# Pontifícia Universidade Católica do Rio Grande do Sul Faculdade de Informática Programa de Pós-Graduação em Ciência da Computação

# MODELAGEM ABSTRATA PARA O HARDWARE DE MPSOCS

# **CARLOS ALBERTO PETRY**

Dissertação apresentada como requisito parcial à obtenção do grau de Mestre em Ciência da Computação na Pontifícia Universidade Católica do Rio Grande do Sul.

Orientador Prof. Dr. Ney Laert Vilar Calazans

Porto Alegre 2009

# Dados Internacionais de Catalogação na Publicação (CIP)

P498m Petry, Carlos Alberto

Modelagem abstrata para o hardware de MPSoCS / Carlos Alberto Petry. – Porto Alegre, 2009. 113 p.

Diss. (Mestrado) – Fac. de Informática, PUCRS Orientador: Prof. Dr. Ney Laert Vilar Calazans

1. Informática. 2. Multiprocessamento. 3. Modelagem de Sistemas. I. Calazans, Ney Laert Vilar. II. Título.

CDD 004.35

Ficha Catalográfica elaborada pelo Setor de Tratamento da Informação da BC-PUCRS

#### Pontifícia Universidade Católica do Rio Grande do Sul FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

# TERMO DE APRESENTAÇÃO DE DISSERTAÇÃO DE MESTRADO

Dissertação intitulada "Modelagem Abstrata para o Hardware de MPSoCS", apresentada por Carlos Alberto Petry, como parte dos requisitos para obtenção do grau de Mestre em Ciência da Computação, Sistemas Embarcados e Sistemas Digitais, aprovada em 16/01/09 pela Comissão Examinadora: PPGCC/PUCRS Prof. Dr. Ney Laert Vilar Calazans-Orientador PPGCC/PUCRS Prof. Dr. Fernando Gehm Moraes -UNB Prof. Dr. Ricardo Pezzuol Jacobi -Homologada em. 15./12...p.q...., conforme Ata No. 22.loq. pela Comissão Coordenadora.

Prof. Dr. Fernando Gehm Moraes Coordenador.

**PUCRS**

**Campus Central**

Av. Ipiranga, 6681 – P32 – sala 507 – CEP: 90619-900 Fone: (51) 3320-3611 – Fax (51) 3320-3621

E-mail: ppgcc@pucrs.br www.pucrs.br/facin/pos

#### **AGRADECIMENTOS**

Meu primeiro agradecimento é, com toda a certeza, ao divino Pai Eterno, Aquele que tudo provê e minha vida conduz.

Em segundo lugar quero agradecer à minha família. À minha esposa pela paciência, pelo estímulo e pelas palavras carinhosas que sempre recebi. Aos meus filhos, por acreditarem e apoiarem meus sonhos, mesmo que isto tenha implicado, em muitas ocasiões, minha ausência em momentos de alegria, de tristeza e de necessidade.

Agradeço também à minha família ascendente. À minha Mãe pela pessoa santa que é por dedicar toda a sua vida em prol de sua família, em especial a mim. Ao meu Pai, em memória, pelos exemplos de vida que me deixou. Aos meus irmãos José Alfredo, Ademar e Gelson, pelos grandes companheiros que tenho. E por fim à minha tia Lita por tantas orações que a mim dedicou.

Agradeço às pessoas que em mim acreditaram quando nesta jornada decidi trilhar. Aos professores Luiz Alberto Steglich e Jair Cordeiro, pelos grandes ensinamentos e confiança que em mim sempre tiveram.

Aos professores do curso de pós-graduação desta instituição, agradeço pela dedicação e empenho em ensinar, sem a ninguém preterir destaco os professores Avelino, Moraes, Hessel e ao meu orientador Ney. Aos grandes colegas de curso, amigos que aqui fiz, desejo grande sucesso. Em especial gostaria de destacar quatro: Edson, pela constância, disponibilidade e presteza em me auxiliar em tantos momentos; Ost, pelo apoio e muitos momentos de alegria; Rafael, embora há tão pouco nos conheçamos pelo sincero amigo que és; Flaviano, pelos muitos momentos de alegria e ansiedade que compartilhamos no convívio deste curso. E não poderia deixar de citar, aos funcionários desta entidade, pela presteza e dedicação que sempre tiveram em suas atividades. A todos vocês um forte abraço e muito sucesso.

Por fim, gostaria de agradecer a qualquer pessoa que tenha esquecido de fazer a justa menção.

# MODELAGEM ABSTRATA PARA HARDWARE DE MPSOC

#### **RESUMO**

A grande quantidade de funcionalidades integradas aos equipamentos digitais atuais, como telefones celulares, handhelds, consoles de jogos e smart phones, vem criando diversos desafios a serem superados pelos projetistas destes sistemas. Entre estes desafios pode-se citar o aumento do desempenho e a flexibilidade, a diminuição da potência consumida e a redução de custos. As atuais tendências para desenvolvimento de sistemas complexos apontam para o uso de sistemas multiprocessados integrados em um único chip (do inglês, Multiprocessor Systems-on-Chip - MPSoCs). MPSoCs são considerados uma solução apropriada para a realização de sistemas eletrônicos digitais de alta complexidade. A alta capacidade de computação paralela sozinha justifica tal afirmativa. Para utilizar eficientemente o grande número de recursos existentes em MPSoCs se faz necessária a exploração do espaço de projeto em alto nível de abstração, de forma a avaliar diferentes alternativas de implementação em tempo adequado de desenvolvimento. Diversos são os esforços realizados tanto pela academia quanto pela indústria para superar os desafios inerentes ao desenvolvimento de tais sistemas. Entre as propostas consideradas para superar os desafios a maioria capitaliza no uso de duas técnicas: o aumento do reuso de módulos IP e o aumento do nível de abstração em que se faz a captura inicial do projeto. O uso de MPSoCs é uma forma natural de aumentar o reuso de hardware e software. O presente trabalho aborda a modelagem de MPSoCs endereçando a segunda destas técnicas: aumento de abstração na captura do projeto do sistema. Disponibiliza-se um modelo funcional em alto nível de abstração do hardware do sistema multiprocessado HeMPS, desenvolvido no ambiente comercial System Studio da empresa Synopsys. A modelagem abstrata proposta propicia acelerar o tempo de simulação do sistema e permite flexibilidade aumentada na exploração do espaço de projeto de aplicações sobre o sistema HeMPS. O modelo gerado inclui múltiplas instâncias de um processador RISC, o Plasma, e uma rede de comunicação intrachip, HERMES, e módulos de hardware acessórios. O processador é modelado a partir de um simulador do conjunto de instruções, e a rede é descrita no nível de abstração de transação. A modelagem inclui também parte de um núcleo de sistema operacional multitarefa executando sobre os processadores do sistema HeMPS. Resultados iniciais mostram um ganho de até três ordens de magnitude em termos de tempo de simulação, para o processador do sistema, quando comparado à simulação RTL deste.

Palavras Chave: Modelagem abstrata, MPSoC, multiprocessamento, multitarefa, NoC.

#### ABSTRACT MODELING FOR MPSOC HARDWARE

#### **ABSTRACT**

The large amount of functionality integrated in current digital devices such as cell phones, handheld computers, game consoles and smart phones is bringing up several design challenges. Among these challenges, it is possible to cite increase performance and flexibility, reduce power consumption and reduce cost. The current trends in the development of such complex systems point to the use of Multiprocessor Systems-on-Chip (MPSoCs). MPSoCs area considered today as an appropriate solution for the realization of highly complex digital electronic systems. Their high capacity for parallel processing alone justifies this statement. To employ the large amount of resources provided by MPSoCs efficiently, it is necessary to explore the application design space at high levels of abstraction. This is important to assess many different implementation alternatives in a timely fashion. Several efforts are under way both in industry and in the academy to overcome the mentioned challenges to develop such systems. Among the propositions available, several, if not all, plead the use of two techniques: the increase of design reuse and the increase of the abstraction level in which designs are captured. The use of MPSoCs is a natural way to provide hardware and software reuse. The present work addresses the use of MPSoCs and focus on using the second technique. It provides a highly abstract functional model of the hardware for an MPSoC called HeMPS. The abstract modeling employed the commercial environment System Studio of Synopsys. The proposed abstract modeling process enables accelerating the system simulation time and increases the system description flexibility to support design space exploration for applications running on the HeMPS system. HeMPS includes multiple instances of an open source RISC processor called Plasma, an intrachip communication network called HERMES, and some accessory hardware modules. The processor is modeled from its instruction set simulator and the network is described at the transaction abstraction level. The modeling also includes part of a multitask operating system microkernel that executes on HeMPS processors. Initial results for the processor system only display simulation time gains that are up to three orders of magnitude faster than the Plasma RTL model simulation.

Keywords: MPSoC, multiprocessing, multitask, NoC, high abstraction level.

# LISTA DE FIGURAS

| Figura 1 – 1 | Modelo conceitual usado como base para este trabalho composto de: elementos de processamento (Plasma-IP), a infra-estrutura de comunicação (NoC HERMES) e como componentes de software: sistema                                                                                                                                                            |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | operacional executado em cada Plasma-IP e tarefas contidas inicialmente no Repositório de Tarefas 23                                                                                                                                                                                                                                                       |

|              | Fluxo de projeto proposto por Nikolov et al. [NIK08]                                                                                                                                                                                                                                                                                                       |

| _            | Fluxo de projeto SCE [DÖM08].                                                                                                                                                                                                                                                                                                                              |

|              | Componentes de hardware básicos do sistema HeMPS: elementos de processamento, roteadores e canais de comunicação                                                                                                                                                                                                                                           |

| Figura 5 – 1 | Diagrama de blocos do Plasma, mostrando seus quatro módulos principais e sua interconexão [WOS07]34                                                                                                                                                                                                                                                        |

| _            | Detalhamento do caminho de dados do módulo Plasma no sistema HeMPS                                                                                                                                                                                                                                                                                         |

| Figura 7 – 1 | Estrutura em níveis no microkernel da plataforma HeMPS                                                                                                                                                                                                                                                                                                     |

| Figura 8 – 1 | Uma instância de uma NoC HERMES 3x3. Retângulos numerados representam os roteadores existentes e os valores identificam sua posição na rede, segundo a distribuição cartesiana XY. Assim, 21 indica o roteador localizado na terceira coluna (abscissas) e segunda linha (ordenadas). Os retângulos N representam os núcleos IP conectados a cada roteador |

| Figura 9 – 1 | Estrutura básica do roteador [MOR04]37                                                                                                                                                                                                                                                                                                                     |

| Figura 10 –  | - Janela inicial do ambiente ATLAS                                                                                                                                                                                                                                                                                                                         |

| Figura 11 –  | - Estrutura interna do roteador para a rede HERMES TL [MOR04a]                                                                                                                                                                                                                                                                                             |

| Figura 12 –  | - Diagrama de blocos típico de um pipeline para processador MIPS usando ISA MIPS-I47                                                                                                                                                                                                                                                                       |

| Figura 13 –  | - Diagrama de blocos do processador MLite do projeto PLASMA [RHO07]49                                                                                                                                                                                                                                                                                      |

| Figura 14 –  | - Fluxo de projeto algorítmico no ambiente System Studio: entradas, saídas e estrutura interna [SYN06]51                                                                                                                                                                                                                                                   |

| Figura 15 –  | - Projeto arquitetural no ambiente System Studio: entradas, saídas e fluxo interno [SYN06]52                                                                                                                                                                                                                                                               |

| Figura 16 –  | - Interface gráfica do ambiente System Studio [SYN06], mostrando as áreas de trabalho principais da ferramenta                                                                                                                                                                                                                                             |

| Figura 17 –  | - Módulo do processador MLite criado no ambiente System Studio: representação do processador e de sua interface. O retângulo chanfrado representa a instância do módulo e os quadrados com seta os dois canais FIFO para comunicação de entrada e saída                                                                                                    |

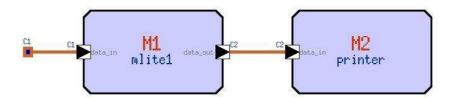

| Figura 18 –  | - Módulos MLite e RAM interconectados através de portas e canais de comunicação através de um canal hierárquico                                                                                                                                                                                                                                            |

| Figura 19 –  | Representação esquemática do roteador HERMES: componente usado para transferência de dados entre nodos da rede ou núcleos IP                                                                                                                                                                                                                               |

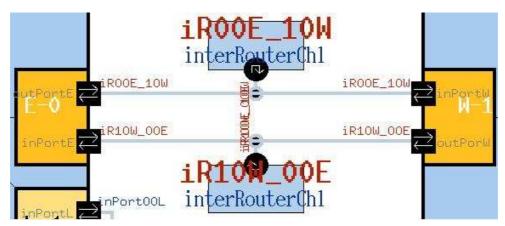

| Figura 20 –  | - Instância do módulo IntraRouterChl. Mostra-se o canal de comunicação interno entre portas de comunicação do roteador HERMES                                                                                                                                                                                                                              |

| Figura 21 –  | Representação esquemática do módulo door, usado para dar suporte ao fluxo de comunicação de dados em um roteador HERMES                                                                                                                                                                                                                                    |

| Figura 22 –  | - Portas primitivas de entrada (a) e saída (b)                                                                                                                                                                                                                                                                                                             |

| Figura 23 –  | - Módulo interRouterChl, um canal hierárquico de interconexão entre roteadores e entre roteador e núcleo IP.                                                                                                                                                                                                                                               |

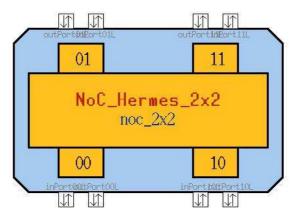

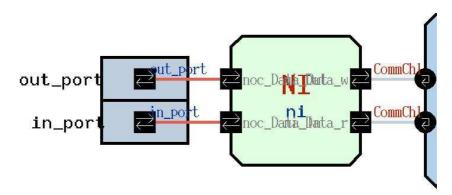

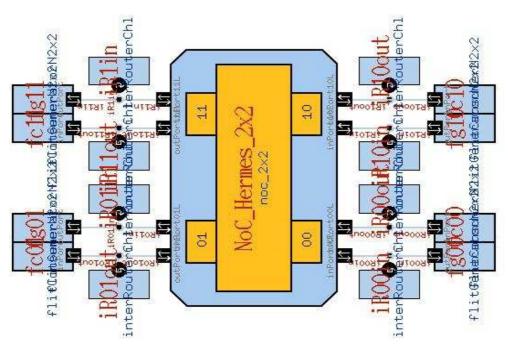

| Figura 24 –  | Rede intrachip HERMES com dimensão 2x2, instanciada em um módulo hierárquico que representa uma rede intra-chip HERMES 2x2                                                                                                                                                                                                                                 |

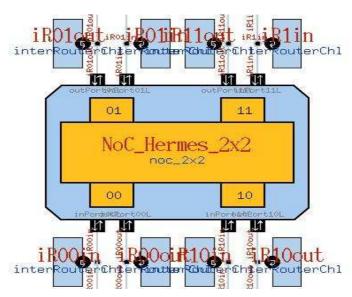

| Figura 25 –  | - Representação esquemática de uma rede HERMES 2x2, módulo hierárquico noc_2x271                                                                                                                                                                                                                                                                           |

| Figura 26 –  | - Módulo noc_2x2, rede HERMES 2x2 juntamente com os canis hierárquicos que permitem conectar a rede aos núcleos IP locais                                                                                                                                                                                                                                  |

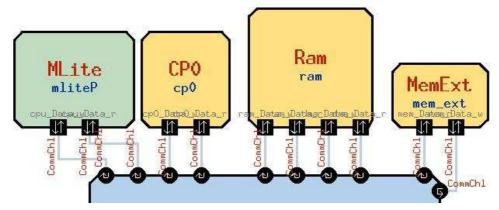

| Figura 27 –  | - Modelo Plasma, contendo o processador MLite e seus três dispositivos de armazenamento, interconectados por um canal hierárquico                                                                                                                                                                                                                          |

| Figura 28 –  | - Visão parcial do modelo do Plasma apresentando a interface externa dos três dispositivos relacionados à comunicação                                                                                                                                                                                                                                      |

| Figura 29 –  | - Módulo UART: usado para envio de mensagens recebidas pelo processador mestre para o console 82                                                                                                                                                                                                                                                           |

| _            | - Módulo de acesso direto à memória (DMA): usado na alocação de tarefas                                                                                                                                                                                                                                                                                    |

| •            | - Protocolo de comunicação usado pelos serviços do microkernel HeMPS, transportados por mensagens na rede. Aqui M corresponde ao processador mestre, S corresponde a algum dos processadores escravos 87                                                                                                                                                   |

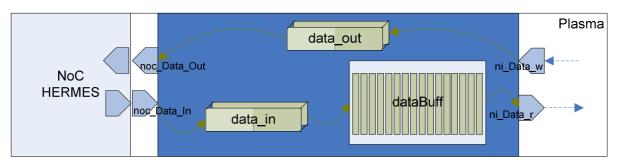

| Figura 32 – Componentes da estrutura usada no mecanismo de envio e recebimento de dados através do módulo cinterface de rede (NI).                                                                                                 |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figura 33 – Estrutura, declaração e forma de leitura relativas à variável data_in, considerando o recebimento de d provindos da rede                                                                                               |     |

| Figura 34 – Módulo de interface de rede (NI).                                                                                                                                                                                      | 90  |

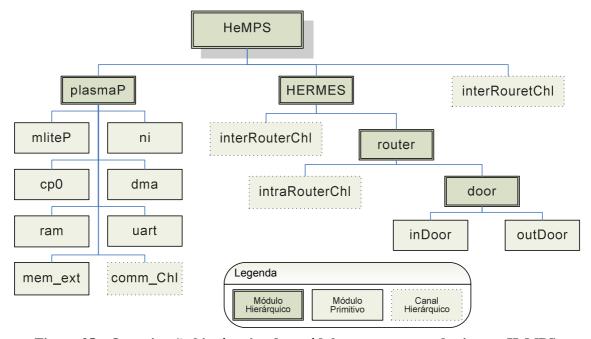

| Figura 35 – Organização hierárquica dos módulos componentes do sistema HeMPS.                                                                                                                                                      | 91  |

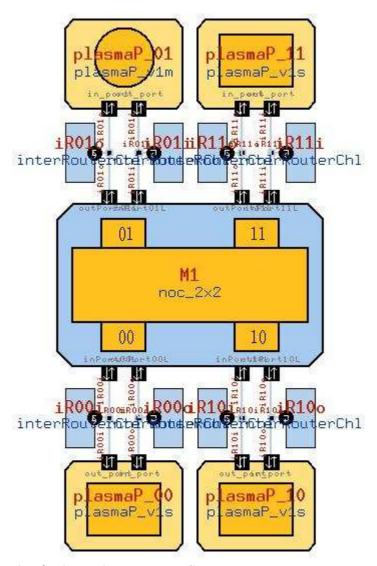

| Figura 36 – Uma instância do sistema HeMPS, contendo uma rede HERMES 2x2 e quatro processadores Plasma.                                                                                                                            | 92  |

| Figura 37 – Cenário de simulação utilizado para validar o módulo MLite no ambiente System Studio                                                                                                                                   | 96  |

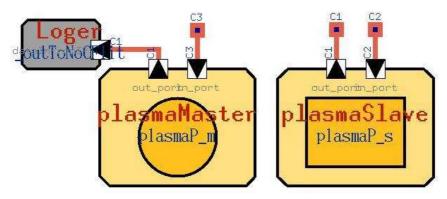

| Figura 38 – Cenário de validação da comunicação entre dois processadores MLite                                                                                                                                                     | 96  |

| Figura 39 – Rede HERMES 2x2 instanciada junto com quatro pares de módulos produtor/consumidor                                                                                                                                      | 97  |

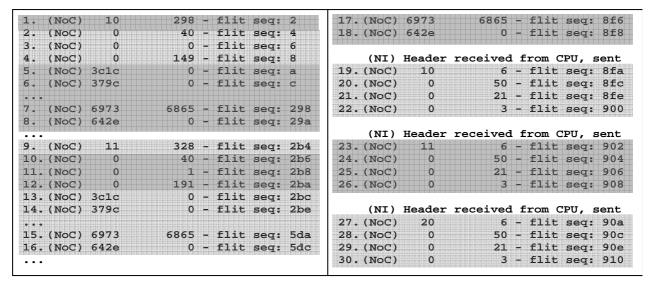

| Figura 40 – Saída gerada na primeira parte da simulação do módulo Plasma mestre: carga na memória externa (MEXT) das quatro tarefas da aplicação selecionada e carga do microkernel na memória principal (RAN                      |     |

| Figura 41 – Fluxo de dados gerado pela execução da operação 7 da Tabela 9                                                                                                                                                          | 101 |

| Figura 42 – Parte da saída gerada pela execução da operação 8 da Tabela 9.                                                                                                                                                         | 101 |

| Figura 43 – Saída gerada pelo procedimento inicial executado pela simulação do processador escravo: carga do microkernel.                                                                                                          | 104 |

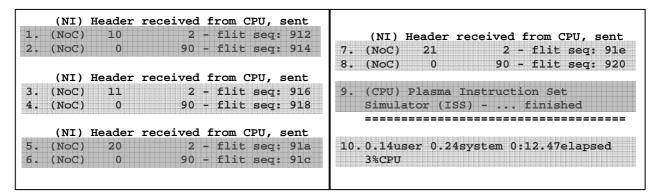

| Figura 44 – Módulos Plasma mestre e escravo, usados na primeira fase de validação                                                                                                                                                  | 105 |

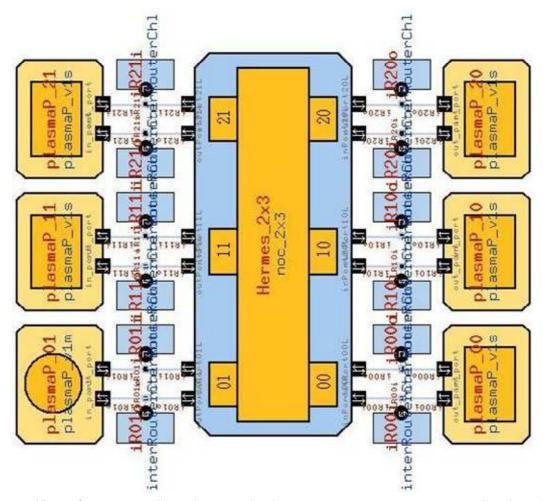

| Figura 45 – Módulo HeMPS de dimensão 2 x 3 composto de uma rede HERMES 2x3 e seis processadores Plasm mestre e cinco escravos.                                                                                                     |     |

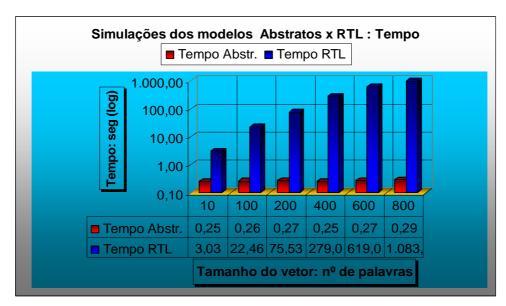

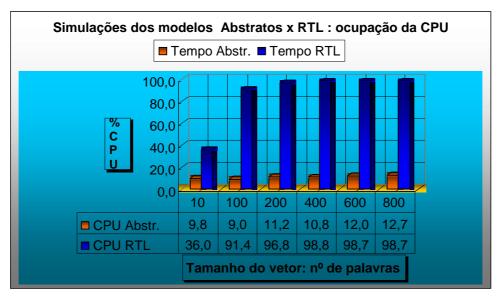

| Figura 46 – Comparação de tempos de simulação entre um modelo abstrato do Plasma baseado em ISS e um mod<br>RTL. Simulação abstrata realizada no ambiente System Studio, e simulação RTL realizada no ambiente Modelsim da Mentor. | nte |

| Figura 47 – Comparação ocupação de CPU entre um modelo abstrato do Plasma baseado em ISS e um modelo R' Simulação abstrata realizada no ambiente System Studio, e simulação RTL realizada no ambiente Modelsim da Mentor.          |     |

# **LISTA DE TABELAS**

| Tabela 2 – Divisão das instruções MIPS quanto ao seu formato                                                                                                                                                                                                   | Tabela 1 – Seqüência de envio de flits na rede HERMES. O primeiro flit contém o endereço de destino (target); o<br>segundo carrega o tamanho da área de dados (size); a partir do terceiro flit são enviados os dados (paylo | ad).    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Tabela 3 – Descrição das convenções de uso dos registradores de propósito geral do MIPS                                                                                                                                                                        |                                                                                                                                                                                                                              | 38      |

| Tabela 4 – Distribuição dos registradores de propósito geral                                                                                                                                                                                                   | Tabela 2 – Divisão das instruções MIPS quanto ao seu formato.                                                                                                                                                                | 44      |

| Tabela 5 – Parâmetros usados para configurar cada instância do módulo roteador HERMES                                                                                                                                                                          | Tabela 3 – Descrição das convenções de uso dos registradores de propósito geral do MIPS                                                                                                                                      | 46      |

| Tabela 6 – Organização do repositório de tarefas. O valor "m" representa "n° de tarefas*12" (3*4: três campos de 4 bytes) e "t" o tamanho total do código de todas as tarefas menos 1, em bytes                                                                | Tabela 4 – Distribuição dos registradores de propósito geral                                                                                                                                                                 | 46      |

| bytes) e "t" o tamanho total do código de todas as tarefas menos 1, em bytes                                                                                                                                                                                   | Tabela 5 – Parâmetros usados para configurar cada instância do módulo roteador HERMES                                                                                                                                        | 72      |

| processador. Gerado significa o local onde é gerado um pacote daquele serviço. Tratado identifica onde o pacote é recebido e tratado. Cód é o código numérico hexadecimal do serviço. Função é o nome da rotina que processa o pacote                          |                                                                                                                                                                                                                              | 78      |

| Tabela 8 – Parâmetros e configuração padrão para os módulos plasmaP e seus submódulos                                                                                                                                                                          | processador. Gerado significa o local onde é gerado um pacote daquele serviço. Tratado identifica onde pacote é recebido e tratado. Cód é o código numérico hexadecimal do serviço. Função é o nome da rotin                 | o<br>na |

| Tabela 9 – Lista de tarefas da fase inicial do microkernel mestre.99Tabela 10 – Descrição do conteúdo dos dados enviados à NoC pela operação 7 da Tabela 9.102Tabela 11 – Descrição do conteúdo de dados enviados para a NoC para a operação 8 da Tabela 9.102 |                                                                                                                                                                                                                              |         |

| Tabela 10 – Descrição do conteúdo dos dados enviados à NoC pela operação 7 da Tabela 9                                                                                                                                                                         |                                                                                                                                                                                                                              |         |

| Tabela 11 – Descrição do conteúdo de dados enviados para a NoC para a operação 8 da Tabela 9                                                                                                                                                                   | Tabela 9 – Lista de tarefas da fase inicial do microkernel mestre.                                                                                                                                                           | 99      |

|                                                                                                                                                                                                                                                                | Tabela 10 – Descrição do conteúdo dos dados enviados à NoC pela operação 7 da Tabela 9                                                                                                                                       | 102     |

| Tabela 12 – Lista de operações referente à execução do processo inicial do microkernel escravo                                                                                                                                                                 | Tabela 11 – Descrição do conteúdo de dados enviados para a NoC para a operação 8 da Tabela 9                                                                                                                                 | 102     |

|                                                                                                                                                                                                                                                                | Tabela 12 – Lista de operações referente à execução do processo inicial do microkernel escravo.                                                                                                                              | 103     |

#### LISTA DE SIGLAS

ASIC Application Specific Integrated Circuit

ASE Application Specific Extension CCSS CoCentric System Studio

CF Control Flow

CFG Control Flow Graph

CPU Central Processing Unit

DF Data Flow

DFG Data Flow Graph

DMA Direct Memory Access

DS Diagrama de Seqüência

DSL Digital Subscriber Line

DSP Digital Signal Processor

FIFO First In First Out

FPGA Field Programmable Gate Array

FPU Floating Point Unit FSM Finite State Machine

HeMPS HERMES Multi Processor System

IP Intellectual Property

ISA Instruction Set Architecture ISS Instruction Set Simulator

MIPS Microprocessor without Interlocked Pipeline Stages

MMU Management Memory Unit MoC Model of Computation

MPSoC Multi Processor System on Chip

MP Master Processor

NAT Network Address Translation

NI Network Interface NoC Network on Chip

NORMA No Remote Memory Access

OSI Open System Interconnect

PAT Payload Abstraction Technique

PC Program Counter

PDA Personal Digital Assistant RAM Random Access Memory

RISC Reduced Instruction Set Computer

RTL Register Transfer Level

SCE System-on-Chip Environment

SL Slave Processor

SLD System Level Design

SoC System-on-Chip

TA Transaction Accurate

TCB Task Control Block

TL Transaction Level

TLB Translation Lookaside Buffer TLM Transaction Level Model

UART Universal Asynchronous Receiver-Transmitter

UML Unified Modeling Language

VA Virtual Architecture

VHDL VHSIC Hardware Description Language VHSIC Very High Speed Integrated Circuit

# SUMÁRIO

| 1 | 5                                                                              |    |

|---|--------------------------------------------------------------------------------|----|

|   | 1.1 MOTIVAÇÃO                                                                  | 22 |

|   | 1.2 MODELO CONCEITUAL                                                          | 23 |

|   | 1.3 Objetivos                                                                  | 23 |

|   | 1.4 ORGANIZAÇÃO DO DOCUMENTO                                                   | 24 |

|   |                                                                                |    |

| 2 | ESTADO DA ARTE                                                                 | 27 |

|   | 2.1 REVISÃO DE TRABALHOS PRÉVIOS                                               | 27 |

|   | 2.1.1 Modelagem baseada em C/C++/SystemC                                       | 27 |

|   | 2.1.2 Modelagem de MPSoCs com Simulink                                         | 30 |

|   | 2.1.3 Modelagem de MPSoCs baseada em Java e UML                                |    |

|   | 2.1.4 Modelagem de MPSoCs baseada em SpecC                                     |    |

| _ |                                                                                | •  |

| 3 |                                                                                |    |

|   | 3.1 SISTEMA MULTIPROCESSADO HEMPS                                              |    |

|   | 3.1.1 Componentes de hardware                                                  |    |

|   | 3.1.2 Componentes de software                                                  |    |

|   | 3.2 INFRA-ESTRUTURA DE COMUNICAÇÃO INTRACHIP HERMES                            |    |

|   | 3.2.1 Conceitos básicos                                                        |    |

|   | 3.2.2 Modelo RTL sintetizável                                                  |    |

|   | 3.2.3 Modelo abstrato simulável                                                |    |

|   | 3.3 ARQUITETURA MIPS-I DE PROCESSADORES DE PROPÓSITO GERAL                     |    |

|   | 3.3.1 A arquitetura MIPS-I                                                     | 40 |

|   | 3.3.1.1 Ârquitetura do conjunto de instruções MIPS                             |    |

|   | 3.3.1.2 Características da arquitetura de processadores baseados na ISA MIPS-I |    |

|   | 3.3.2 Implementação do processador Plasma                                      |    |

|   | 3.4 SYNOPSYS SYSTEM STUDIO – FERRAMENTA DE MODELAGEM DE SISTEMAS               | 49 |

|   | 3.4.1 Introdução                                                               | 49 |

|   | 3.4.2 Projeto algorítmico                                                      | 50 |

|   | 3.4.3 Projeto arquitetural                                                     | 51 |

|   | 3.4.4 Interface gráfica do ambiente System Studio                              | 53 |

| 4 | MODEL A CEM DO CURCICIENA DI ACMA                                              |    |

| 4 | MODELAGEM DO SUBSISTEMA PLASMA                                                 |    |

|   | 4.1 CARACTERÍSTICAS DO SIMULADOR PLASMA (PROJETO OPENCORES)                    |    |

|   | 4.2 INTEGRAÇÃO E MODELAGEM DO PROCESSADOR PLASMA                               |    |

|   | 4.2.1 Integração e modelagem: Etapa 1                                          |    |

|   | 4.2.2 Integração e validação: Etapa 2                                          | 61 |

| 5 | MODELAGEM DA REDE INTRACHIP HERMES                                             | 65 |

|   | 5.1 Introdução                                                                 |    |

|   | 5.2 MODELAGEM HIERÁRQUICA DOS MÓDULOS DA HERMES                                |    |

|   | 5.2.1 O roteador (router)                                                      | 65 |

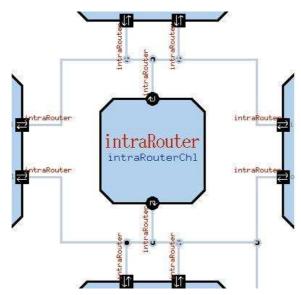

|   | 5.2.2 Módulo intraRouterChl                                                    |    |

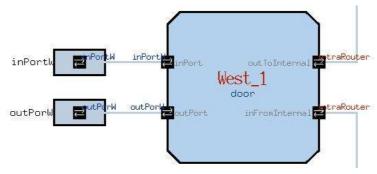

|   | 5.2.3 Módulo door                                                              |    |

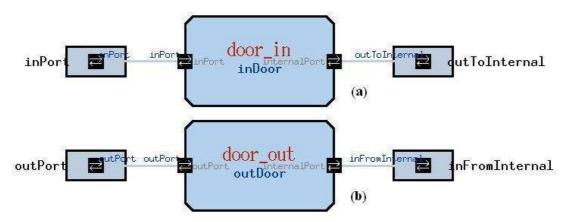

|   | 5.2.4 Módulos inDoor e outDoor                                                 |    |

|   | 5.2.5 Módulo interRouterChl                                                    |    |

|   | 5.2.6 Modelo da rede HERMES                                                    |    |

|   |                                                                                |    |

| 6 | MODEL ACEM DO SISTEMA MIJI TIPROCESSADO HEMPS                                  | 73 |

|    | 6.1 COMPONENTES DE SOFTWARE                                 | 73  |

|----|-------------------------------------------------------------|-----|

|    | 6.1.1 O microkernel HeMPS                                   | 73  |

|    | 6.1.1.1 Microkernel mestre                                  | 74  |

|    | 6.1.1.2 Microkernel escravo                                 | 75  |

|    | 6.1.2 Aplicações                                            |     |

|    | 6.2 COMPONENTES DE HARDWARE COMPLEMENTARES AO MÓDULO PLASMA | 77  |

|    | 6.2.1 Módulos complementares: MEM_EXT e CP0                 | 77  |

|    | 6.2.1.1 Módulo MEM_EXT: o repositório                       | 78  |

|    | 6.2.1.2 Módulo CP0: co-processador 0                        |     |

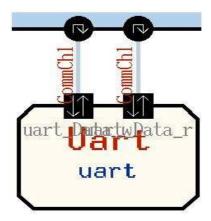

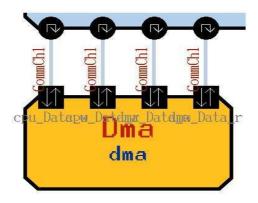

|    | 6.2.2 Módulos complementares: UART, DMA e NI                | 81  |

|    | 6.2.2.1 Módulo UART                                         | 81  |

|    | 6.2.2.2 Módulo DMA                                          | 82  |

|    | 6.2.2.3 Módulo NI                                           |     |

|    | 6.2.3 O modelo completo do sistema multiprocessado HeMPS    | 91  |

| 7  | VALIDAÇÃO E RESULTADOS                                      |     |

|    | 7.1 INTRODUÇÃO                                              |     |

|    | 7.2 VALIDAÇÃO DO MÓDULO PLASMA                              |     |

|    | 7.2.1 Módulo MLite                                          |     |

|    | 7.2.2 Módulo de memória                                     |     |

|    | 7.3 VALIDAÇÃO DA INFRA-ESTRUTURA DE COMUNICAÇÃO HERMES      |     |

|    | 7.4 VALIDAÇÃO DO SISTEMA MULTIPROCESSADO HEMPS              |     |

|    | 7.4.1 Validação do módulo HeMPS: primeira etapa             |     |

|    | 7.4.2 Validação do módulo HeMPS: segunda etapa              | 105 |

|    | 7.5 RESULTADOS QUANTITATIVOS PRELIMINARES                   | 106 |

|    |                                                             |     |

| 8  | CONCLUSÕES                                                  | 109 |

|    | 8.1 CONCLUSÕES E CONTRIBUIÇÕES                              | 109 |

|    | 8.2 Trabalhos futuros                                       |     |

|    |                                                             |     |

| DI | EFERÊNCIAS BIBLIOGRÁFICAS                                   | 111 |

| ĸI | LFLKENUIA5 DIDLIUGKAFIUA5                                   | 111 |

# 1 Introdução

Com o desenvolvimento da tecnologia, sobretudo a digital, uma vasta quantidade e variedade de sistemas tecnológicos têm invadido nosso cotidiano. Muitos equipamentos fazem uso de alta tecnologia como meio de viabilizar o seu funcionamento. As funcionalidades oferecidas pelos equipamentos digitais vêm evoluindo rapidamente. Um claro exemplo é o telefone celular, cuja principal característica, permitir a realização de chamadas telefônicas de forma móvel, alia-se a outros recursos incorporados ao aparelho, como agenda e calculadora, acesso à Internet, etc., tornando-se cada vez mais partes essenciais deste tipo de telefone.

A grande quantidade de funcionalidades integradas a equipamentos digitais atuais gera constantes desafios a serem superados pelos projetistas. Entre os vários desafios que se apresentam como críticos ao projetar novos sistemas, cinco são freqüentemente destacados [ANG06] [HEN03] [KOG02] [MAA08] [POP07] [TIB07]:

- Gerenciar o aumento do desempenho e flexibilidade;

- Manter a confiabilidade do sistema;

- Aperfeiçoar o uso da área de silício;

- Gerenciar a crescente complexidade de projeto;

- Evitar o aumento ou, se possível, reduzir o tempo necessário para projeto e verificação do sistema visando:

- o reduzir os custos de projeto e implementação;

- atender à crescente exigência pela redução do tempo de chegada do produto ao mercado (do inglês time-to-market).

O acréscimo de complexidade tipicamente aumenta a demanda de tempo para o desenvolvimento de novos produtos. Por outro lado, as pressões de mercado estão forçando a diminuição deste tempo para dispositivos mais complexos, atingindo-se o conhecido problema da lacuna de produtividade em projeto (do inglês design productivity gap). A lacuna de produtividade ocorre devido à exigência de aumento da capacidade de produção não acompanhada pela capacidade de projetistas em aproveitar os recursos das tecnologias frente ao avanço destas, a qual imprime circuitos integrados cada vez mais densos.

Duas maneiras fundamentais para atender os desafios citados são o aumento da reutilização maciça de hardware e software de componentes, durante o projeto de sistemas embarcados complexos, e uso de sistemas multiprocessados em um único chip (MPSoC) [JER05]. MPSoCs têm sido crescentemente considerados como a solução mais apropriada para a realização de sistemas eletrônicos digitais de alta complexidade. Porém, para que estes sistemas sejam viáveis precisam ser projetados, simulados e

verificados, devendo operar conforme a sua especificação de requisitos [JER05].

Atualmente, o paradigma de projeto mais empregado baseia-se na captura de descrições de sistemas no nível de abstração de transferência entre registradores (do inglês, Register Transfer Level ou RTL). Entretanto, o projeto partindo de descrições RTL não oferece suporte adequado para o desenvolvimento de sistemas muito complexos [DON04].

Outra maneira de enfrentar os desafios citados anteriormente vem sendo proposta tanto na indústria quanto na academia, como forma de dar suporte à superação dos desafios existentes. Basicamente esta maneira pode ser resumida conforme afirmam Cai e Gajski [CAI03]: o nível de abstração deve ser elevado acima do RTL como forma de manter a produtividade no desenvolvimento de projetos e tratar a crescente complexidade de SoCs e MPSoCs, levando a ganhos de produtividade de várias ordens de grandeza, em termos, por exemplo, de tempo de simulação.

O presente trabalho aborda a modelagem abstrata de MPSoCs como forma de aumentar o desempenho do processo de validação por simulação de sistemas multiprocessados. Isto é obtido utilizando-se de um nível de abstração localizado acima do RTL, aplicado a cada componente modelado do MPSoC. O processo de modelagem abstrata é restrito aqui sobre tudo ao hardware de um MPSoC específico, denominado HeMPS [WOS07]. Outra restrição imposta ao trabalho é o uso de uma ferramenta de modelagem comercial específica, o ambiente System Studio da Synopsys [SYN08]. A justificativa para uso deste ambiente de desenvolvimento se dá pela sua disponibilidade e relativa facilidade para realizar a captura e modelagem abstrata dos componentes considerados fazendo uso da linguagem SystemC.

## 1.1 Motivação

Entre as motivações do presente trabalho destaca-se:

- a importância de MPSoCs para sistemas eletrônicos digitais atuais, incluindo arquiteturas com centenas de componentes [HEN03] interconectados através de uma infra-estrutura de comunicação, como por exemplo, NoCs;

- o uso de modelos desenvolvidos em níveis de abstração superiores ao RTL largamente propostos na atualidade, a fim de permitir vencer os desafios impostos pelo projeto de equipamentos digitais atualmente em desenvolvimento ou que serão desenvolvidos no futuro próximo.

O presente trabalho tem por principal objetivo disponibilizar uma descrição executável contendo módulos compatíveis com o hardware do sistema HeMPS, descritos em níveis de abstração mais elevados que o RTL. A descrição executável resultante deste trabalho tem como fim ser um modelo que permite o desenvolvimento e teste de software escrito para a arquitetura HeMPS de forma mais eficiente.

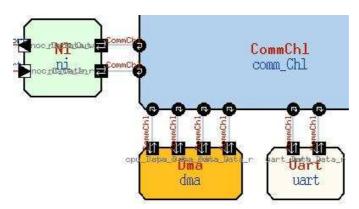

#### 1.2 Modelo conceitual

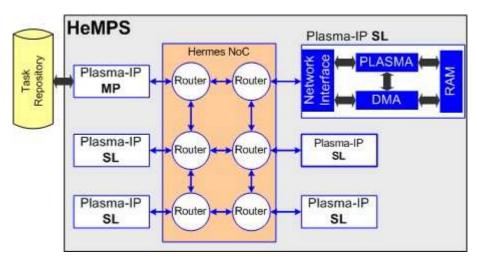

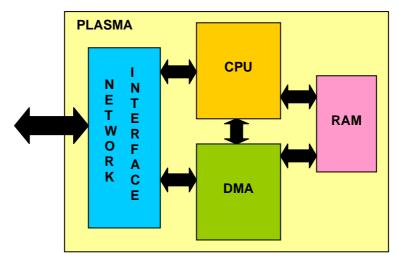

A Figura 1 apresenta o modelo conceitual utilizado como base para este trabalho. Ela mostra o diagrama de blocos do sistema HeMPS, um MPSoC composto de elementos homogêneos de processamento, infra-estrutura de interconexão baseada em uma NoC e um repositório de tarefas contendo aplicações que são distribuídas pelo processador mestre (MP) aos processadores escravos (SL). O elemento de processamento do sistema HeMPS, Plasma-IP SL, por sua vez, inclui um processador, uma memória local, um controlador de acesso direto a memória e uma interface com a NoC.

O software aqui considerado pode ser definido em duas classes: (i) o sistema operacional executado em cada processador, microkernel, e (ii) o conjunto de tarefas a serem executas de forma distribuída nos processadores escravos, contidas inicialmente no Repositório de Tarefas. Conforme já mencionado, o objetivo deste trabalho prioriza a modelagem do hardware do sistema HeMPS. Entretanto, com o intuito de gerar um modelo capaz de executar ao menos parte do microkernel, os módulos produzidos foram validados através do uso do próprio software do sistema.

Figura 1 – Modelo conceitual usado como base para este trabalho composto de: elementos de processamento (Plasma-IP), a infra-estrutura de comunicação (NoC HERMES) e como componentes de software: sistema operacional executado em cada Plasma-IP e tarefas contidas inicialmente no Repositório de Tarefas.

## 1.3 Objetivos

Esta Seção apresenta os objetivos do presente trabalho. Inicialmente são apresentados os objetivos estratégicos:

- trazer para o grupo de pesquisa do Autor a capacidade de uso de processos eficazes para validação de sistemas complexos em alto nível de abstração;

- 2. dominar um método de modelagem em alto nível de abstração baseado em ferramentas comerciais;

3. disponibilizar um modelo mais abstrato do hardware da plataforma HeMPS.

Para alcançar os objetivos estratégicos, propõem-se os seguintes objetivos específicos:

- modelar uma instância do processador Plasma a partir de um simulador do conjunto de instruções (ISS) do MIPS-I;

- 5. adaptar uma implementação abstrata no nível de transação (em inglês, transaction level, TL) da rede intrachip HERMES [MOR04a] para operar no ambiente comercial selecionado:

- 6. criar um modelo, descrito em alto nível de abstração, do hardware da plataforma HeMPS a partir dos modelos disponibilizados nos objetivos específicos 1 e 2;

- 7. simular o modelo obtido no objetivo específico 3 conjuntamente com aplicações simples de software, a fim de validar o uso do modelo abstrato;

- 8. comparar de forma quantitativa a modelagem realizada com o modelo RTL disponível, do ponto de vista de eficiência de simulação.

# 1.4 Organização do documento

O restante desta dissertação está organizado conforme descrito a seguir.

O Capítulo 2 apresenta o estado da arte em modelagem de sistemas abstratos. São abordados trabalhos que realizam a modelagem tanto de elementos de comunicação como elementos de processamento.

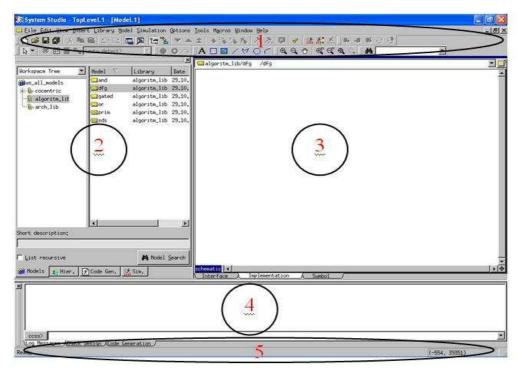

O Capítulo 3 apresenta os trabalhos relacionados a esta dissertação. Nele são abordados dois trabalhos desenvolvidos no grupo de pesquisa do Autor e um trabalho realizado fora deste grupo, salientando as alterações e adições necessárias para compor o sistema de referência no aqui empregado. A parte final desta seção apresenta o ambiente de desenvolvimento System Studio da empresa Synopsys. Esta ferramenta serviu de ambiente base para desenvolver os módulos do modelo abstrato considerado. São apresentados os dois principais formatos usados para modelagem de sistemas e uma introdução às principais características do ambiente gráfico da ferramenta.

A partir do capítulo 4 inicia-se a apresentação do processo de modelagem dos três principais módulos do sistema HeMPS. Neste Capítulo apresenta-se a modelagem do subsistema de processamento (Plasma). O Capítulo introduz as características do ISS, utilizado como base para a modelagem e apresenta as fases de integração e modelagem executadas para gerar o elemento de processamento.

O Capítulo 5 apresenta a modelagem realizada para integrar e disponibilizar uma instância da infra-estrutura de comunicação HERMES. A geração deste módulo teve por

base o modelo no nível de transação (em inglês, transaction level model, TLM) já desenvolvido no grupo do Autor, que necessitou passar por alterações e recebeu acréscimos, a fim de que pudesse ser integrado ao ambiente.

O Capítulo 6 apresenta a modelagem realizada para integrar o modelo abstrato do sistema HeMPS no ambiente System Studio. Foram considerados para esta tarefa os modelos introduzidos nos dois capítulos anteriores.

O Capítulo 7 apresenta o processo de validação dos diversos módulos e os resultados obtidos a partir das simulações executadas. São apresentadas as validações dos módulos desenvolvidos nos capítulos 4 a 6 e os resultados obtidos nas simulações do subsistema Plasma e do sistema HeMPS.

Por fim, o Capítulo 9 apresenta as conclusões do presente trabalho e sugestões de trabalhos futuros.

# 2 ESTADO DA ARTE

Embora muito seja comentado no meio industrial e na academia sobre a modelagem abstrata de sistemas e apesar da disponibilidade de ferramentas comerciais poderosas dando suporte a este tipo de modelagem, não é tarefa simples obter informações sobre fluxos baseados na captura de projeto em alto nível de abstração. Esta Seção apresenta alguns trabalhos encontrados na literatura sobre o tema.

# 2.1 Revisão de trabalhos prévios

# 2.1.1 Modelagem baseada em C/C++/SystemC

Kogel e Bussaglia [KOG02] propõem uma metodologia para realizar a exploração arquitetural de sistemas computacionais descritos em SystemC fazendo uso do ambiente System Studio [SYN08]. O principal objetivo perseguido pelos Autores é definir uma arquitetura de sistema que permita oferecer desempenho, flexibilidade e baixo consumo de potência, e que atenda às especificações de áreas de aplicação tais como comunicação wireless, redes de computadores e processamento de dados multimídia.

Os Autores consideram dois domínios durante o fluxo de projeto: especificação e implementação. Eles propõem também a consideração de um domínio intermediário, denominado nível de sistema (do inglês System Level).

No domínio de especificação, os requisitos são estabelecidos e as funcionalidades necessárias definidas, gerando um documento de especificação do sistema. Inicia-se pelos procedimentos de captura e particionamento das funcionalidades, com o objetivo de gerar o modelo funcional do sistema. O próximo passo é gerar o modelo abstrato da arquitetura a partir do modelo funcional. A fim de permitir a captura das funcionalidades e definir o mapeamento da arquitetura abstrata, estas funcionalidades são particionadas em módulos SystemC. Para imprimir maior rigor metodológico, alguns critérios são usados na definição do mapeamento, incluindo a avaliação da troca de informações entre módulos e a análise de localidade de algoritmos. Como resultado é gerado um modelo mapeado para a arquitetura em um nível de abstração superior ao RTL, porém mais detalhado que a especificação original. O domínio de implementação objetiva elaborar a arquitetura de hardware, conciliando restrições tais como consumo, área do circuito e velocidade. A partir daí segue-se fluxo convencional de desenvolvimento.

Os Autores demonstraram a possibilidade do uso de metodologias de projeto em nível de sistema (em inglês System Level Design ou SLD) no desenvolvimento de SoCs, aplicando-as via uso de ferramentas comerciais, no caso o System Studio. Os resultados finais demonstram a redução de linhas de código escritas e aumento do desempenho da

simulação em cerca de duas ordens de magnitude quando comparado a uma captura a partir de descrição RTL.

Jang et al. [JAN04] apresentam uma metodologia de modelagem de SoCs em alto nível de abstração, que permite projetar, verificar e validar sistemas complexos, além de possibilitar a exploração da arquitetura. O modelo abstrato criado baseou-se em um modelo RTL já implementado e sintetizado, no qual foi detectado baixo desempenho na comunicação. A implementação abstrata foi desenvolvida com precisão próxima ao modelo RTL existente e comparada a última. O desenvolvimento, verificação, validação e posterior exploração da arquitetura foram realizadas através do uso do ambiente System Studio [SYN08]. Módulos de processamento baseados no processador ARM e no barramento AMBA foram providos pela biblioteca DesignWare [SYN08a].

Os projetistas que desenvolveram a versão RTL também implementaram a versão abstrata do sistema. A modelagem se baseou no SoC S3C2510, que corresponde a um microcontrolador de rede para sistemas baseados no padrão Ethernet, desenvolvido pela empresa Samsung, eliminando os módulos não diretamente relacionados à funções de tradução de endereços de rede (em inglês Network Address Translation ou NAT). Os módulos foram projetados usando modelos arquiteturais (SystemC) com metodologia de modelagem TL. Também foram testados quanto à funcionalidade, a partir da execução de aplicações simples. O mesmo modelo abstrato, além de permitir verificar a fonte relacionada ao baixo desempenho detectado na versão RTL, permitiu aos projetistas realizarem testes considerando diferentes variações da arquitetura via simulação.

O modelo de alto nível disponibilizou aos projetistas uma plataforma básica para ser usada no desenvolvimento e avaliação de futuros produtos. Permitiu avaliar problemas ocorridos na versão RTL previamente sintetizada e atingiu velocidades de simulação superior a uma centenas de vezes se comparado à simulação da versão RTL.

Benini et al. [BEN05] propõem um ambiente para exploração e simulação de MPSoCs baseado em SystemC 1.0.2, denominado MPARM. O ambiente contém seis componentes: (i) modelos de processador ARM, (ii) modelos de barramentos AMBA, (iii) modelos de memória, (iv) suporte à programação paralela, (v) sistema operacional uCLinux e (vi) ferramentas para desenvolvimento em linguagem C (GNU toolchain). Outra característica do ambiente é o encapsulamento de um ISS ARM desenvolvido em linguagem C++, fazendo uso de um wrapper SystemC. Segundo os autores o ambiente permite a exploração de diferentes arquiteturas de hardware e a análise de padrões de interação entre processadores, meios de armazenamento compartilhados e meios de comunicação. Segundo os Autores, isto permite definir métricas de desempenho, como média de ciclos de espera pelo barramento de acordo com o tamanho da cache, como esclarecem os resultados apresentados no artigo.

Beltrame et al. [BEL08] propõem uma plataforma de alto nível para modelagem e simulação de MPSoCs baseada em SystemC-TL e Python, denominada ReSP. Conforme

os Autores, a integração da linguagem Python junto à biblioteca SystemC aumenta a capacidade de modelagem e simulação. Os mesmos Autores apresentam em [BEL08b] uma evolução desse trabalho, uma metodologia para exploração de espaço de projeto em alto nível de abstração de plataformas reconfiguráveis. Esta metodologia utiliza a plataforma ReSP estendida para trabalhar com arquiteturas dinamicamente reconfiguráveis de modo a gerar um perfil da aplicação. A partir deste perfil as rotinas de maior custo computacional, como laços aninhados, são identificadas e migradas para hardware de forma dinâmica. A arquitetura sobre a qual a metodologia é aplicada é composta por seis componentes: (i) quatro processadores ARM, (ii) um FPGA, (iii) dois bancos de memórias RAM, (iv) um mecanismo de configuração (do inglês Configuration Engine, CE), (v) um gerenciador de configuração (do inglês Reconfiguration Manager, RM) responsável por interceptar as requisições das funcionalidades implementadas em hardware e desviá-las para o CE, e (vi) um barramento de comunicação.

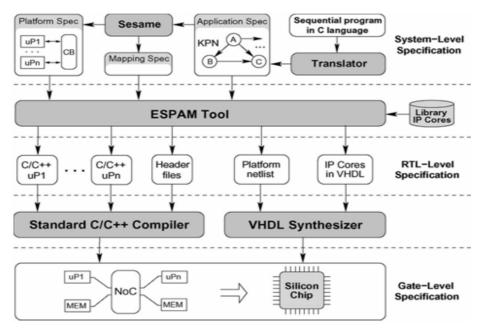

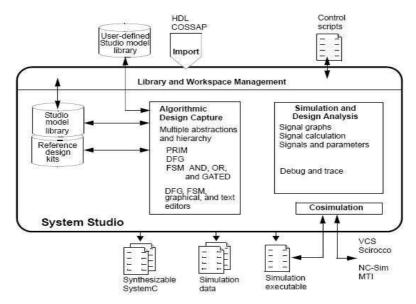

Nikolov et al. [NIK08] apresentam uma plataforma composta pela ferramenta ESPAM (do inglês, Embedded System-level Platform Synthesis and Application Mapping) conjuntamente ao fluxo de projeto ilustrado na Figura 2 para automatizar a programação, implementação e o projeto de MPSoCs. Essa plataforma recebe como entrada especificações em alto nível de abstração e gera uma plataforma MPSoC especificada em VHDL sintetizável, além de realizar o mapeamento da aplicação C/C++ sobre os processadores da plataforma. Segundo os autores, esta metodologia permite ao projetista desenvolver um sistema multiprocessado em menos tempo, reduzindo portanto a lacuna de produtividade de projeto.

Figura 2 – Fluxo de projeto proposto por Nikolov et al. [NIK08].

A ferramenta ESPAM recebe três tipos de especificações como entrada:

especificação de plataforma: descreve a topologia de uma plataforma

multiprocessada na qual a comunicação ocorre através de canais FIFO;

- especificação de aplicação: descreve uma aplicação como uma rede de processos Kahn (do inglês, Kahn Process Network, KPN), ou seja, uma rede de processos concorrentes comunicando-se via canais FIFO;

- especificação de mapeamento: descreve a relação entre todos os processos na especificação da aplicação e de todos os componentes na especificação da plataforma.

A plataforma foi validada através do desenvolvimento e programação de sistemas multiprocessados que executam as aplicações Sobel, DWT e M-JPEG considerando uma imagem de 128x128 pixels. Para as aplicações Sobel e o DWT foram utilizados três processadores Microblaze e para a M-JPEG quatro processadores, conectados por uma rede ponto a ponto. Os sistemas multiprocessados foram comparados com um sistema monoprocessado usando Microblaze ou PowerPC, indicando ganhos de desempenho da ordem de 2,2 vezes para Sobel, 2,1 para DWT e 3,75 vezes para M-JPEG.

## 2.1.2 Modelagem de MPSoCs com Simulink

Moreno et al. [MOR08] adotam três níveis de abstração para projetos de MPSoCs, quais sejam: arquitetura do sistema (do inglês System Architecture, SA), arquitetura virtual (do inglês Virtual Architecture, VA) e preciso em nível de transação (do inglês Transaction Accurate, TA). Dos três níveis, nos níveis VA e TA propõem-se a exploração da arquitetura do MPSoC, tendo sido ali que os autores descreveram modelos de NoC, os quais foram inseridos no fluxo de projeto MPSoC baseado no ambiente Simulink [THE08]. Os modelos de NoC propostos permitem avaliar o desempenho da arquitetura de comunicação através da variação de parâmetros durante a simulação do sistema e inserir definições abstratas de uma NoC no fluxo de projeto proposto originalmente em [POP07].

A tarefa básica para integrar os modelos NoC ao fluxo de projeto MPSoC é a modelagem do sistema. Esta fase é composta de três passos:

- modelagem da aplicação, que descreve a funcionalidade da aplicação alvo, gerando um modelo em alto nível de abstração a partir de Simulink;

- modelagem abstrata da infra-estrutura de comunicação, correspondendo à criação do modelo VA;

- refinamento da infra-estrutura de comunicação, gerando o modelo TA, permitindo detalhar a arquitetura local dos subsistemas.

A inserção dos modelos de NoCs no fluxo de projeto MPSoC permitiu a exploração da arquitetura da NoC e também estimar características relacionadas à implementação, além de permitir obter informações importantes para a tomada de decisão sobre o desenvolvimento da arquitetura de comunicação do sistema a partir dos modelos

propostos.

#### 2.1.3 Modelagem de MPSoCs baseada em Java e UML

Ost et al. [OST08] apresentam uma técnica para avaliação de características de MPSoCs com comunicação baseada em NoCs, reduzindo o tempo de simulação a partir do aumento do nível de abstração em que o sistema é descrito, mantendo precisão a nível de ciclo de relógio. Os Autores propõem uma técnica de abstração dos dados do pacote, denominada PAT (do inglês Payload Abstraction Technique), que permite avaliar o desempenho sob o ponto de vista da latência e vazão, a partir do uso de simulação e métodos analíticos.

PAT permite obter resultados relativamente precisos mantendo alto nível de abstração, enquanto reduz o tempo total de simulação, devido ao uso de um número menor de eventos de comunicação obtida a partir da abstração dos dados do pacote. Neste trabalho, a NoC HERMES é modelada usando dois componentes: controle e buffer: controle é responsável pela arbitragem da porta de entrada e o roteamento pelo repasse de dados; buffer é uma estrutura de memória do tipo FIFO, modelada com o uso de máquinas de estado finitas, que controlam o fluxo de dados. Também permite avaliar latência e vazão aproximadamente 2.3 vezes mais rápido quando comparado ao modelo de referência, RTL. Questões relativas a congestionamento de tráfego não foram observadas, podendo gerar algum impacto sobre os resultados.

Indrusiak et al. [IND08] apresentam uma abordagem para dar suporte à exploração do espaço de projeto de arquiteturas de interconexão usando NoCs. Os Autores visam criar modelos abstratos de NoCs e definir níveis de abstração adequados acima do nível RTL. A idéia básica é partir de um modelo NoC RTL e gerar um modelo orientado a atores pela análise de interações, cujo o espaço de projeto será validado e explorado de forma a chegar a um modelo RTL otimizado em relação ao primeiro.

Dois aspectos foram considerados importantes na criação de NoCs abstratas: abstração estrutural e comportamental. A abstração estrutural compreende como os subsistemas são divididos e a abstração comportamental envolve como e quando os subsistemas atualizam seu estado interno e interagem concorrentemente com outros subsistemas.

Duas etapas básicas são desenvolvidas: modelagem dos atores e análise baseada em interconexão. A modelagem dos atores separa a funcionalidade, representada pelos atores, da comunicação entre componentes, formalizada como modelos de computação (do inglês, Models of Computation, MoC) concorrentes, que se comunicam através de tokens de dados, e são gerenciados por um diretor. A análise baseada em interações é usada para abstrair interconexões da NoC RTL, formalizadas através de diagramas de seqüência (DS) UML. Estes descrevem todas as transações ocorridas e definem a ordem parcial entre mensagens, desconsiderando tempo e

concorrência. Esta abordagem facilita a exploração do espaço de projeto, permitindo ao projetista analisar diferentes alternativas para interconexão do sistema de forma interativa, visando atender adequadamente requisitos como desempenho, área utilizada e consumo de potência.

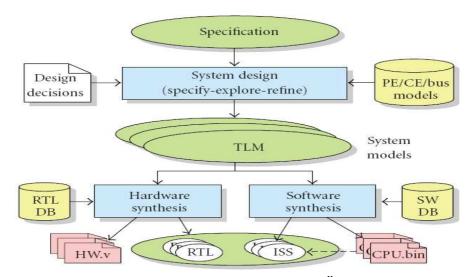

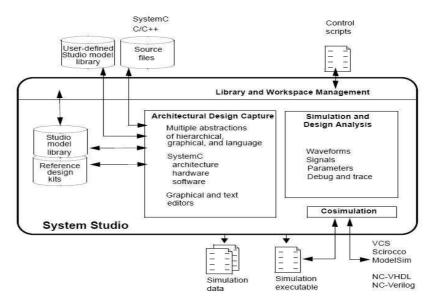

# 2.1.4 Modelagem de MPSoCs baseada em SpecC

Dömer et al. [DÖM08] propõem um fluxo de projeto denominada SCE (do inglês, System-on-chip Environment) baseado no paradigma "especificação-exploração-refinamento" com suporte para plataformas MPSoC heterogêneas e que emprega a linguagem SpecC. O fluxo parte de uma especificação abstrata do sistema alvo, onde modelos em vários níveis de abstração são automaticamente gerados através de sucessivos passos de refinamento. A Figura 3apresenta o fluxo de projeto adotado pelo SCE.

Figura 3 – Fluxo de projeto SCE [DÖM08].

A partir de uma especificação abstrata que descreve as funcionalidades do sistema, o projetista pode gerar modelos TL do projeto sucessivos em direção a níveis de abstração mais baixos, para tanto o fluxo usa modelos de componentes do repositório da ferramenta. Conforme o projetista gera novos modelos menos abstratos é possível tomar novas decisões, que serão integradas ao modelo recém gerado, a partir do modelo anterior. Após gerar os modelos, implementa-se componentes de hardware e software e cria-se descrições em Verilog no nível RTL.

#### 3 TRABALHOS RELACIONADOS

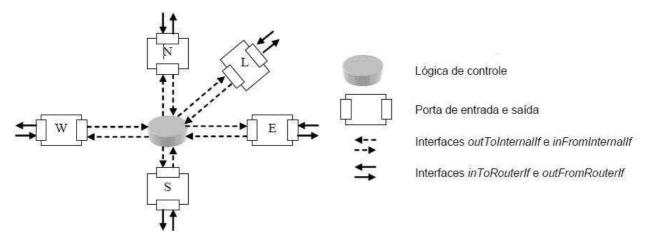

Este Capítulo introduz os trabalhos relacionados que foram considerados e/ou utilizados para o desenvolvimento abordado nos Capítulos seguintes. O Capítulo desenvolve-se em quatro Seções. A primeira aborda o sistema empregado como ponto de partida do trabalho, a plataforma multiprocessada HeMPS [WOS07]. Em seguida, as Seções 3.2 e 3.3 discutem os dois principais componentes da plataforma HeMPS, a rede intrachip HERMES [MOR04] e o processador Plasma, uma implementação da arquitetura RISC MIPS-I [RHO07]. Finalmente, a Seção 3.4 discute a ferramenta de modelagem escolhida para uso neste trabalho, o ambiente CoCentric System Studio da Synopsys [SYN08a].

# 3.1 Sistema multiprocessado HeMPS

O sistema HeMPS [WOS07] é uma infra-estrutura de hardware e software que permite a implementação de MPSoCs. HeMPS usa o processador Plasma como elemento de processamento do sistema multiprocessado e baseia sua comunicação na infra-estrutura de comunicação intrachip HERMES. O sistema HeMPS emprega multiprocessamento homogêneo e possui uma arquitetura de sistema baseada no paradigma mestre-escravo.

#### 3.1.1 Componentes de hardware

A infra-estrutura de hardware presente no sistema HeMPS é composta basicamente por três módulos:

- elementos de processamento: correspondem aos núcleos IPs dedicados ao processamento, que correspondem aos processadores Plasma. Existem duas classes de processadores: mestre (master) e escravo (slave). O mestre basicamente é responsável por distribuir as tarefas a serem executadas nos processadores escravo e gerenciar informações a respeito destas tarefas, existindo apenas um processador desta classe no sistema. Os processadores escravo são responsáveis por executar tarefas, podendo existir mais de uma tarefa em cada processador, pois estes executam um núcleo de sistema operacional que implementa a operação multitarefa. O mesmo núcleo implementa o suporte à comunicação entre tarefas, locais e/ou remotas;

- elementos de comunicação e roteamento: corresponde aos roteadores da rede HERMES, que habilitam a comunicação entre os vários elementos de processamento;

- canais de comunicação: representam aos meios que interligam os diversos roteadores presentes na rede HERMES.

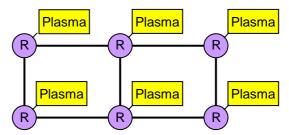

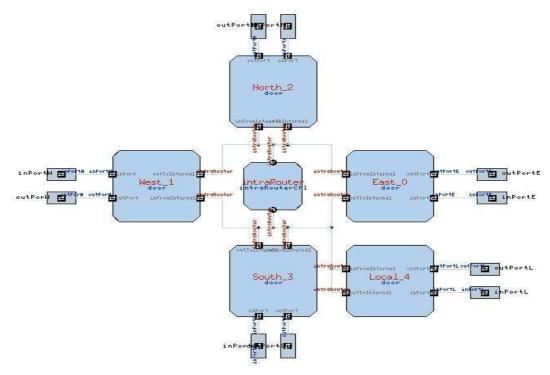

Uma instância de sistema que mostra a estrutura básica de hardware da HeMPS aparece na Figura 4.

Figura 4 – Componentes de hardware básicos do sistema HeMPS: elementos de processamento, roteadores e canais de comunicação.

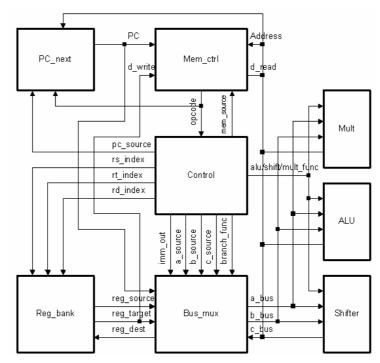

Figura 5 – Diagrama de blocos do Plasma, mostrando seus quatro módulos principais e sua interconexão [WOS07].

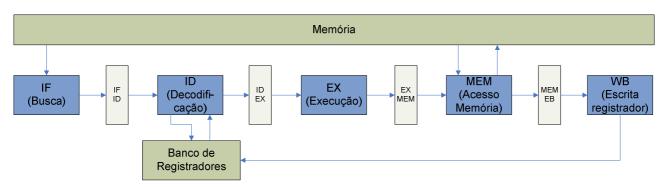

Na Figura 5 podem ser observados os quatro componentes básicos do módulo:

- CPU: denominado MLite, é um processador baseado na arquitetura RISC MIPS-I de 32 bits, discutido na Seção 3.3;

- RAM: corresponde à memória principal local do processador. Nesta memória são armazenados tanto o código das tarefas locais como os seus dados;

- Network Interface: trata-se da interface de rede, responsável por permitir a comunicação bidirecional entre processador e uma rede externa a este. Foi desenvolvido para dar suporte à comunicação do Plasma com a rede HERMES e vice-versa;

- DMA: é o módulo de acesso direto à memória (do inglês, direct memory access). O DMA permite aumentar o desempenho no sistema, uma vez que gerencia a transferência de grandes blocos de dados entre memória e rede de forma independente do processador.

Com relação ao projeto Plasma original o módulo Plasma usado no sistema HeMPS sofreu alterações a fim de adequar este projeto às necessidades do sistema. Entre as mudanças destaca-se a inserção do módulo DMA, a inserção da interface de

rede NI e do repositório de tarefas Mem Ext.

Mais detalhes da implementação do hardware do sistema HeMPS podem ser encontrados em [WOS07], sobretudo no Capítulo 4 desta dissertação.

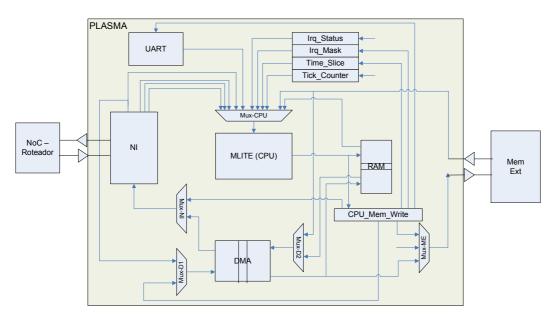

A Figura 6 apresenta uma versão do módulo Plasma com maior nível de detalhes.

Figura 6 - Detalhamento do caminho de dados do módulo Plasma no sistema HeMPS.

# 3.1.2 Componentes de software

A infra-estrutura de software existente no sistema HeMPS compreende dois grupos básicos de programas: microkernel e tarefas. O microkernel por sua vez possui duas versões, uma destinada à execução no processador mestre e outra que executa nos processadores escravos. As tarefas correspondem às aplicações a serem executadas em cada processador escravo, visto que na versão da HeMPS usada aqui o mestre não executa tarefas, apenas o microkernel.

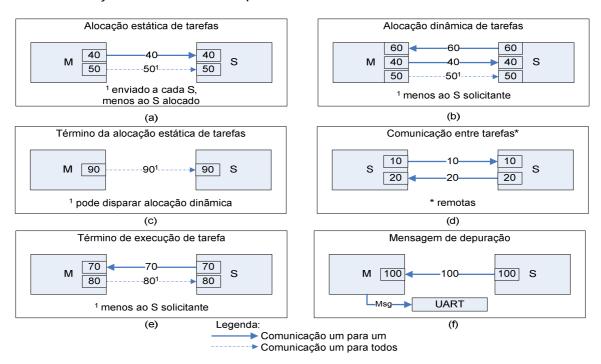

Sinteticamente, a versão mestre do microkernel realiza as seguintes tarefas: (i) executa o processo de inicialização (boot) onde todas as estruturas de dados necessárias são criadas e atribuídas; (ii) realiza a distribuição das tarefas a serem executadas de forma estática ou dinâmica; (iii) controla o escalonamento das tarefas em execução; (iv) implementa a comunicação entre os processadores, tanto no nível do microkernel (sistema) quanto no das tarefas; (v) operacionaliza o tratamento de interrupções tanto de software como de hardware.

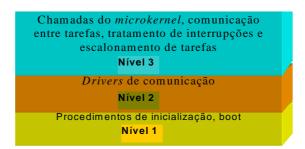

Figura 7 – Estrutura em níveis no microkernel da plataforma HeMPS.

A Figura 7 introduz a estrutura em camadas composta de três níveis adotada na arquitetura do microkernel juntamente à função executada por cada nível.

## 3.2 Infra-estrutura de comunicação intrachip HERMES

#### 3.2.1 Conceitos básicos

A infra-estrutura de comunicação intrachip HERMES [MOR04] foi desenvolvida no grupo de pesquisa do autor, o Grupo de Apoio ao Projeto de Hardware (GAPH) [GAP08]. O objetivo principal foi atingir largura de banda superior, quando comparada a arquiteturas de comunicação intrachip tradicionais, baseadas em barramento.

Um conjunto de modelos VHDL parametrizáveis foi desenvolvido para dar suporte à infra-estrutura HERMES. Através do emprego da ferramenta ATLAS [GAP08] é possível implementar diversas arquiteturas de comunicação a partir destes modelos. A infra-estrutura de comunicação gerada a partir dos modelos utiliza chaveamento por pacotes onde as mensagens a serem transmitidas são encapsuladas em pacotes roteados de forma individual e continua entre os nodos da rede, sem o estabelecimento prévio de um caminho. Este mecanismo de comunicação requer o uso de um modo de roteamento para definir como os pacotes devem se mover entre os roteadores. O modo de roteamento adotado para a comunicação é o wormhole. O roteamento de pacotes é implementado a partir do algoritmo XY distribuído, mas existem outras estratégias disponíveis na ferramenta ATLAS. O pacote é dividido em flits, unidades de controle de fluxo utilizadas para sincronizar a transferência de dados. Apenas os dois flits iniciais possuem informações de roteamento, os flits restantes compõem o conteúdo da mensagem e seguem o caminho determinado pelo algoritmo de roteamento escolhido.

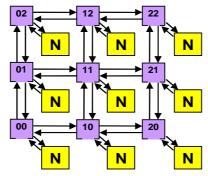

A NoC HERMES possui uma topologia regular malha 2D direta, que habilita a implementação do algoritmo de roteamento escolhido, a distribuição dos nodos de comunicação e a inserção de núcleos IP. Uma instância de rede HERMES ilustrando a topologia pode ser vista na Figura 8.

Figura 8 – Uma instância de uma NoC HERMES 3x3. Retângulos numerados representam os roteadores existentes e os valores identificam sua posição na rede, segundo a distribuição cartesiana XY. Assim, 21 indica o roteador localizado na terceira coluna (abscissas) e segunda linha (ordenadas). Os retângulos N representam os núcleos IP conectados a cada roteador.

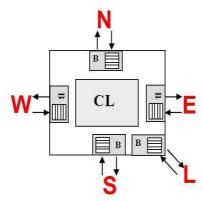

O componente básico da infra-estrutura HERMES é o roteador, com estrutura apresentada na Figura 9. O roteador HERMES possui cinco portas bidirecionais que se conectam com até quatro outros roteadores vizinhos e com um núcleo IP. O roteador usa armazenamento de dados na entrada e possui lógica de arbitragem interna. O roteamento é determinístico, distribuído e pode usar caminho mínimo e não mínimo entre origem e destino. Uma lógica de controle centralizada (CL na Figura) implementa arbitragem de acesso à lógica de roteamento e o próprio roteamento.

Figura 9 – Estrutura básica do roteador [MOR04].

O roteador HERMES contém três estruturas fundamentais:

- cinco portas de conexão (N, S, E, W e L): cada porta é composta por dois canais, um de entrada e outro de saída, e um elemento de armazenamento na entrada. São responsáveis pelo controle do recebimento e envio de dados que chegam ao roteador, tanto através de roteadores vizinhos como do núcleo IP local;

- lógica de controle (CL): realiza a arbitragem entre pedidos de roteamento concorrentes e controla o roteamento de dados entre as portas, podendo ocorrer transferências em paralelo entre mais de um par de portas de entrada/saída distintas. Cada transferência de dados passa pela lógica de controle;

- armazenamento (B): memória local para armazenamento temporário de

informações de entrada (buffer), o que permite um melhor desempenho da comunicação devido a possíveis bloqueios no fluxo de comunicação.

O formato do pacotes da rede HERMES é apresentado na Tabela 1.

Tabela 1 – Seqüência de envio de flits na rede HERMES. O primeiro flit contém o endereço de destino (target); o segundo carrega o tamanho da área de dados (size); a partir do terceiro flit são enviados os dados (payload).

| Seqüência<br>de envio | 0       | 1       | 2      |     | n-1        | n        |

|-----------------------|---------|---------|--------|-----|------------|----------|

| Conteúdo              | Destino | Tamanho | Dado 1 | ••• | Dado tam-1 | Dado tam |

Estes pacotes são compostos de duas partes: cabeçalho (header) e carga útil (payload). Estes por sua vez são transmitidos pela rede em unidades denominadas flits. Existem três diferentes tipos de flits: destino (target), tamanho (size) e carga útil (payload), os quais são enviados nesta mesma seqüência conforme a Tabela.

### 3.2.2 Modelo RTL sintetizável

A NoC HERMES foi desenvolvida originalmente via descrições RTL [MOR04]. Ela foi descrita em VHDL e validada por simulação funcional, sendo posteriormente sintetizada com sucesso em FPGAs. O protocolo de comunicação foi baseado no modelo de referência OSI, usando como de hábito apenas um subconjunto das camadas deste modelo: físico, enlace, rede e transporte. Basicamente cada camada provê, respectivamente, as seguintes funcionalidades:

- definir o mecanismo de comunicação entre os roteadores;

- estabelecer o protocolo handshake sobre a camada física, de forma a garantir o fluxo de controle dos dados enviados e recebidos;

- realizar a segmentação e remontagem dos dados em flits, ou seja, implementar a técnica de comunicação de chaveamento por pacotes;

- estabelecer a comunicação fim a fim entre origem e destino na rede.

A NoC HERMES implementa roteadores compostos por cinco portas de comunicação bidirecionais que podem estar conectadas a até cinco dispositivos periféricos, dependendo de qual posição ocupa na topologia. O caso em que todas as portas são usadas caracteriza-se quando o roteador se encontra inserido no interior da rede, ou seja, não ocupa nenhuma posição de borda quando algumas portas estarão desconectadas. Por exemplo, na Figura 8 o roteador 11 possui todas as portas conectadas enquanto o roteador 22 possui duas portas não utilizadas (N e E).

A Figura 10 apresenta a janela inicial da ferramenta gráfica para geração automática da infra-estrutura de rede HERMES denominada ATLAS [GAP08], que comporta quatro setores: (i) geração da NoC a partir da ferramenta NoCGen, (ii) geração do tráfego, (iii) simulação e (iv) avaliação. Estes quatro setores são alcançados a partir da janela inicial da ferramenta, conforme pode ser observado na Figura 10. A ferramenta

aceita em cada setor certa quantidade de parametrização, permitindo definir características como: largura de banda, profundidade de armazenamento de dados na entrada e número de canais virtuais. O setor de geração de tráfego produz dados para serem injetados na rede, o que permite avaliar diferentes cenários de tráfego. Na simulação, os dados gerados são injetados na NoC e a funcionalidade de comunicação é simulada entre os roteadores, conforme o cenário previamente definido. No último setor, avaliação, é possível analisar diversos aspectos de desempenho a partir de gráficos, tabelas, mapas e relatórios gerados automaticamente pela ferramenta, auxiliando a compreensão dos resultados gerados.

Figura 10 - Janela inicial do ambiente ATLAS.

#### 3.2.3 Modelo abstrato simulável