## ESCOLA POLITÉCNICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO DOUTORADO EM CIÊNCIAS DA COMPUTAÇÃO

VINICIUS MORAIS FOCHI

## FAULT-TOLERANCE AT THE MANAGEMENT LEVEL IN MANY-CORE SYSTEMS

Porto Alegre 2019

## PÓS-GRADUAÇÃO - *STRICTO SENSU*

Pontifícia Universidade Católica do Rio Grande do Sul

## PONTIFÍCIA UNIVERSIDADE CATÓLICA DO RIO GRANDE DO SUL ESCOLA POLITÉCNICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

# FAULT-TOLERANCE AT THE MANAGEMENT LEVEL IN MANY-CORE SYSTEMS

VINICIUS M. FOCHI

Thesis presented as partial requirement for obtaining the degree of PhD in Computer Science at Pontifícia Universidade Católica do Rio Grande do Sul.

Advisor: Prof. Fernando Gehm Moraes

## Ficha Catalográfica

F652f Fochi, Vinicius Morais

Fault-Tolerance at the Management Level in Many-Core Systems / Vinicius Morais Fochi . – 2019. 108 p. Tese (Doutorado) – Programa de Pós-Graduação em Ciência da Computação, PUCRS.

Orientador: Prof. Dr. Fernando Gehm Moraes.

1. MCSoCs. 2. System Management. 3. Fault-Tolerance. 4. Application Admission. 5. BrNoC. I. Moraes, Fernando Gehm. II. Título.

Elaborada pelo Sistema de Geração Automática de Ficha Catalográfica da PUCRS com os dados fornecidos pelo(a) autor(a). Bibliotecária responsável: Salete Maria Sartori CRB-10/1363 Vinicius Morais Fochi

## Fault-Tolerance at the Management Level in Many-Core Systems

Tese apresentada como requisito parcial para obtenção do grau de Doutor em Ciências da Computação do Programa de Pós-Graduação em Ciências da Computação, Escola Politécnica da Pontifícia Universidade Católica do Rio Grande do Sul.

Aprovado em 23 de agosto de 2019.

## BANCA EXAMINADORA:

Prof. Dra. Fernanda Kastensmidt – Avaliadora (UFRGS)

Prof. Dr. Eduardo Bezerra – Avaliador (UFSC)

Prof. Dr. Cesar Marcon – Avaliador (PUCRS)

Prof. Dr. Fernando Gehm Moraes (PPGCC/PUCRS - Orientador)

## ACKNOWLEDGMENTS

Gostaria de agradecer as pessoas que tiveram influência sobre o desenvolvimento desta tese e de todo meu Doutorado. Gostaria de dedicar esta conquista aos meus pais, José Jorge Fochi e Rosi Morais Fochi que me apoiaram a continuar estudando e a minha irmã Cristina.

Ao Professor Fernando Gehm Moraes, por aceitar o imenso desafio de continuar me orientando. Muito obrigado por manter reuniões semanais, me obrigando assim a trabalhar intensamente no desenvolvimento do trabalho. Obrigado por todo o conhecimento compartilhado e por sempre acreditar no nosso trabalho. Por ter compartilhado seu tempo e paciência para a realização desta tese. Sou muito grato por me aceitar como aluno de doutorado.

Agradeço a todos os professores do PPGCC pelo conhecimento compartilhado. Aos colaboradores do PPGCC pela dedicação em nos manter sempre informados dos prazos e burocracias.

Um agradecimento especial ao colega Luciano Lores Caimi, grande colaborador no desenvolvimento deste trabalho e organizar todos os eventos.

Aos colegas que me ajudaram durante a jornada do Doutorado: Eduardo Wachter, Marcelo Ruaro, L. Heck, G. Heck, Roger, Juraci, Marcelo Holgado e a todos os demais: obrigado pela ajuda!

Agradeço a Capes e os contribuintes por terem possibilitado e financiado esta pesquisa.

# TOLERÂNCIA A FALHAS NO NÍVEL DA GERERÊNCIA EM SISTEMAS MANY-CORE

#### RESUMO

A redução dos nodos tecnológicos permitiu o surgimento de sistemas com múltiplos núcleos de processamento utilizando redes intra-chip (MCSoCs - many-core systemson-chip), com dezenas a centenas de elementos de processamento (PEs). Apesar do poder de processamento oferecido pelo grande numero de PEs e da flexibilidade de comunicação devido à adoção de NoCs, é necessário gerenciar os recursos do sistema para garantir sua escalabilidade. A execução das tarefas de gerência requer PEs reservados exclusivamente para executar essas ações. Uma abordagem centralizada induziria uma carga de traba-Iho significativa para os PEs de gerência (MPE) em sistemas de grande escala. A adoção de abordagens distribuídas, com MPEs hierarquicamente organizadas, reduz a carga de gerência, sendo a organização adotada nesta Tese. Propostas recentes de gerência em MCSoCs focam em diferentes aspectos: potência, desempenho, utilização dos recursos do sistema. Essas técnicas são aplicadas no nível sistêmico dos MCSoCs. No entanto, nos trabalhos analisados, há uma lacuna nas propostas relacionadas a falhas permanentes nos MPEs. Esta Tese tem por objetivo abordar dois problemas principais. Primeiro, tratar falhas permanentes nos MPEs, desenvolvendo um conjunto de novas técnicas para que os MCSoCs continuem a operar corretamente, sem reexecutar as aplicações em execução. Segundo, resolver a questão do ponto único de falha na comunicação dos MCSoCs com o mundo externo. A contribuição original desta Tese é uma arguitetura MCSoC distribuída, com capacidade de recuperação de falhas em pontos críticos do sistema. O método de recuperação inclui módulos de hardware e software, monitoramento de falhas e recuperação de gerenciamento. A proposta utiliza técnicas de migração de tarefas e heurísticas para selecionar a posição do novo MPE. Esta Tese propõe um método de recuperação quando um MPE torna-se falho. O método é escalável, capaz de atuar em sistemas de dezenas a centenas de processadores. O método é transparente para as aplicações executadas no MCSoC, com uma pequena sobrecarga no tempo de execução, observado durante a migração de gerência e migração de tarefas.

**Palavras-Chave:** MCSoCs; NoC; Gerenciamento de sistemas; Recuperação de falhas; Migração de tarefas; Tolerância a falhas; Admissão de aplicativos; BrNoC.

# FAULT-TOLERANCE AT THE MANAGEMENT LEVEL IN MANY-CORE SYSTEMS

#### ABSTRACT

The technology nodes reduction enabled the emergence of NoC-based manycores with dozens to hundreds of processing elements (PEs). Despite the processing power offered by a large number of processors and communication flexibility due to the adoption of NoCs, it is necessary to manage the many-core resources to ensure scalability. The execution of the management tasks requires processing elements reserved exclusively to execute such actions. A centralized approach would induce a significant load to the managers PEs (MPE) in large-scale systems. The adoption of distributed approaches, with MPEs hierarchically organized, reduces the management load, being the organization adopted in this work. Recent proposals for Many-core System-on-chip (MCSoCs) management focus on different aspects: power, performance, system resources. These management techniques are applied to the systemic level of the MCSoCs. However, in the reviewed works, there is a gap in proposals related to permanent faults in processors with management functions. This Thesis aims to tackle two main problems. First, to treat permanent faults in management processors, developing a set of new techniques so that the MCSoCs continues to operate correctly, without re-executing applications running on it. Second, to solve the single point of failure issue regarding the communication of the MCSoCs with the external world. The original contribution of this Thesis is a distributed MCSoC architecture, with fault recovery capability at critical points in the system. The recovery method includes hardware and software modules, fault monitoring, and management recovering. The proposal uses task migration techniques, and heuristics to select the position of the new manager. This Thesis proposes a recovery method when an MPE became faulty. The method is scalable, able to act in systems from dozens up to hundreds of processors. The method is transparent to the applications executing in the MCSoC, with a small execution overhead observed during the management and task migration.

**Keywords:** MCSoCs; NoC; System Management; Fault-recovery; Task migration; Fault-tolerance; Application Admission, BrNoC.

# LIST OF FIGURES

| Figure  | 1.1 – Overview of <i>MCSoC</i> hardware model adopted as reference for this Thesis.                                                              | 19 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure  | 2.1 – Architectural overview of the invasive hardware/software stack [Paul                                                                       |    |

| Figure  | et al., 2015]                                                                                                                                    | 23 |

|         | et al., 2016].                                                                                                                                   | 24 |

| Figure  | 2.3 – Proposed software stack in the MADNESS project [Meloni et al., 2012].                                                                      | 25 |

| Figure  | 2.4 – Architecture proposed in the MADNESS project [Meloni et al., 2012].                                                                        | 26 |

| Figure  | 2.5 – Hardware test components placed near the processing cores [Kam-<br>ran et al., 2016].                                                      | 28 |

| Figure  | 2.6 – The Observe–Decide–Act control loop of [Bolchini et al., 2013].                                                                            | 30 |

|         | 2.7 – Overview of SoftRM proposal [Tsoutsouras et al., 2017].                                                                                    | 31 |

| -       | 2.8 – A Overview of Network-on-Chip (NoC) architecture with multiple cores<br>[Suraj Paul, 2018].                                                | 32 |

| Figure  | 2.9 – Fault Tolerance using replica tasks [Suraj Paul, 2018].                                                                                    | 33 |

|         |                                                                                                                                                  |    |

|         | 2.10 – A 6x6 platform with 3x3 clusters configuration [Domingues et al., 2018].                                                                  | 35 |

| -       | 2.11 – Block diagram of the OsPhoenix architecture [Silveira et al., 2016]                                                                       | 36 |

|         | 3.1 – HeMPS baseline architecture                                                                                                                | 39 |

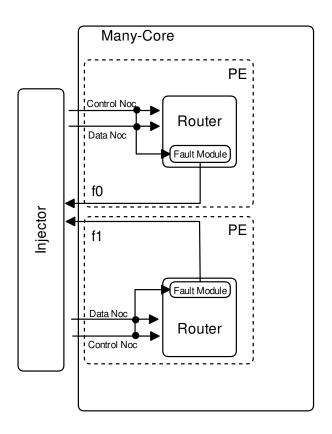

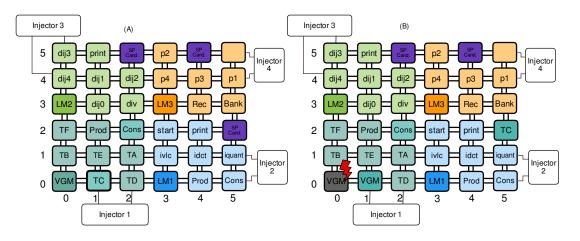

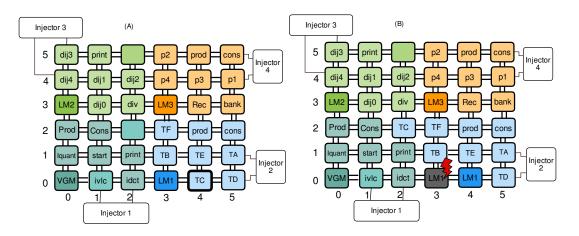

| -       | 3.2 – Modified architecture adopted in this Thesis                                                                                               | 40 |

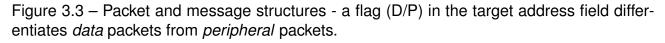

| Figure  | 3.3 – Packet and message structures - a flag (D/P) in the target address field differentiates <i>data</i> packets from <i>peripheral</i> packets | 43 |

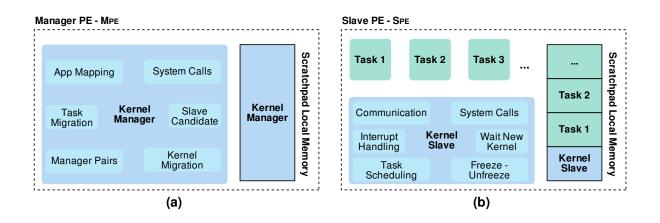

| Figure  | 3.4 – Overview of the kernels: (a) $M_{PE}$ kernel manages the system and do not execute users' tasks; (b) $S_{PE}$ kernel manage users' tasks   | 43 |

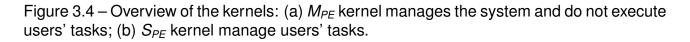

| Figure  | 3.5 – Application task graph example.                                                                                                            | 44 |

|         | 3.6 – <i>BrNoC</i> architecture.                                                                                                                 | 46 |

| _       | 3.7 – Control NoC Wrapper logic.                                                                                                                 | 47 |

| -       | 3.8 – Message ( <i>flit</i> ) and one row of <i>BrNoC CAM</i> memory.                                                                            | 47 |

|         | 3.9 – Example of path discovery using the <i>BrNoC</i> .                                                                                         | 49 |

| _       | 3.10 – Example of fault and freeze notification using the <i>BrNoC</i> .                                                                         | 51 |

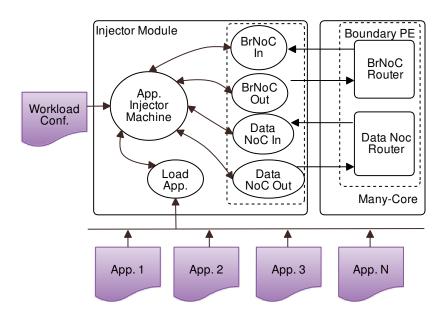

| -       | 3.11 – Application Injector connection with the MCSoC.                                                                                           | 53 |

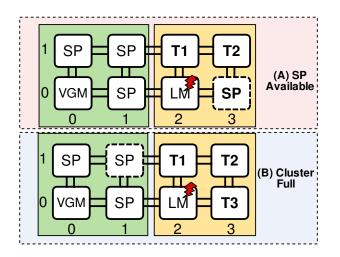

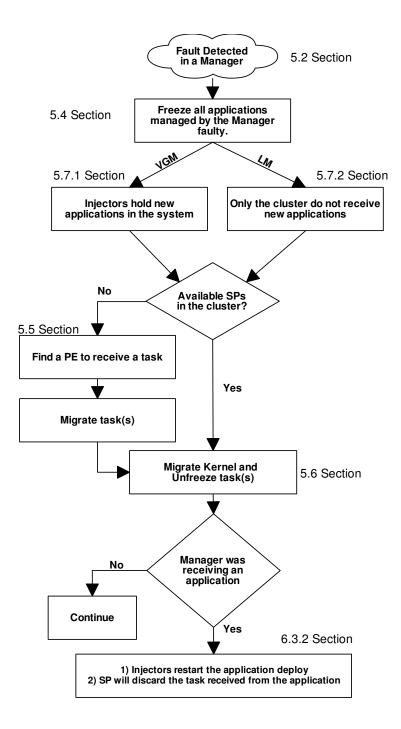

| -       | 4.1 – Scenarios handled by the recovery method: (a) cluster with available                                                                       | 50 |

| - iguie | SPs; (b) cluster with all SPs executing tasks.                                                                                                   | 56 |

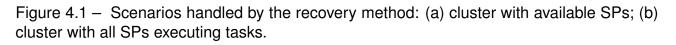

| Figure 4.2 – High-level flow chart, with the actions executed by the recovery proto-<br>col. Above the rectangles, it is inserted the section detailing the procedures.                          |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                            | 57 |

| Figure 5.1 – Example of ward pairs definition.                                                                                                                                                   | 62 |

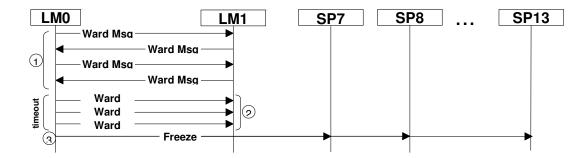

| Figure 5.2 – Protocol to detect a faulty MP using ward_messages.                                                                                                                                 | 62 |

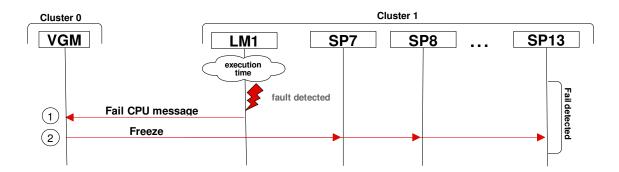

| Figure 5.3 - Fault notification using a fail_CPU_message.                                                                                                                                        | 63 |

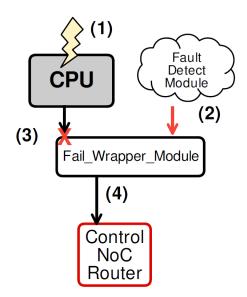

| Figure 5.4 – Fail Wrapper Module ( <i>FWM</i> ).                                                                                                                                                 | 64 |

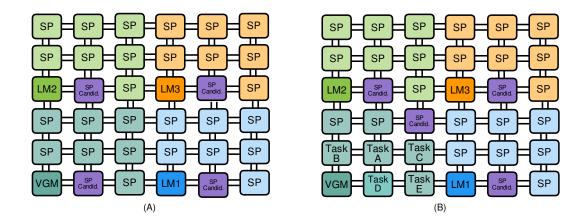

| Figure 5.5 – Manager Candidate ( <i>SP<sub>candidate</sub></i> ) selection - (a) startup; (b) selection after a new application admission.                                                       | 64 |

| Figure 5.6 – Freeze process on the cluster managed by the VGM. LM1 injects the freeze_message.                                                                                                   | 66 |

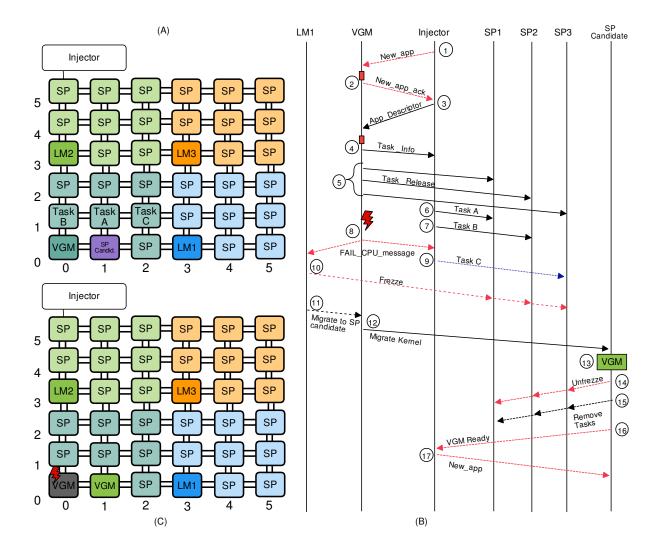

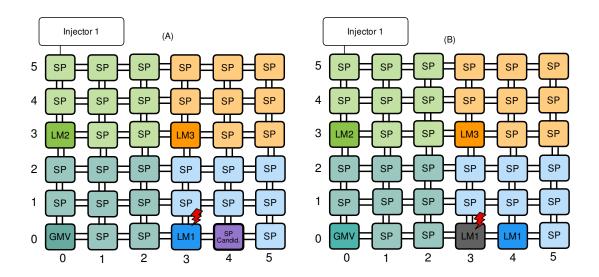

| Figure 5.7 – Task migration to release an <i>SP</i> . (A) Fault detect at <i>LM</i> ; (B) task C migrated from $PE_{2,1}$ , to $PE_{1,1}$ ; (C) <i>LM</i> migration from address (2,0) to (2,1). | 66 |

| Figure 5.8 – Sequence diagram of the recovery protocol steps with task migration.<br>Black arrows: messages transmitted through the Data <i>NoC</i> . Red arrow:                                 | 67 |

| messages transmitted through the Control <i>NoC</i> .                                                                                                                                            |    |

| Figure 5.9 – Kernel migration process in a faulty <i>MP</i>                                                                                                                                      | 69 |

| and a Virtual Global Manager migration.                                                                                                                                                          | 71 |

| Figure 5.11 – Local manager migration.                                                                                                                                                           | 72 |

| Figure 5.12 – Local manager recovery protocol.                                                                                                                                                   | 73 |

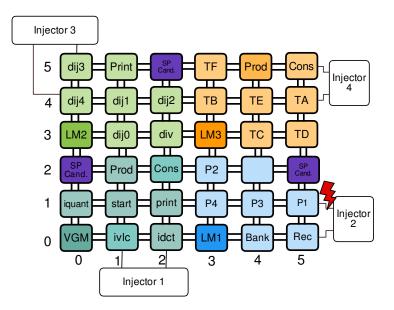

| Figure 6.1 – MCSoCs with multiple injector instances and redundant links.                                                                                                                        | 75 |

| Figure 6.2 – Interface between a injector and the MCSoC.                                                                                                                                         | 76 |

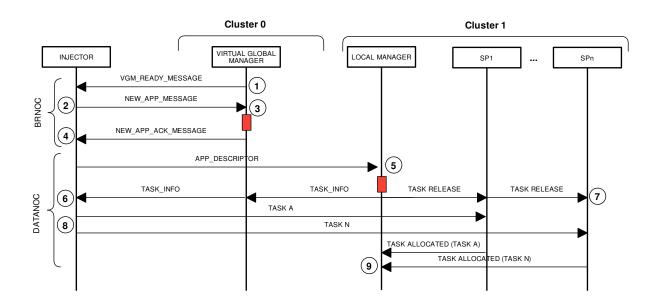

| Figure 6.3 – Application Admission Protocol.                                                                                                                                                     | 77 |

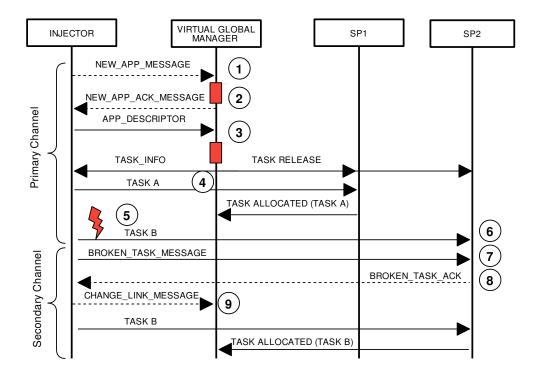

| Figure 6.4 – Fault in a the primary link.                                                                                                                                                        | 79 |

| Figure 6.5 – Recovery from a fault in a manager <i>PE</i> during application admission.                                                                                                          | 80 |

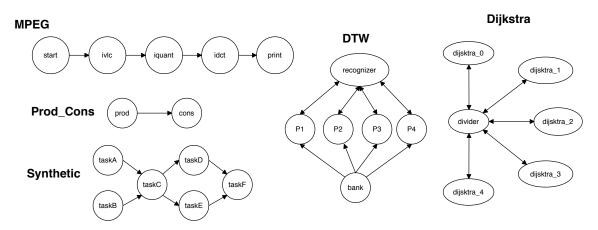

| Figure 7.1 – Task graphs used in the experiments.                                                                                                                                                | 82 |

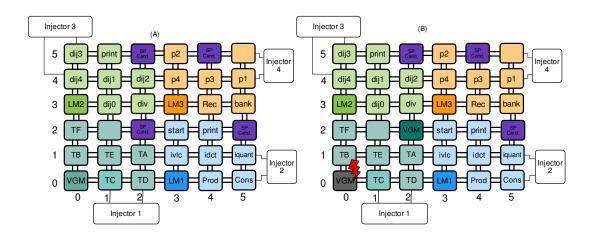

| Figure 7.2 – Recovery method for the VGM.                                                                                                                                                        | 83 |

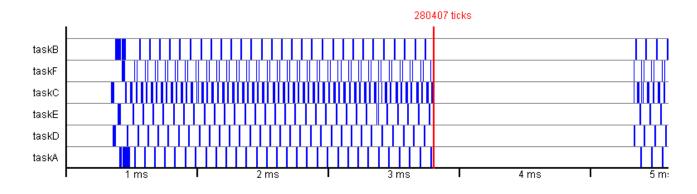

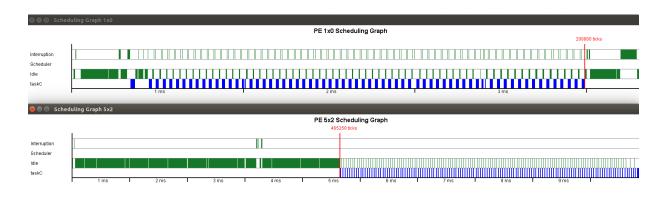

| Figure 7.3 - Scheduling of the Synthetic tasks, showing the moment when the                                                                                                                      |    |

| application is suspended.                                                                                                                                                                        | 84 |

| Figure 7.4 – Recovery method for the LM1.                                                                                                                                                        | 84 |

| Figure 7.5 – Recovery method for the VGM and a task migration.                                                                                                                                   | 85 |

| Figure 7.6 – Scheduling of Task C, showing the moment when the task migrate                                                                                                                      | 86 |

| Figure 7.7 – Recovery method for the LM1 and a task migration.                                                                                                                                   | 87 |

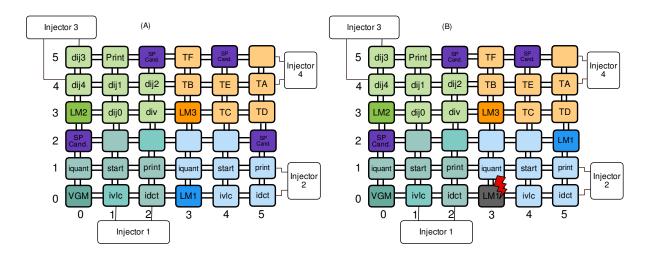

| Figure 7.8 – Fault in a the primary link from Injector 2.                                                                                                                                        | 88 |

| Figure 7.9 – Fault in a the primary link from Injector 1                  | 89  |

|---------------------------------------------------------------------------|-----|

| Figure 7.10 – Recovery method in a Manager during a application admission | 90  |

| Figure 7.11 – Recovery method in a Manager during a application admission | 91  |

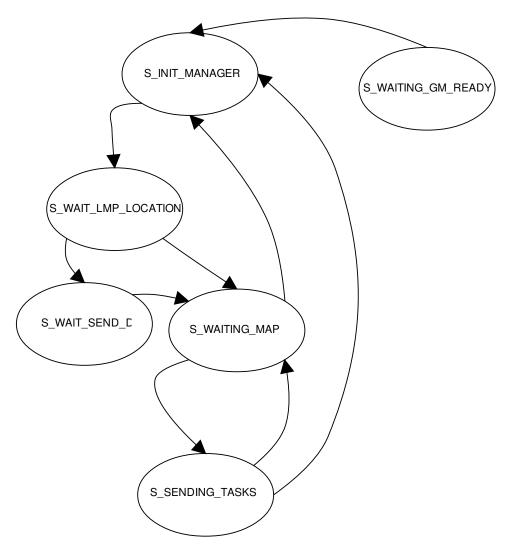

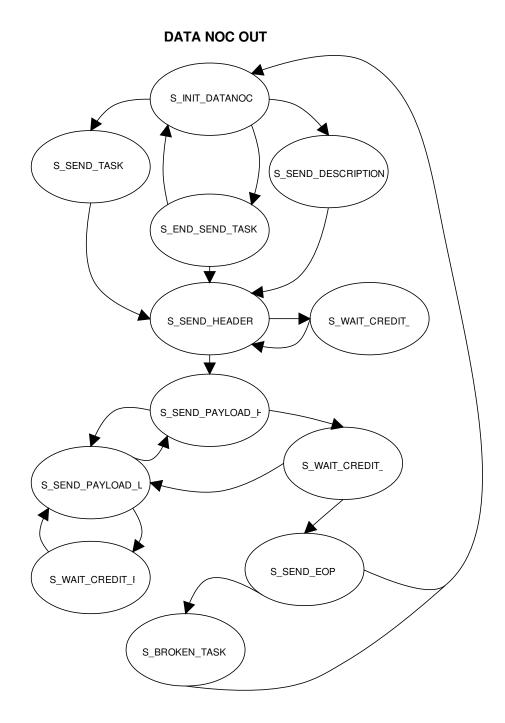

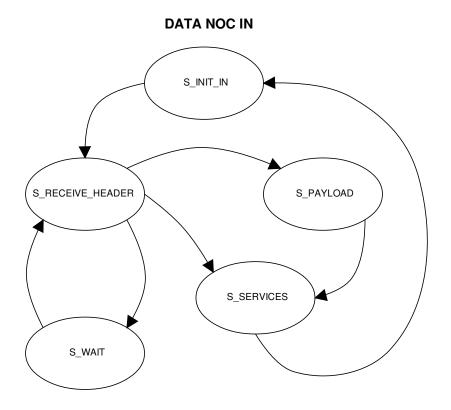

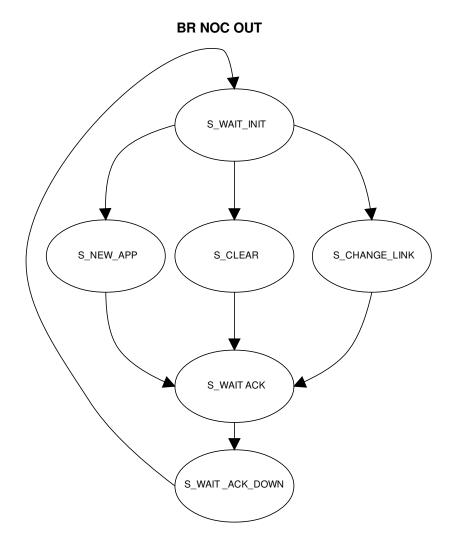

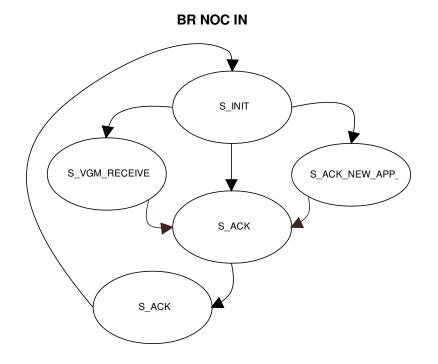

| Figure A.1 – Application Injector FSM                                     | 104 |

| Figure A.2 – Data NoC Out FSM.                                            | 105 |

| Figure A.3 – Data In NoC FSM.                                             | 106 |

| Figure A.4 – BrNoC Out NoC FSM.                                           | 107 |

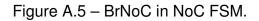

| Figure A.5 – BrNoC in NoC FSM.                                            | 108 |

# LIST OF TABLES

| Table 2.1 – Summary of the the state-of-the art.                                   | 38 |

|------------------------------------------------------------------------------------|----|

| Table 3.1 – Examples of messages types and purposes of the brNoC.                  | 50 |

| Table 7.1 – Overhead - VGM recovery.                                               | 83 |

| Table 7.2 – Applications' execution time.                                          | 83 |

| Table 7.3 – Overhead – LM recovery.                                                | 85 |

| Table 7.4 – Applications' execution time.                                          | 85 |

| Table 7.5 – Overhead - VGM recovery and task migration.                            | 86 |

| Table 7.6 – Applications' execution time.                                          | 86 |

| Table 7.7 – Overhead - LM recovery and task migration.                             | 87 |

| Table 7.8 – Applications' execution time.                                          | 87 |

| Table 7.9 – Recovery overhead from a fault in the primary link.                    | 88 |

| Table 7.10 – Applications' execution time.                                         | 88 |

| Table 7.11 – Recovery overhead from a fault in the primary link with task retrans- |    |

| mission                                                                            | 89 |

| Table 7.12 – Applications' execution time.                                         | 89 |

| Table 7.13 – Overhead to a VGM recovery.                                           | 91 |

| Table 7.14 – Application's execution time.                                         | 91 |

| Table 7.15 – Overhead from a LM recovery.                                          | 92 |

| Table 7.16 – Application's execution time.                                         | 92 |

| Table 7.17 – Summary of Results.                                                   | 92 |

| Table 8.1 – Summary of Publications.                                               | 96 |

# LIST OF ACRONYMS

- ACT Autonomous Chip Tester

- AET Application Execution Time

- AIM Application Injector Machine

- **API Application Program Interface**

- BRT Broker Recovery Time

- BSS Block Started by Symbol

- CAM Content Addressable Memory

- CRC Cyclic Redundancy Check

- DMA Direct Memory Access

- DMNI Direct Memory Network Interface

- DVFS Dynamic Voltage and Frequency Scaling

- DWC Duplication with comparison

- DWCR Duplication with comparison and re-execution

- ECC Error Correction Codes

- EBL Effective Buffer Length

- FIFO First In First Out

- FPD fault-resilient Packet delivery

- FPGA Field Programmable Gate Array

- FTR Fault-Tolerant Routing

- FSM Finite State Machine

- FWM Fail Wrapper Module

- GMP Global Manager Processor

- GM Global Manager

- GPPC General Purpose Processing Cores

- GPD General Purpose Device

- HEMPS Hermes MultiProcessor System

- I/O Input/Output

- IP Intellectual Property

- LMP Local Manager Processor

- LM Local Manager

- MEMPHIS Many-core Modeling Platform for Heterogenous SoCs

- MP Manager Processor

- MPSOC Multi-Processor System-on-Chip

- MCSOC Many-Core System-on-Chip

- NI Network Interface

- NOC Network On Chip

- NBTI Negative Bias Temperature Instability

- ODA Observe-decide-act

- OS Operating System

- PE Processor Element

- PDA Path-Diversity-Aware

- PPN Polyhedral Process Network

- PS Packet Switch

- QOS Quality Of service

- **RISC Reduced Instruction Set Computing**

- RTL Register Transfer Level

- **REM Runtime Energy Management**

- RTOS Real-Time Operating System

- SCC Single-chip Cloud Computer

- SA0 Stuck-At-0

- SA1 Stuck-At-1

- SR Source Routing

- SP Slave Processor

- SOC System-On-Chip

- SBST Software-Based Self-Test

- SAF Stuck-at Faults

- TCB Task Control Block

- TMR Triple Modular Redundancy

- TRA Test Response Analyzer

- TMSU Task Mapping and Scheduling Unit

- TM Task Mapper

- TS Task Scheduler

- VHDL VHSIC Hardware Description Language

- VLSI Very Large Scale Integration

- VHSIC Very High Speed Integrated Circuit

- WET Workload Execution Time

# CONTENTS

| 1     | INTRODUCTION                                        | 16 |

|-------|-----------------------------------------------------|----|

| 1.1   | MOTIVATION                                          | 17 |

| 1.2   | PROBLEM DEFINITION                                  | 18 |

| 1.2.1 | REFERENCE ARCHITECTURE                              | 18 |

| 1.2.2 | PROBLEM DEFINITION                                  | 19 |

| 1.2.3 | THESIS STATEMENT                                    | 20 |

| 1.2.4 | OBJECTIVES                                          | 20 |

| 1.2.5 | ORIGINAL CONTRIBUTIONS                              | 21 |

| 1.2.6 | DOCUMENT ORGANIZATION                               | 21 |

| 2     | STATE OF THE ART                                    | 22 |

| 2.1   | JOHNY PAUL ET AL                                    | 22 |

| 2.2   | ANDRÉ LUÍS DEL MESTRE MARTINS ET AL.                | 23 |

| 2.3   | PAOLO MELONI ET AL.                                 | 24 |

| 2.4   | YU-YIN CHEN ET AL                                   | 26 |

| 2.5   | AREZOO KAMRAN ET AL                                 | 27 |

| 2.6   | BISWAJIT BHOWMIK ET AL.                             | 28 |

| 2.7   | CRISTIANA BOLCHINI ET AL.                           | 29 |

| 2.8   | TSOUTSOURAS ET AL                                   | 31 |

| 2.9   | SURAJ PAUL ET AL                                    | 32 |

| 2.10  | DOMINGUES ET AL                                     | 34 |

| 2.11  | SILVEIRA ET AL                                      | 35 |

| 2.12  | RELATED WORK ANALYSIS                               | 36 |

| 3     | BASELINE PLATFORM                                   | 39 |

| 3.1   | BASELINE PLATFORM AND ITS EVOLUTION                 | 39 |

| 3.1.1 | DATA NOC                                            | 42 |

| 3.1.2 | SOFTWARE MODEL                                      | 43 |

| 3.2   | CONTROL NOC - BRNOC                                 | 45 |

| 3.3   |                                                     | 52 |

| 4     | SYSTEM MANAGEMENT RECOVERY OVERVIEW AND FAULT MODEL | 55 |

| 4.1   | PROPOSED RECOVERY METHOD OVERVIEW                   | 55 |

| 4.2   | ACTIONS EXECUTED BY THE RECOVERY PROTOCOL                               | 56 |

|-------|-------------------------------------------------------------------------|----|

| 4.3   | FAULT MODEL                                                             | 58 |

| 4.3.1 | FAULT DETECTION MECHANISMS                                              | 58 |

| 5     | SYSTEM MANAGEMENT RECOVERY METHOD                                       | 61 |

| 5.1   | MANAGER PAIRS DEFINITION                                                | 61 |

| 5.2   | FAULT DETECTION NOTIFICATION                                            | 62 |

| 5.3   | MANAGER CANDIDATE DEFINITION                                            | 64 |

| 5.4   | FREEZE & UNFREEZE MESSAGES                                              | 65 |

| 5.5   | TASK MIGRATION                                                          | 66 |

| 5.6   | KERNEL MIGRATION                                                        | 68 |

| 5.7   | RECOVERY PROTOCOL                                                       | 70 |

| 5.7.1 | VIRTUAL GLOBAL MANAGER FAULT RECOVERY                                   | 70 |

| 5.7.2 | LOCAL MANAGER FAULT RECOVERY                                            | 72 |

| 5.8   | FINAL REMARKS                                                           | 73 |

| 6     | APPLICATION ADMISSION RECOVERY METHOD                                   | 75 |

| 6.1   | INJECTOR HARDWARE MCSOCS AND FAULTS MECHANIMS                           | 75 |

| 6.2   | APPLICATION ADMISSION PROTOCOL                                          | 77 |

| 6.3   | FAULT RECOVERY DURING APPLICATION ADMISSION                             | 78 |

| 6.3.1 | RECOVERY FROM A FAULT IN THE PRIMARY LINK                               | 78 |

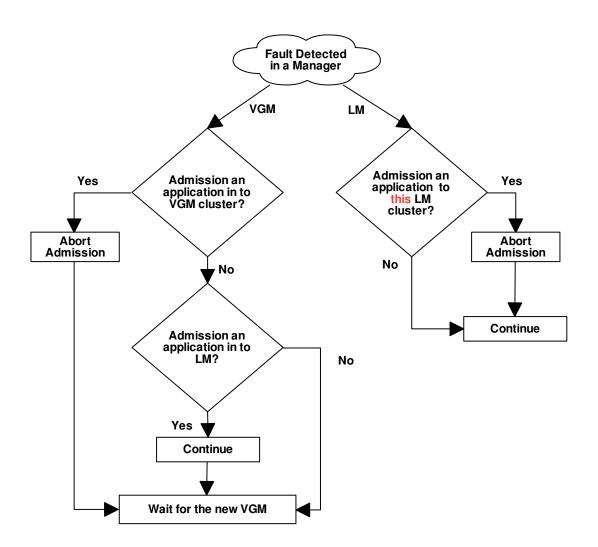

| 6.3.2 | RECOVERY FROM A FAULT IN A MANAGER PE DURING APPLICATION AD-<br>MISSION | 79 |

| 6.4   | FINAL REMARKS                                                           | 80 |

| 7     | EXPERIMENTAL RESULTS                                                    | 82 |

| 7.1   | RECOVERY RESULTS FROM A FAULT IN A MANAGER                              | 82 |

| 7.2   | RECOVERY RESULTS FROM A FAULT IN A MANAGER WITH TASK MIGRA-             | 85 |

| 7.3   | RECOVERY RESULTS FROM A FAULT IN THE PRIMARY LINK                       | 88 |

| 7.4   | RECOVERY RESULTS FROM A FAULT IN A MANAGER DURING APPLICA-              | 90 |

| 7.5   | FINAL REMARKS                                                           | 92 |

| 8     | CONCLUSION                                                              | 93 |

| 8.1   | FUTURE WORKS                                                            | 95 |

| Α     | INJECTOR FINITE STATE MACHINES | 104 |

|-------|--------------------------------|-----|

| Apper | ndices                         | 103 |

|       | REFERENCES                     | 97  |

| 8.2   | PUBLICATIONS                   | 96  |

## 1. INTRODUCTION

The continuous development in Very Large Scale Integration (*VLSI*) technology and scaling of transistors to nanometer range led to the integration of billions of transistors on a single chip. This allows the system designer to embed a large number of intellectual property cores, memory units, and Processing Elements (*PEs*) onto a single chip resulting in a System-on-Chip (*SoC*).

Shared buses are commonly used for the communication between different computation and memory units present in the *SoC*. However, the performance of on-chip communication medium between the components becomes a critical issue with the increase in the number of cores [Grecu et al., 2004]. Networks-on-chip (*NoCs*) have been proposed as a viable solution to deal with this limitation [Benini and Micheli, 2002]. In the *NoC* paradigm, data communication among various cores is achieved through an on-chip network consisting of routers and links. In a direct *NoC* topology, each core is attached to a router through a Network Interface (*NI*) module. *NoCs* provides a scalable, flexible, and reusable communication infrastructure, which is required for *SoCs* where different on-chip elements need to communicate with each other in parallel.

Large *SoCs* require processing elements (*PEs*) dedicated to management purposes, for example, execute the task mapping, handle monitoring data obtained from sensors and estimation functions, and run self-awareness adaptation (e.g., quality-of-service, *DVFS* control, aging, temperature) [Dutt et al., 2015, Tajik et al., 2016]. Many-core Systems-on-Chip (*MCSoCs*) with a hierarchical organization ensure scalability at the management level, with *PEs* having distinct roles: managers (*MP*), responsible for manipulating system resources at runtime, and slave processors (*SP*), processors that only executed tasks, [Faruque et al., 2008]. With such organization, *MCSoCs* contains virtual regions, named clusters, with one *MP* and a set of *SPs* per cluster. A cluster may increase its size at runtime, borrowing *SPs* from neighbor clusters, in a process named re-clustering [Castilhos et al., 2013].

Transistors, vias, and wires degrade faster over time in deep sub-micron technologies, inducing transient faults and permanent faults, thus shortening integrated circuits lifetime [Kim et al., 2013]. The aggressive technology scaling and increasing design complexity of *MCSoCs* made the chip components vulnerable to faults. The failure rate of electronic components increases as high as 316% with 64% decrease in the feature size [Srinivasan et al., 2004]. These faults may be permanent or transient. Permanent faults are nonrecoverable device defects. These faults can occur due to manufacturing defects or device wear-out caused by Negative Bias Temperature Instability (*NBTI*) [Knebel et al., 2016], electromigration and oxide breakdown [Fick et al., 2009a]. While, transient faults are temporary random faults that may occur for a short interval of time due to, e.g., crosstalk [Cui et al., 2016], alpha particles, cosmic radiation [Li and Draper, 2016], permanent faults damage the on-chip elements. As a result, components with permanent faults are no longer available to the system, inducing performance degradation, system malfunction, or compromising the entire chip.

Thus, reliability becomes a key issue in *MCSoC* design [Heron et al., 2010]. Classical fault-tolerant approaches, as Triple Modular Redundancy (*TMR*) or spare components [Reddy et al., 2016], do not comply with today's requirements of silicon area and power dissipation. Due to the way it is built, an *MCSoC* provides a set of replicated structures (*PEs*), where a healthy component can execute the faulty component functions, resulting in graceful performance degradation.

It is worth to differentiate the consequences of a permanent fault in *SP*s and in *MP*s. A fault in a PE executing a user application (*SP*) compromises the application, being possible to remap the application [Barreto et al., 2015]. The effect of a fault in an *MP* is more severe than a fault in an SP, because it may halt the entire cluster, making the set of *SP*s controlled by the faulty MP unavailable.

#### 1.1 Motivation

Modern *MCSoCs* increasingly require runtime fault recovery methods because fault probability increases in deep-sub-micron technology nodes. Thus, systems should adopt self-adaptation techniques to cope with transient and permanent faults to extend the system lifetime.

System management, and how to deal with a failure on it, opens a set of new challenges and opportunities in the field of many-core systems research. Several system-level approaches are available in the literature: as power management (*DVFS*)[Martins et al., 2016], performance/quality-of-service (*QoS*) management [Ruaro and Moraes, 2017], resource management[Paul et al., 2015]. A rich literature with methods to test the processing elements modules is also available, with approaches adopted at different levels (hardware or software) or modules (as *NoC*[Fochi et al., 2015], processors, memories [Meloni et al., 2012]).

However, there is a gap in the literature related to fault-tolerant methods at the system level, i.e., related to the processors with the function to manage the system. Therefore, system management requires alternative monitoring and actuation policies to recover the system when one of these processors presents a permanent fault.

Besides fault-tolerant methods at the system level, the deployment of new applications into the *MCSoCs* is a subject with few works in the literature. The availability of distributed *MCSoCs* architectures adds flexibility to define new methods to deploy applications into the system. For example, it becomes possible to consider several instances responsible for injecting new applications into the *MCSoC*, eliminating the single point of failure when only one device is in charge to deploy applications.

In the context of this Thesis, the focus of the research is the investigation of techniques to deal with permanent faults in *MP* and methods to deploy applications into the *MCSoC*. Fault detection is out of the scope of the Thesis.

## 1.2 Problem Definition

This Session initially presents the *MCSoC* reference architecture with the goal to identify to the reader the relevant features of modern systems. Next, the text presents the challenges related to fault-tolerance covered in this Thesis.

## 1.2.1 Reference Architecture

This Section presents the reference architecture. The Thesis adopts it for the proofof-concept of proposed methods. It is worth to mention the methods proposed throughout this Thesis are not specific to this architecture, but generic, with applicability in systems with similar architectural features.

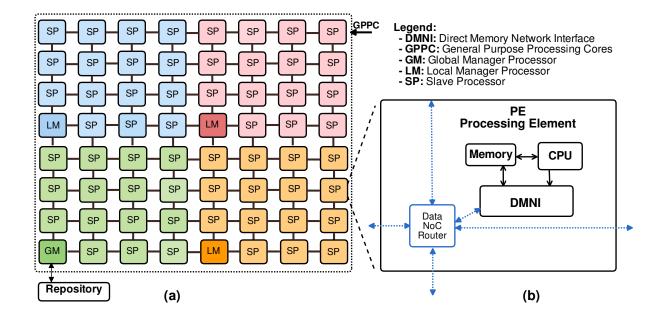

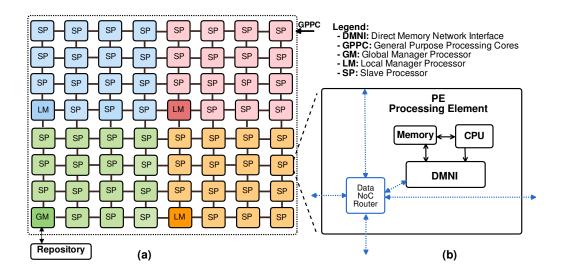

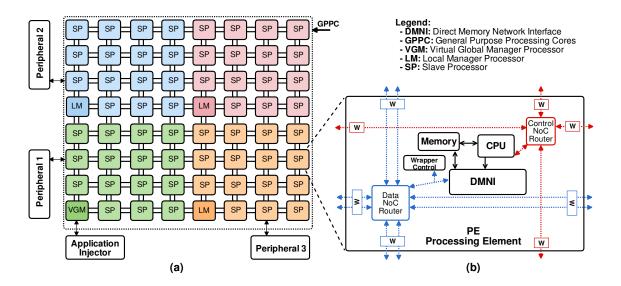

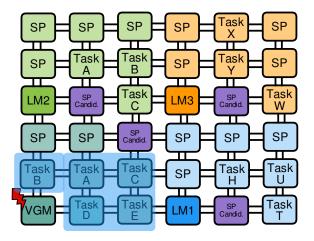

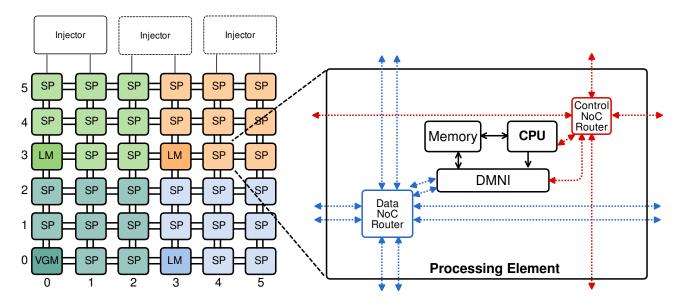

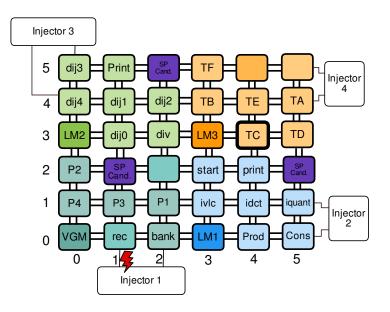

The reference many-core platform (Figure 1.1) has the following features [Carara et al., 2009, Castilhos et al., 2013, Ruaro et al., 2019]:

- NoC-based system: the Network-on-Chip (*NoC*) connection allows multiple communications between *PE*s while ensures scalability. The *NoC* adopts 2D-mesh topology, input buffering, credit-based flow control, round-robin arbitration, wormhole packetswitching, support for deterministic XY and source routing, 8-flit buffer depth, input buffering, and duplicated physical channels (two 16-bit channels per link), enabling full adaptive routing.

- Homogeneous *GPPC* (General Purpose Processing Core): all *PE*s have the same hardware architecture with a router, a private memory, an MIPS-like processor and a Direct Memory Network Interface (*DMNI*) module.

- Distributed memory: each *PE* has a private memory, responsible for storing instructions and data. Inter-task communication occurs through message-passing.

- Applications modeled as task graphs: the applications are divided into tasks, and a graph defines the communication flow between them.

Distributed management: the system is divided into clusters. Every cluster contains a Local Manager *PE* (*LM*), which manages the cluster, and a set of Slave *PEs* (*SPs*), which runs the applications' tasks. One of the *LMs* has the role of Global Manager (*GM*), being the only PE with access to external devices (e.g. application repository). The *GM* works as a *LM* and distributes the applications to clusters. The Operating System (*OS*) running on *PEs* defines their role in the system.

Figure 1.1 – Overview of *MCSoC* hardware model adopted as reference for this Thesis.

### 1.2.2 Problem Definition

Recent proposals for many-core management focus on different aspects: power [Martins et al., 2016, Haghbayan et al., 2014], performance [Bolchini et al., 2013], system resources [Paul et al., 2015]. These management techniques are applied to the systemic level of the *MCSoC*. However, in the reviewed works, there is a gap in proposals related to permanent faults in processors with management functions.

For fault-tolerance, the literature present proposals at different levels: processor level [Braak et al., 2010, Walters et al., 2011], router level [Yu et al., 2011, Chen et al., 2017], link level [Vitkovskiy et al., 2012, Veiga and Zeferino, 2010]. It is important to differentiate the impact of a permanent fault in a *SP* and in a manager processor (*GM* and *LM*). A faulty *SP* may be isolated using wrappers and the tasks assigned to it remapped to another SP. A faulty manager processor compromises all *SP*s of the cluster by compromising the computational capacity of the system, but the system may continue to operate. The existence of a *LM* with a global management function (*GM*) represents a single point of failure.

This Thesis aims to tackle two main problems. First, to treat **permanent** faults in management processors (*LM* and *GM*), developing a set of new techniques so that the *MCSoC* continues to operate correctly, without re-executing applications running on it. Second, to solve the single point of failure issue regarding the communication of the *MCSoC* with the external world.

## 1.2.3 Thesis Statement

Hardware and software faults in *MCSoCs* may compromise not only the execution of the applications, but also reduce the system lifetime. A weakness in *MCSoCs*' design is its management, frequently made by a single processor with a single interface with the external world.

The Thesis herein proposed aims to demonstrate that it is possible to develop a distributed *MCSoC* architecture, supporting permanent faults at critical points of the system, as in the processors executing management functions, and at the interface of the *MCSoC* with external entities responsible for deploying new applications into the system.

#### 1.2.4 Objectives

The strategic goal of the Thesis is the specification, development, and validation of methods for fault recovery in manager processors, intending to eliminate the single point of failures in an *MCSoCs*.

The specific goals of the Thesis include:

- Define methods to trigger the fault recovery mechanism after the fault detection;

- Define methods to migrate the memory contents of a faulty PE to a healthy one;

- Create a software structure where the manager processors can be recovered by a health *PE*;

- Define the method to connect external hardware modules to the MCSoCs;

- Validation of approaches with faults injected in any manager processor.

#### 1.2.5 Original Contributions

The original contribution of this Thesis is a distributed *MCSoC* architecture, with fault recovery capability at critical points in the system. The recovery method includes hardware (Sections 3.1 and 3.2 and Chapter 6) and software modules (Sections 5.3, 5.5 and 5.6), fault monitoring and management recovering. The proposal uses task migration Section 5.5, techniques, and heuristics to select the position of the new manager (Section 5.3). The proposal is scalable, able to act in systems from dozens up to hundreds of processors.

#### 1.2.6 Document Organization

The remaining of this document is organized as follows. Chapter 2 reviews and discusses system management and fault-tolerance related works, positioning the current Thesis with regard to the state-of-the-art. Chapter 3 details the *MCSoC* baseline platform and its evolution in the context of this work. This Chapter presents the two first contributions of the Thesis, the *brNoC* (Section 3.2) and the Injector Module (Section 3.3). Chapter 4 presents a general view of the system management recovery method. This presentation is required to provide a comprehensive perspective of the proposals discussed in the next Chapters. Chapter 5 presents the third contribution of the Thesis, the recovery method of the system management functions, action required when a Manager *PE* becomes faulty. Chapter 6 presents the fourth contribution of the Thesis, the modifications carried-out at the *MCSoC* boundaries to cope with faults during the applications' admission. Chapter 7 presents results related to the methods proposed in Chapters 5 and 6. Finally, Chapter 8 concludes this Thesis, pointing-out directions for future works.

## 2. STATE OF THE ART

This Chapter reviews and discusses system management and fault-tolerance related works. The Chapter finishes with a comparison between its key features, positioning the current Thesis with regard to the state-of-the-art.

### 2.1 Johny Paul et al.

Paul et al. [Paul et al., 2015] propose a system management technique. The Authors use a resource-aware computing paradigm called Invasive Computing to reduce the negative effects of resource sharing in MPSoCs with the focus in mobile robotics applications. In the proposal, the operating system (*OS*) can influence the applications' internal decisions, based on dynamic load distribution. Using the resource-aware programming model, the application gains the ability to adapt to available resources by changing its workload.

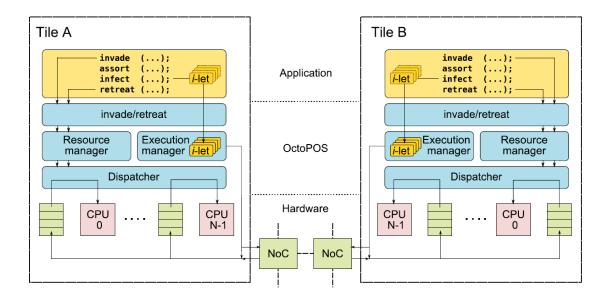

To achieve the programming model of invasive computing, it is necessary an *OS* specifically designed to support the model. The authors choose the OctoPOS [Schedel et al., 2011] *OS*. This *OS* provides primitives and a scalable and low-overhead execution environment for invasive-parallel applications. Figure 2.1 presents the overall system design of OctoPOS, showing two instances of OctoPOS running on two compute tiles. The proposal has 4 phases: invasive, assort, infect, and retreat. In the invasive phase, applications exclusively acquire resources according to their needs. In the assort phase, the application adapts itself according to the number of resources received from the system. In the infect phase, the processing elements designated to executed the tasks are said "infected", and once the execution has finished, the results can be collected and merged. In the retreat phase, the allocated resources are released.

The Authors executed experiments to evaluate the adaptive algorithm using a platform prototyped in an *FPGA* (Xilinx Virtex-5 XC5VLX330) at 50MHz, with 16 SPARC LEON3 processing elements equally distributed over 4 tiles connected via a custom-designed *NoC*. The authors considered the execution time and cycle-accurate time-stamp counters available in the hardware prototype.

A comparison with two adaptive algorithms, Harris and Shi-Tomasi corner detector, are made to evaluate the new resource-aware algorithm. Applications like audio processing or motor control are used to compare the results. The main conclusions from the work are: (*i*) the model helped to avoid frame drops, no frame was dropped during the evaluation, and the accuracy values improved significantly over the conventional approach; (*ii*) when the resources are the same both approaches have the same accuracy values, but when the resources are scarce the resource-aware model starts to adapt the workload by increasing

Figure 2.1 – Architectural overview of the invasive hardware/software stack [Paul et al., 2015].

the pruning threshold resulting a slight drop in accuracy however the overall accuracy has improved significantly over the conventional approach; (*iii*) the resource-aware model improves the performance, with up to 22% improvement in the throughput and up to 20% the accuracy.

#### 2.2 André Luís Del Mestre Martins et al.

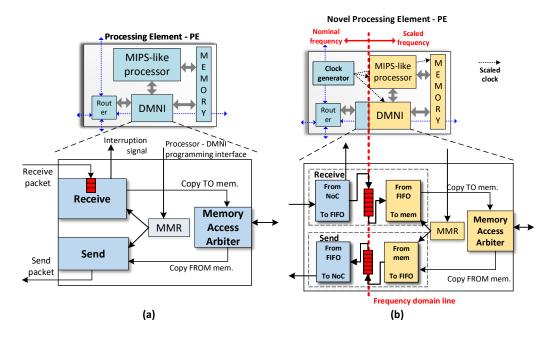

Martins et al. [Martins et al., 2016] propose a power management method, called Runtime Energy Management (*REM*) to reduce energy while guaranteeing scalability, focusing on homogeneous NoC-based MPSoCs. In the proposal, the power management controls the system by monitoring the energy consumption at the *PE* level using fine-grain *DVFS* as the primary power control policy. Scalability is ensured by a distributed management architecture, responsible for power monitoring and actuation on individual cores to respect power constraints.

To implement the *DVFS* technique in the reference platform, the Authors propose different strategies for modeling the frequency and voltage scaling. To model the frequency scaling, the original *PE* structure was modified, in such a way to have the *NoC* router always running at the nominal frequency, while the processor and memory support different frequencies. To guarantee realistic *DVFS* support, the authors propose a model of voltage scaling considering hardware overheads, as latency and energy.

The *DVFS* actuates on the processor, memory, and *DMNI* as shown in Figure 2.2. With this hardware modification, the processor may work at different voltage-frequency pairs, while the *NoC* transmits packets using the nominal frequency. The *DMNI* module is respon-

sible for synchronizing the modules working at different frequencies. The *DVFS* protocol manages the minimum period for scaling the voltage safely with the frequency range generated by the clock generator.

The *REM* monitors packets sent by each *PE*. All PEs send their energy values to the cluster manager *PE* periodically. The *REM* heuristic defines three energy zones: (*i*) hot zone: energy is above a given high threshold; (*ii*) cold zone: energy is below a low threshold; (*iii*) warm zone: the energy is between hot zone and cold zones. The power zones are configured at the design-time. The manager *PE* receives monitoring packets from the PEs. If a given PE is in the hot zone, a packet is sent to the *SP* to scale down the frequency and voltage; if the PE is in the cold zone a packet is sent to scale up the frequency and voltage.

Figure 2.2 – (a) Original PE and (b) new PE with DVFS support. The new PE has Clock Generator hardware as well as changes on the DMNI [Martins et al., 2016].

Results show an average energy saving of 12.09%, with an execution time overhead of 19.04% to a light power management policy and an average energy saving of 47.39% with an execution time overhead of a 38.22% to a restrict power management policy.

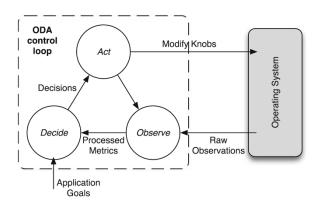

## 2.3 Paolo Meloni et al.

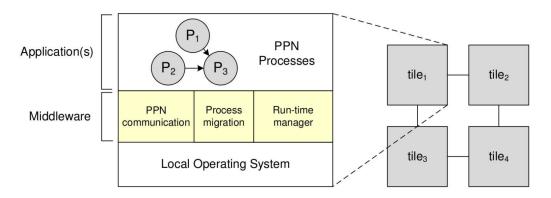

Meloni et al. [Meloni et al., 2012] propose the MADNESS project, which provides adaptive fault tolerance management in NoC-based MPSoCs. The method uses task migration to handle faults in a processing element that presents a permanent fault by migrating the task to a processor free of faults. The method proposed in [Meloni et al., 2012] involves different layers during the *MPSoC* design. At the application level, a software infrastructure was

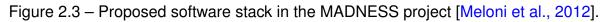

proposed allowing the execution of the applications in a computational model called Polyhedral Process Network (*PPN*), which consists of autonomous and concurrent processes that communicate with each other through *FIFO* channels. The middleware layer implements support for communication between processes as well as task migration modules for fault tolerance, and the module called Run-time Manager, responsible for making decisions about the resources to be migrated in the presence of a permanent failure in the processing elements. Figure 2.3 presents the software elements to support fault tolerance in MADNESS. The levels presented are:

- Application level, executes the communicating processes;

- Middleware level, implements the communication process layer (*PPN*), the migration process, and the run-time manager;

- Local Operating System, provides basic functionalities such as process management (process creation/deletion, setting process priorities) and multitasking capabilities;

The last layer developed is at the hardware level, composed of a self-test module used in fault detection and by the task migration process.

The migration module has as main functions: isolate the processor that presented a permanent fault; notify the run-time manager module that it is running on a fault-free processor to execute the task migration; receive all pending messages and *FIFO* tokens relating to predecessor and successor processors (derived from the *PPN* model); and finally send the task context and *FIFO* channels to the triggered run-time manager.

The migration made by the software infrastructure is limited to migrate only the context of the tasks in the failed processor since the task code is loaded on all processors in the system. Figure 2.4 shows the proposed architecture of the self-test module responsible for detecting the permanent faults and signalize to the task migration module to start the process. The task migration hardware disables access to the data and instructions memories of the faulty processing element. However, the *DMA* module has access to the data and instructions memories, enabling to transmit the memory contents even if the *PE* is faulty.

Figure 2.4 – Architecture proposed in the MADNESS project [Meloni et al., 2012].

## 2.4 Yu-Yin Chen et al

Chen et al. [Chen et al., 2017] propose a fault tolerance management in NoCs. The Authors present a Path-Diversity-Aware Fault-Tolerant Routing (*PDA-FTR*) algorithm for NoCs. The *PDA-FTR* combines path adaptiveness and routing path quality to achieve fault-resilient packet delivery (*FPD*) and traffic load distribution. In the proposal, the algorithm uses the *PDA* information and a local buffer occupancy to acquire the Effective Buffer Length (*EBL*) of the routing direction. *EBL* is a router delay measurement, where higher *EBL* implies shorter routing delay. The routing decision made by the proposed routing algorithm sends the packet to a less congested region and away from the faulty region.

The *PDA-FTR* algorithm, based on the Path Diversity (*PD*) information, initially adopts minimal routing paths for packet delivery. However, as minimal routing paths are blocked by faults, *PDA-FTR* employs non-minimal ones to prevent packet congestion in the faulty region. To ensure the absence of deadlocks, the Authors use the non-minimal Odd-Even turn model [Tsai et al., 2013]. If there are two or more routing path candidates, the *PDA-FTR* uses the *EBL* information of each candidate channel to select the better output channel.

The Authors report that to implement the *PDA-FTR*, it is necessary to store the *FPD* (Fault-Location-Based PD) table at every router and the entire *FPD* table in a router. The number of tables entries in a router increases by  $O(k^2)$ , where *k* is the number of routers. This feature compromises scalability, and the computing time and power consumption grow when searching for a specific entry in a large table. To reduce the memory cost, the Authors propose a regional *FPD* table to cover most routing paths for packet transmission while minimizing performance degradation. Due to the data locality, processing elements that often communicate with each other are usually placed in proximity to each other for minimizing the delay in data delivery. Based on this property, a small table can store the most used paths

for making a routing decision with minimal performance degradation when compared to full *FPD* table.

Results show that the router with *PDA-FTR* has an area overhead of 10.77% compared to the baseline design. Compared with the baseline design router, the proposed *PDA-FTR* router has power overhead of 7.04% due to the routing table.

## 2.5 Arezoo Kamran et al.

Kamran et al. [Kamran et al., 2016] propose an autonomous test mechanism for online detection of permanent faults in many-core processors. In this method, several test components are incorporated in the many-core architecture that autonomously and concurrent with the system normal operation, distribute software-based self-test routines among the processing cores, monitor the behavior of the processing cores during the execution of the test routines, detect faulty cores, and make their suppression from the system if possible. To use short idle times of the processing cores, test data is segmented into small pieces, called test snippets. Individual test snippets are distributed among the processing cores and are made accessible to them for a limited period. If a processing core has an idle slot during a period that a test snippet is available, it executes the test snippet, otherwise, it skips execution of that portion of the test. The proposed test mechanism is designed in such a way that it supports skipping of test snippets at the expense of losing test quality, but without any effect on the integrity of the whole test mechanism.

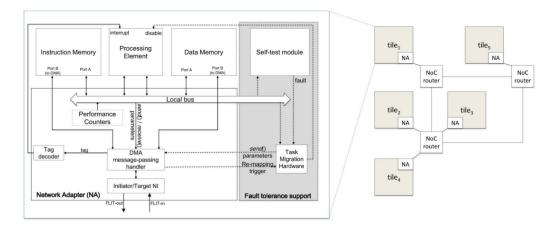

The Authors assume that the many-core processor contains identical nodes, each of which with a processing core, cache blocks, and hardware facilities for communications with other nodes. The test architecture is independent of core communication and uses a dedicated test distribution logic. The processing cores are tested using a non-intrusive software-based self-test approach (*SBST*). In the proposed technique, a small amount of assisting hardware is incorporated in the many-core architecture. These hardware test components distribute *SBST* among the processing cores and detect idle processing cores to switch them to test mode. The *SBST* routines execute, monitoring the behavior of the processing cores during the test.

Figure 2.5 shows the hardware components added near a processing core. Several adjacent processing cores share this additional test component. A local test controller, called *cluster tester*, receives a test routine from a shared global controller called Autonomous Chip Tester (*ACT*), and stores it in a small local buffer (called test-snippet buffer). When this cluster tester is triggered by a command from the *ACT*, it starts monitoring the processing cores. When a processing core becomes idle, the cluster tester disconnects the idle processing core from the communication infrastructure and the memory subsystem and connects it to test-snippet buffer while the other neighboring processing cores are performing their normal

Figure 2.5 – Hardware test components placed near the processing cores [Kamran et al., 2016].

operation. Meanwhile, the disconnected processing core starts executing the test routine execution, the cluster tester captures bus activities of the processing core under-test, and generates a signature. This signature is used later to be compared with the signatures generated by other processing cores or with a golden signature. The responsibility of a cluster tester is to receive test commands and test data from the *ACT*, detect and isolate idle processing cores of the cluster, apply test data to the idle processing cores, and identify and remove faulty processing cores in collaboration with the *ACT*.

Experimental results show that, for a cluster with four Plasma MIPS processing cores, there is a hardware overhead of 3.6%, and for larger cluster sizes, as 32 Plasma MIPS, 1.2%. The authors related that there is no performance overhead because the test executes when the processing cores are in idle status.

## 2.6 Biswajit Bhowmik et al.

Bhowmik et al. [Bhowmik et al., 2016] present a distributed online test mechanism that detects stuck-at faults (*SAF*s) in the *NoC* channels as well as identifies the faulty channels. The proposed test mechanism improves yield and reliability of NoCs at the cost of a small performance degradation. The method focus on detecting stuck-at-0 (*SA*0) and stuck-at-1 (*SA*1) faults in the channels and evaluate their effect on network performance. Each channel consists of control, data, and handshake wires. The authors propose an on-line method for testing wires connecting the router to its core.

The proposal assumes a 16-bit channel. The method starts the application of the test on a  $2 \times 2$  NoC configuring the channels as unidirectional links. Thus, there are 256 wires (8 channels between routers and 8 channels between routers and cores). The proposed test model tests 256 SA0 and 256 SA1 faults. The test technique accounts these faults on data, control, and handshake wires. The method test a channel in this sequence. During the test of a channel, the method keeps the underlying network functional, except the subset of channels under test in a test iteration. In this mode, the network is allowed to transmit application data but must wait at an intermediate router involved in the test. The algorithm uses test packets that contain the test vectors. The packet contents vary depending on the type of wire under test. That means stuck-at faults in data, control, and handshake wires get detected with a specific packet format. To test data wires, test vectors are placed in the payload field of the test packet. After transmitting the test packets, the test response analyzes at receiver core and routers analyzes received test vectors to detect whether data, channel, and wire experiences any SA0 or SA1 fault. If the wire experiences an SA0 or SA1, the test response analyzes receives logic-0 or logic-1 on the wire. The detection ensures the state of the faultiness of a wire. After testing the data-wires, the control and handshake wires are undergone the testing similarly.

The Authors show that during the experiment they observe that the Test Packt Generator takes one clock to generate a test packet. Another clock cycle is used to organize it as a test packet. The packet takes four clocks to reach the neighbor and additional two clocks to analyze the received test sequences. Thus, a channel can be tested in just 11 clocks. Multiple channels in an iteration need this time to be tested. The authors related that the link cover metric in the proposed test mechanism achieves 100%.

## 2.7 Cristiana Bolchini et al.

Bolchini et al. [Bolchini et al., 2013] describe a system with an adaptive level of reliability. The work presents a fault management layer at the *OS* level. This layer has a strategy for dynamically adapting the reliability at run-time. The fault management layer contains three methods: duplication with comparison (*DWC*), triplication (*TMR*), duplication with comparison and re-execution (*DWCR*).

The *DWC* technique guarantees the fault detection property by creating a replica of the application and by comparing the outputs. A checker task is issued at the end of each node of the application's task graph to identify discrepancies in the (intermediate) results.

The *TMR* technique creates two replicas of the original application, resulting in three results to be voted by specific 2-of-3 majority voter that mitigate the possible occurrence of faults. Besides the fault tolerance property, the technique is also able to achieve fault diagnosis features, by identifying the core producing the erroneous mismatching value.

The *DWCR* similarly to the *DWC* technique, the original application is duplicated to have the possibility to detect possible faults by comparing two results using a checker task. If an fault is detected, a third replica of the task is created and executed. In this way, a voter task can identify the correct result. This technique provides the fault tolerance property, and may provide fault diagnosis features, i.e., it can identify the core that caused the fault. This technique is characterized by a limited overhead for achieving the fault tolerance property because the third replica is used and scheduled only after a problem has been detected.

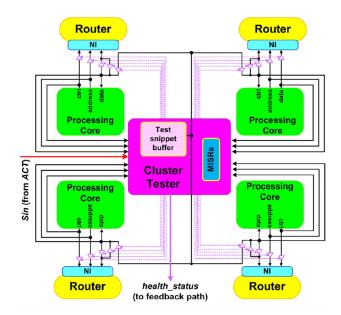

The method uses an observe-decide-act (*ODA*) control loop as shown in Figure 2.6. The *ODA* loop is divided into three stages. The observe phase consists of sensing the status of the system and, in particular, collecting execution data for computing a set of performance and reliability-related metrics. Then, the decide phase is performed by considering the measured metrics and a high-level goal specified as a requirement on the application (as performance and reliability). The knowledge of the goal guides the adaptation engine in making a suitable decision on how to execute the applications. Finally, once the decision has been taken, it is put into practice in the act phase through the actuators, which modify the system's knobs to alter its behavior. The behavior of the system is sensed again in the observed phase, and the control loop is restarted.

Figure 2.6 – The Observe–Decide–Act control loop of [Bolchini et al., 2013].

If the method experiences a high detected fault ratio, *DWCR* is highly disadvantageous compared to *TMR* since it would require a considerable number of tasks to be re-executed. The last knob is the resource activation/deactivation. The fault management techniques, during the execution, the adaptation engine may diagnose a suspected damaged processing core. In this case, the engine can deactivate the processing core to further analyze it using specific diagnosis tasks. Later, if the result of the accurate analysis is negative, the unit can be reactivated and used again for executing the application.

## 2.8 Tsoutsouras et al.

Tsoutsouras et al. [Tsoutsouras et al., 2017] present a run-time resource management framework which can dynamically adapt the system to permanent faults in a selforganized, workload-aware manner. They proposed an organization that allows resource management agents to recovery from a failure electing a new agent to replace the faulty management agent, while workload awareness optimizes the election according to the status of each core.

Figure 2.7 – Overview of SoftRM proposal [Tsoutsouras et al., 2017].

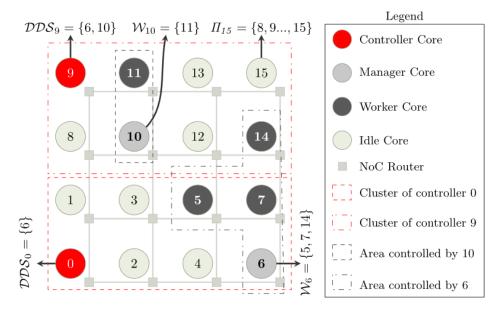

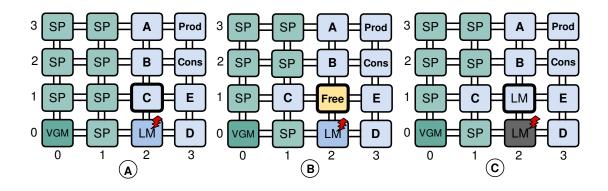

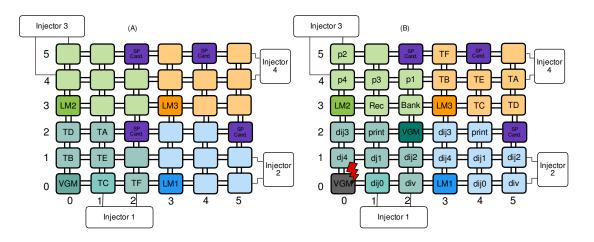

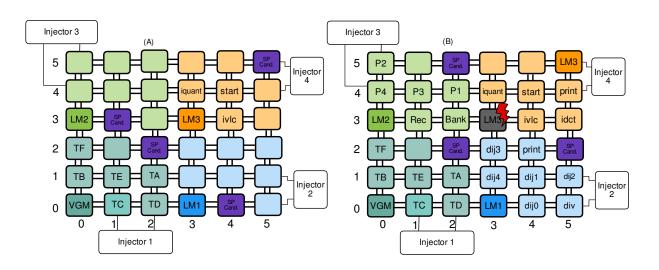

The work is hierarchically organized as shown in Figure 2.7:

- Controller cores (red in Figure 2.7). Responsible for monitoring the system status. There is no central point of system monitoring. Each Controller core is dedicated to its cluster and it is not involved in application management or workload execution. Each cluster area of the system is monitored by a controller core. These clusters are not overlapping and their number and topology is parameterizable and can be defined at the system initialization, but cannot change at run-time;

- Manager cores (dark gray in Figure 2.7). The relationship between a manager core and an application is one to one, meaning that there is one manager core per application. This one to one relationship allows that each manager core adopt different workload allocation schemes, without any resource sharing between applications;

- Worker cores. Execute the applications' tasks. Each worker core has a controller and a manager core. This design choice decouples system monitoring and application management. Cores without a manager and a controller core are considered Idle Cores.

The technique allows fault tolerance recovery to any agent in the system (controller, manager and worker). When a fault is detected, an election occurs to determine which *PE* replace the failed agent. The *PE* with the lowest workload is elected to replace the failed agent. After the election, the state of the system is updated and the failed *PE* is "removed" from the system.

The SoftRM was implemented and evaluated on Intel Single-chip Cloud Computer (*SCC*) *NoC* based many-core system. The *SCC* chip consists of 24 dual-IA-core tiles connected by a 2D-grid on-die network, where each tile contains two P54C cores.

#### 2.9 Suraj Paul et al.

Suraj Paul et al. [Suraj Paul, 2018] present a fault-tolerant resource allocation strategy to mitigate the effect of permanent faults on processors, targeting mixed critical applications. The goal is to select a suitable fault tolerance strategy to mitigate the effect of processor failure at run time with minimum degradation in the performance of the executing applications.

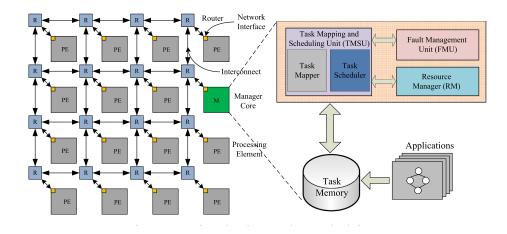

Figure 2.8 presents the system model. A special purpose *PE* hosts the real-time operating system (*RTOS*), and it is referred as Manager Core. The work assumes that such PE acting as Manager Core is reliable and faulty-free. The Manager Core executes task allocation. When a user submits an application to the system, its tasks are stored in the Task Memory. The status of every PE, i.e., faulty/non-faulty, is updated in the resource manager. The Task Mapping and Scheduling Unit (*TMSU*) has two sub-units, Task Mapper (*TM*) and Task Scheduler (*TS*). The allocation algorithm is present in *TM*, which is executed at runtime for assignment of tasks to different available PEs. *TS* schedules the allocated tasks depending on their timing characteristics and criticality.

Figure 2.8 – A Overview of Network-on-Chip (NoC) architecture with multiple cores [Suraj Paul, 2018].

Figure 2.9 – Fault Tolerance using replica tasks [Suraj Paul, 2018].

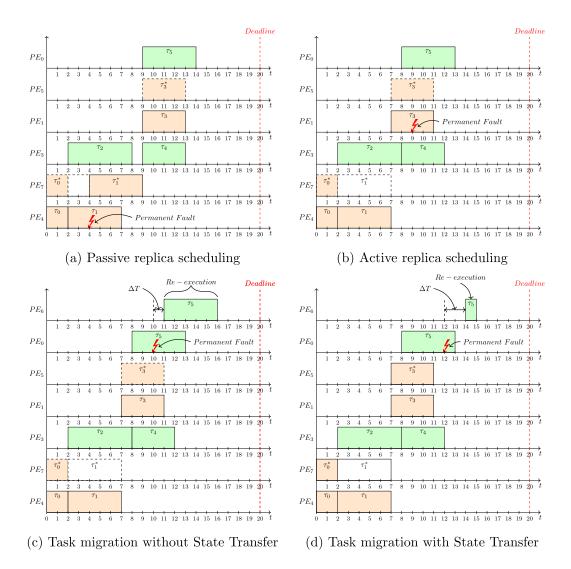

Figure 2.9 presents four different scenarios using the proposed fault-tolerant algorithm. Note the  $\tau 0$ ,  $\tau 1$  and  $\tau 3$  are critical tasks, so a replica from these tasks are created in different PEs.

- Passive replica scheduling Figure 2.9(a). In this scenario, *PE*<sub>4</sub> became faulty at time t=4.

To overcome the effect of this fault on executing task τ1, its passive replica, τ1\* allocated on *PE*<sub>7</sub>, is scheduled.

- Active replica scheduling Figure 2.9(b). A permanent fault affects the execution of task  $\tau$ 3 mapped on *PE*<sub>1</sub> at t = 9. Since this is a critical task with a low slack time, the replica task  $\tau$ 3\* is already scheduled concurrently with  $\tau$ 3, which tolerates failure of *PE*<sub>1</sub>.

- Task migration without State Transfer Figure 2.9(c).  $PE_0$  is assumed to become faulty at t = 10, while executing task  $\tau$ 5. As the fault occurred close to the start time of the task, the proposed fault mitigation policy re-executes the task on an alternative PE,  $PE_6$ .

- Task migration with State Transfer – Figure 2.9(d).  $PE_0$  fails at t = 12. A different fault tolerant strategy is adopted, which helps to complete the task within its deadline. It can be seen that in this case the fault occurs close to the task  $\tau$ 5 deadline. Therefore, state transfer policy is used to recover from fault. Here, the state of the task  $\tau$ 5 consisting of both code and data is transferred to the nearest available  $PE_6$  and the task resumes its execution.

The fault-tolerance method effectiveness of dynamic mapping and scheduling algorithm was implemented on a simulator developed in C++ and used in ORION 3.0. Scalability, QoS performance, communication latency and communication energy was evaluated using the ORION 3.0 model. The proposed algorithm uses an unified mapping and scheduling strategy that gives an energy aware resource allocation in both fault-free and faulty scenarios.

## 2.10 Domingues et al.

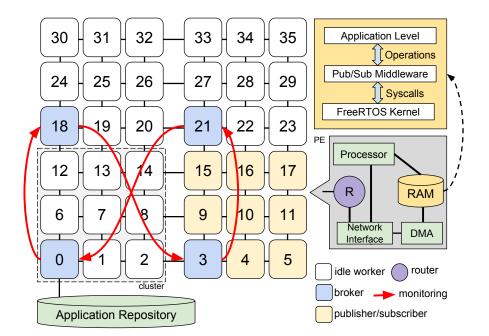

[Domingues et al., 2018] propose a system management technique targeting communication between PEs. The Authors proposer a lightweight fault recovery mechanism for brokers of a publish-subscribe middleware for MPSoCs. The proposed approach uses the existing brokers to backup sensitive data of its neighbor brokers, which provides high availability to the system because when a fault is detected in a broker's processor, its neighbor broker promptly assumes the responsibility of managing the applications of the faulty broker. This broker replacement is entirely transparent to the application level.

Figure 2.10 illustrates a case study using a 6x6 NoC-based MPSoC, with 3x3 clusters. The proposed fault recovery approach relies on a 3-stage protocol consisting of monitoring, cluster recovery and broker recovery phases. The arrows in the figure indicate that the broker at the end of the arrow (called primary broker) is monitored by the broker at the start of the arrow (called secondary broker). This ring topology is reconfigured in the presence of a faulty broker.

The broker fault tolerante feature has the following configurations that must be defined at design-time: (a) the time span between keepalive requests (30,000 clock cycles in the performed experiments); (b) the number of unanswered keepalive requests to consider the broker as faulty (3 in performed experiments).

The MPSoC hardware infrastructure was described using OVPSIM APIs by Imperas, which provides an instruction accurate simulation framework. The kernel software was implemented in C programming language and the middleware software using the C++ programming language.

Figure 2.10 – A 6x6 platform with 3x3 clusters configuration [Domingues et al., 2018].

The results presents the broker recovery time (*BRT*) is in average 32,000 clock cycles. Results showed the approach had a minimal resource overhead for different fault insertion setups.

## 2.11 Silveira et al.

[Silveira et al., 2016] proposes a technique that employs the preprocessing of fault scenarios based on forecasting fault tendencies, which is performed with a fault threshold circuit operating in accordance with high-level software.

The work focuses in a reconfigurable fault-tolerant system for irregular networks that requires the follow mechanisms for (i) fault detection and diagnosis; (ii) fault recognition reporting; (iii) deadlock-free routing computation; and (iv) routing reconfiguration (e.g., routing tables and auxiliary circuits).

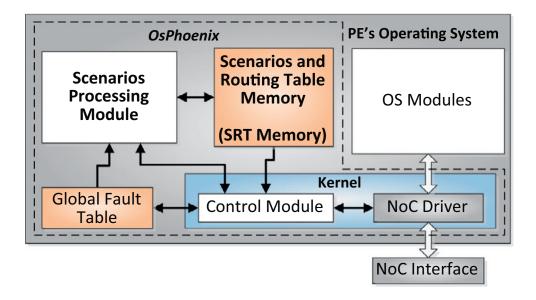

The OsPhoenix's Kernel contais (Figure 2.11): (*i*) the Control Module that manages the fault-tolerant mechanism; (*ii*) the NoC Driver. The Global Fault Table is a module that stores the status of fault tendency for all the NoC links. The Control Module update the Global Fault Table and synchronize the OsPhoenix knowledge with all the PEs. The Scenarios Processing Module is responsible to compute the routing tables managed by the Control Module using the information provided from the Global Fault Table. When a new routing path is discovery it is stored and can be transmitted to the HwPhoenix.

The Authors related that the preprocessed scenarios reduces the time that the NoC is halted. The amount of scenarios grows exponentially with the quantity of faults.

Figure 2.11 – Block diagram of the OsPhoenix architecture [Silveira et al., 2016].

That requires and overhead of area to compute all scenarios. To minimize this problem the work proposes a differential treatment for static and transient faults, an incremental processing of fault scenarios and dissimilarity approach.

## 2.12 Related Work Analysis

Table 2.1 summarizes the reviewed works according to the classification chosen for system management and fault-tolerance comparison. The first column contains the Author and reference. The second column shows the constraints applied to the system, which is management or fault-tolerance. The third column presents the architecture (homogeneous, heterogeneous or only *NoC*) and the core counting given by the number of processor elements or the *NoC* size. The fourth column is the method or technique main goals under the constraint (second column). The fifth column lists the techniques used to control the system according to the Authors definitions. The last column presents the experimental setup used by the Authors and the abstraction level of the system modeling which the results are produced according to the following standard: (*i*) cycle-accurate simulation, only the execution time result is exact, and the others are estimated; (*ii*) *FPGA* prototyping, cycle-accurate simulation for *FPGA* devices.

The literature presents distinct management and fault-tolerance approaches for many-core systems that can be applied to the PE modules. According to the Table 2.1, several techniques are used to manage the system with different goals, as power, resources,

and performance. Fault-tolerance may be applied at different levels, as routing-algorithm, link level, processor level, system level.

The literature presents a rich fault tolerance and management approaches for *MCSoCs*. However solutions that encompass a fault tolerance focused on the system management are scarce. [Tsoutsouras et al., 2017] is the work that most similar with this Thesis proposal. The main difference is that the [Tsoutsouras et al., 2017] implemented the manager recovery in different hierarchical levels. They have tree levels of management and recover, the first level is the replacement of the Controller cluster. The second level is the recovery (PE that execute an task). To execute the recovery method in [Tsoutsouras et al., 2017] they have a communication protocol to update and leave the system in a safe state. In this work we assume that the memory is protected, similar to [Meloni et al., 2012], and a hardware module in the fault manager handle the migration of data and contents to a health PE.

The proposal made in this Thesis includes fault tolerance techniques at the *MCSoC* management level, including the local management in the clusters and the global system management (Chapter 5). Fault tolerance is also proposed for the admission of new applications in the *MCSoC*, through the redundancy of the links with external devices, as well as redundancy with external devices (Chapter 6). Thus, the proposal is original and advances the state-of-the-art in fault tolerance for MCSoCs, through the proposition of high-level techniques, given that low-level techniques (router and processor) are mature in the literature.

| Author                        | Design Constraint                                        | Architecture<br># of cores                 | Design Goals                                        | Techniques                                                | Modelling<br>(Exp. Setup tools)                                      |

|-------------------------------|----------------------------------------------------------|--------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------|

| [Paul et al., 2015]           | Resource Management                                      | Heterogeneous, 16 SPARC<br>LEON3           | Performance                                         | Dynamic load distribution, adaptive shared resources      | FPGA Simulation (Xilinx Virtex-5,<br>XC5VLX330 FPGA)                 |

| [Martins et al.,<br>2016]     | Power Management                                         | Homogeneous, 3x3 to 12x12                  | Scalability and energy efficiency                   | DVFS, clock gating, mapping,<br>migration                 | Cycle-accurate simulation, and<br>low-level analysis (Cadence tools) |

| [Meloni et al., 2012]         | Fault-Tolerance on processor<br>cores                    | Homogeneous 2x2                            | Task remapping                                      | Task migration                                            | FPGA simulation, Design Space<br>Exploration (DSE)                   |

| [Chen et al., 2017]           | Fault-Tolerance on Routing<br>algorithm                  | Only NoC, 8x8                              | Adaptive routing algorithm, balance traffic load    | Path discovery                                            | Cycle-accurate simulation                                            |

| [Kamran et al.,<br>2016]      | Fault-Tolerance on processor<br>cores                    | Homogeneneous, 2 to 32<br>processing cores | CPU faulty detect                                   | Software-based self-test routines                         | Xilinx ISEs WebPACK simulation                                       |

| [Bhowmik et al.,<br>2016]     | Fault-Tolerance on links                                 | Only NoC, 2x2 to 8x8                       | On-line test mechanism that detects stuck-at faults | Packet test                                               | Xilinx 10.1 simulation                                               |

| [Bolchini et al.,<br>2013]    | Management and<br>Fault-Tolerance on processing<br>cores | Homogeneous, 6 to 12<br>processing cores   | Performance, detected faults                        | Application's replicas                                    | Cycle-accurate simulation + ReSP simulation environment              |

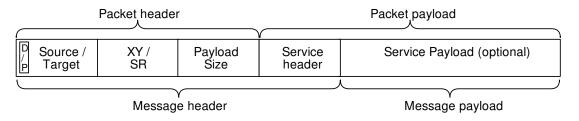

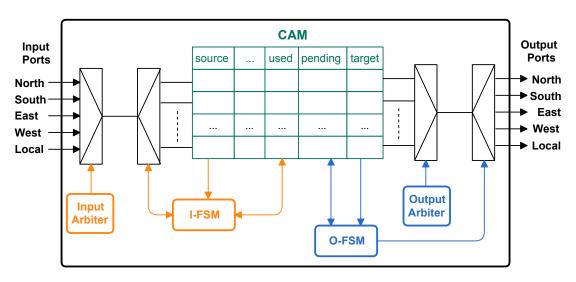

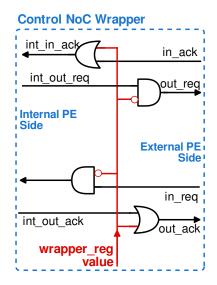

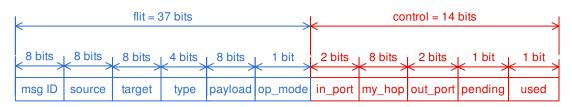

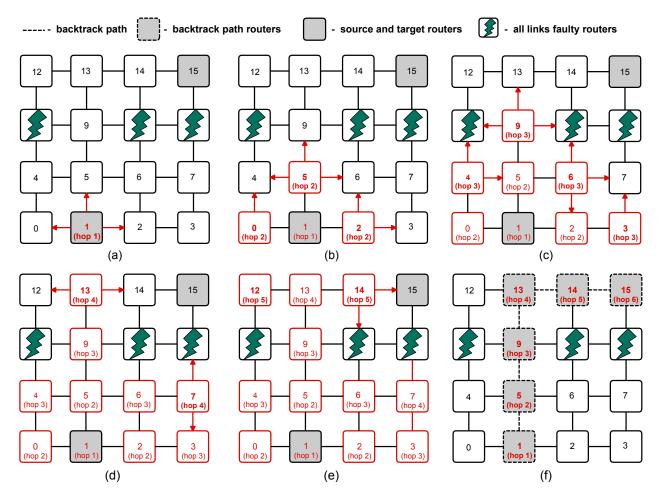

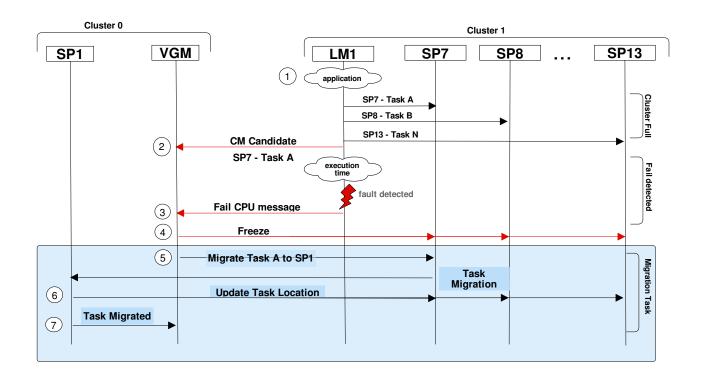

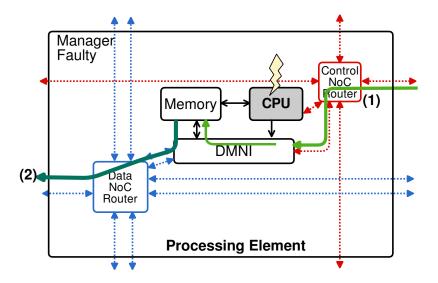

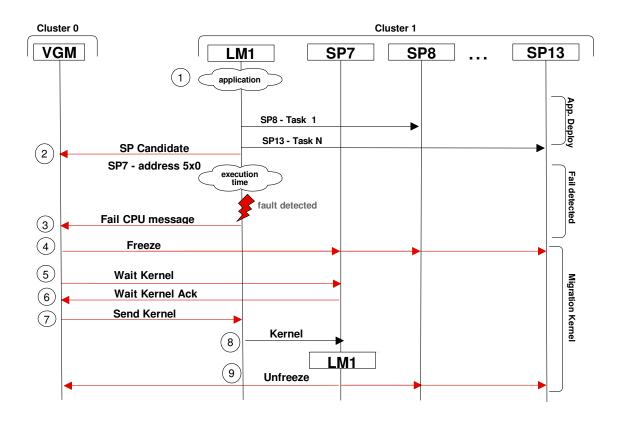

| [Domingues et al.,<br>2018]   | Fault Tolerance in Management<br>Cores                   | Homogeneous 2 to 36                        | Fault Detection and Manager<br>Recovery             | Migration of data contents and<br>cluster reconfiguration | OVPSIM, instruction-accurate<br>simulation                           |