## PONTIFÍCIA UNIVERSIDADE CATÓLICA DO RIO GRANDE DO SUL FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

# TÉCNICAS DE TOLERÂNCIA A FALHAS APLICADAS A REDES INTRA-CHIP

**VINICIUS MORAIS FOCHI**

Dissertação apresentada como requisito parcial à obtenção do grau de Mestre em Ciência da Computação na Pontifícia Universidade Católica do Rio Grande do Sul.

Orientador: Prof. Dr. Fernando Gehm Moraes

## Dados Internacionais de Catalogação na Publicação (CIP)

F652t Fochi, Vinicius Morais

Técnicas de tolerância a falhas aplicadas a redes intra-chip / Vinicius Morais Fochi. – Porto Alegre, 2015.

Diss. (Mestrado) – Fac. de Informática, PUCRS. Orientador: Prof. Fernando Gehm Moraes.

1. Informática. 2. Arquitetura de Computador. 3. Tolerância a Falhas (Informática). 4. Multiprocessadores. I. Moraes, Fernando Gehm. II. Título.

CDD 004.35

Ficha Catalográfica elaborada pelo Setor de Tratamento da Informação da BC-PUCRS

#### Pontifícia Universidade Católica do Rio Grande do Sul FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

## TERMO DE APRESENTAÇÃO DE DISSERTAÇÃO DE MESTRADO

Dissertação intitulada "Técnicas de Tolerância a Falhas Aplicadas a Redes Intra-Chip" apresentada por Vinícius Morais Fochi como parte dos requisitos para obtenção do grau de Mestre em Ciência da Computação, aprovada em 13/03/2015 pela Comissão Examinadora:

| Terundo Colm loras                               |             |

|--------------------------------------------------|-------------|

| Prof. Dr. Fernando Gehm Moraes-                  | PPGCC/PUCRS |

| Orientador                                       |             |

|                                                  |             |

|                                                  |             |

| 1                                                |             |

| My                                               |             |

| Prof. Dr. Alexandre de Morais Amory-             | PPGCC/PUCRS |

|                                                  |             |

|                                                  |             |

|                                                  |             |

| Fuande gues de que.                              |             |

| Profa. Dra. Fernanda Gusmão de Lima Kastensmidt- | UFRGS       |

|                                                  |             |

|                                                  |             |

Homologada em $\frac{24}{105}$ , conforme Ata No.  $\frac{908}{100}$ ... pela Comissão Coordenadora.

Prof. Dr. Luiz Gustavo Leão Fernandes Coordenador.

**Campus Central**

Av. Ipiranga, 6681 – P32– sala 507 – CEP: 90619-900 Fone: (51) 3320-3611 – Fax (51) 3320–3621

E-mail: ppgcc@pucrs.br

www.pucrs.br/facin/pos

#### **AGRADECIMENTOS**

Gostaria de agradecer as pessoas que realmente tiveram influência sobre o desenvolvimento desta dissertação e do meu Mestrado. Gostaria de dedicar esta conquista aos meus pais, José Jorge Fochi que me apoiou a continuar estudando, Rosi Morais Fochi e a minha irmã Cristina.

Ao Professor Fernando Moraes, por aceitar o imenso desafio de me orientar. Muito obrigado por manter reuniões semanais, me obrigando assim a trabalhar intensamente para não perder o foco no desenvolvimento do trabalho. Obrigado por todo o conhecimento transmitido e por sempre acreditar no nosso trabalho. Por ter compartilhado seu tempo e conhecimento para que a realização deste trabalho. Sou muito grato por me aceitar como aluno de mestrado.

Agradeço a todos os professores do PPGCC pela transmissão de seus conhecimentos. Aos empregados da PPGCC pela dedicação em nos manter sempre informados dos prazos e burocracias. Um agradecimento especial ao Professor Alexandre de Morais Amory, que enriqueceu esta dissertação em suas avaliações. Aos colegas que me ajudaram durante a jornada do mestrado: Samir, Guedes, Madalozzo, Castilhos, Ruaro, L.Heck, Matheus, Wachter, Augusto e a todos os demais: obrigado pela ajuda! E a Dell por ter possibilitado e financiado esta pesquisa.

### TÉCNICAS DE TOLERÂNCIA A FALHAS APLICADAS A REDES INTRA-CHIP

#### **RESUMO**

O contínuo desenvolvimento na tecnologia de transistores possibilitou que centenas de processadores trabalhassem interconectados por NoCs (network-on-chip). A nanotecnologia permitiu o desenvolvimento de complexos sistemas, porém a vulnerabilidade a falhas também aumentou. A literatura apresenta soluções parciais para o tema de tolerância a falhas, tendo como alvo partes do sistema. Uma importante lacuna na literatura é um método integrado para detecção de falhas do nível do roteador até a correta execução das aplicações em MPSoC reais. O objetivo principal desta dissertação é apresentar um método com tolerância a falhas da camada física até a camada de transporte. O MPSoC é modelado em nível de RTL, usando VHDL.

O presente trabalho propõe técnicas de tolerância a falhas aplicadas a redes intrachip. São estudadas técnicas de tolerância a falhas em nível sistêmico, nível do roteador, nível de enlace e algoritmos de roteamento tolerante a falhas. Este trabalho apresenta a pesquisa e o desenvolvimento de duas técnicas: (i) protocolos para permitir a correta transmissão dos dados com degradação parcial do enlace, de forma a permitir que o roteador opere mesmo com canais físicos falhos; (ii) método de teste e recuperação do roteador. O modelo de falhas utilizado nesta Dissertação é de falhas permanentes e transientes.

Para avaliar as técnicas propostas, foi utilizada a plataforma HeMPS, juntamente com uma campanha de injeção de falhas onde até cinco falhas aleatórias foram injetadas nos canais de comunicação entre os roteadores simultaneamente em cada cenário. Foram utilizadas duas aplicações para avaliar as técnicas: codificador MPEG e uma aplicação sintética, com um total de 2,000 cenários simulados. Os resultados demonstram a efetividade da proposta, com a maioria dos cenários executando corretamente com roteadores operando em modo degradado, com um impacto no tempo de execução abaixo de 1% e um aumente do área de 30% no roteador.

**Palavras-Chave**: MPSoC, NoC, HeMPS, detecção de falhas, degradação parcial do enlace, teste e recuperação de falhas.

#### FAULT TOLERANCE TECHNIQUES APPLIED TO NETWORKS ON CHIP

#### **ABSTRACT**

The continuous development of the transistor technology has enabled hundreds of processors to work interconnected by a NoC (network-on-chip). Nanotechnology has enabled the development of complex systems, however, fault vulnerability also increased. The literature presents partial solutions for fault tolerance issues, targeting parts of the system. An important gap in the literature is an integrated method from the router-level fault detection to the correct execution of applications in the MPSoC. The main goal of this dissertation is to present a fault-tolerant method from the physical layer to the transport layer. The MPSoC is modeled at the RTL level using VHDL.

This work proposes fault tolerance techniques applied to intra-chip networks. Related work on fault tolerance at a systemic level, router level, link level and routing algorithms are studied. This work presents the research and development of two techniques: (i) protocols to enable the correct communication between task with partial degradation of the link enabling the router to operate even with faulted physical channels; (ii) test recovery method and of the router. This Dissertation considers permanent and transient faults.

The HeMPS platform is the reference platform to evaluate the proposed techniques, together with a fault injection campaign where up to five random failures were injected simultaneously at each simulated scenario. Two applications were used to evaluate the proposed techniques, MPEG encoder and a synthetic application, resulting in 2,000 simulated scenarios. The results demonstrated the effectiveness of the proposal, with most scenarios running correctly with routers operating in degraded mode, with an impact on the execution time below 1%, with a router area overhead around 30%.

**Keywords:** MPSoC, NoC, HeMPS, fault detection, partial degradation of the link, testing and fault recovery.

## **LISTA DE FIGURAS**

| Figura 1 – Curva de envelhecimento do circuito [JHA03]                                                                                                     | 19   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figura 2 – Modelo da arquitetura proposta no Projeto MADNESS [MEL12].                                                                                      | 22   |

| Figura 3 – Arquitetura dos roteadores e suas interconexões incluindo os sinais de controle e os canais bidirecionais [TSA11].                              | 25   |

| Figura 4 – Arquitetura do roteador da Vicis [FIC09].                                                                                                       | 26   |

| Figura 5 – Exemplo de <i>port swapping</i> [FIC09]                                                                                                         | 26   |

| Figura 6 – FIFO de entrada (a) original (b) modelo proposto [CON09]                                                                                        | 28   |

| Figura 7 – Códigos de Hamming nos enlaces da NoC. E – Codificação, D – Decodificação [CON09]                                                               | 28   |

| Figura 8 – Diagrama de blocos do roteador ParlS [VEI10]                                                                                                    | 30   |

| Figura 9 – Enlace da rede SoCIN incluindo os circuitos e os sinais para a técnica de paridade [VEI10].                                                     | 31   |

| Figura 10 – Enlace da rede SoCIN incluindo os circuitos e sinais para a técnica de CRC [VEI10                                                              | ].31 |

| Figura 11 – Interface entre uma porta de saída e uma porta de entrada dos roteadores, com adição dos sinais de crc_in, crc_out, erro_in e erro_out [SIL10] | 32   |

| Figura 12 – Interface entre dois roteadores de uma rede com Hamming nos enlaces [SIL10]                                                                    | 33   |

| Figura 13 - Diagrama simplificado de uma rede com Hamming na origem [SIL10]                                                                                | 34   |

| Figura 14 – Demonstração do método proposto por [WAC13] em uma NoC 4x4                                                                                     | 35   |

| Figura 15 – Conexões entre os roteadores e o modulo de roteamento [WAC13]                                                                                  | 36   |

| Figura 16 – Oito diferentes grupos de situações onde ocorre duas falhas simultâneas em uma NoC [VAL11]                                                     | 37   |

| Figura 17 – Caminho obtido através do algoritmo RDR1 em uma rede com 25% de enlaces con falha [VAL11].                                                     |      |

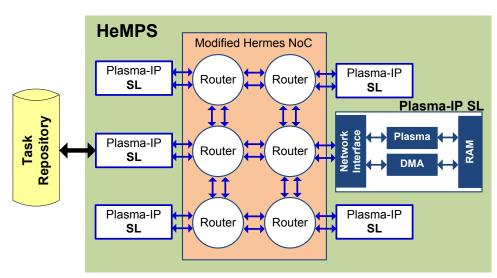

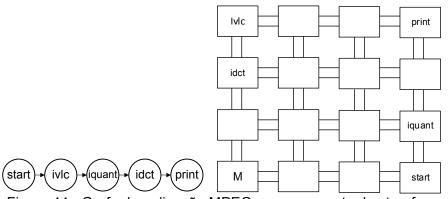

| Figura 18 – Instância do MPSoC HeMPS com 9 elementos de processamento Plasma-IP                                                                            | 41   |

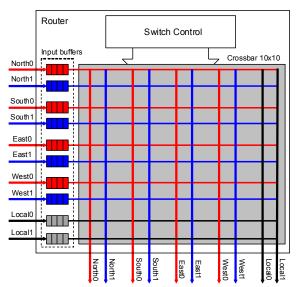

| Figura 19 - Roteator da NoC proposta em [CAR09]                                                                                                            | 42   |

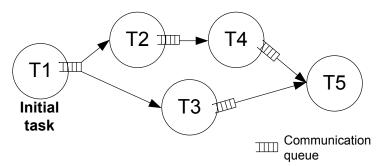

| Figura 20 – Aplicação modelada como um grafo de tarefas, com as filas de comunicação                                                                       | 43   |

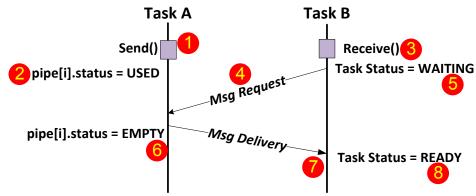

| Figura 21 - Protocolo de comunicação adotado na plataforma de referência                                                                                   | 44   |

| Figura 22 – Operação do método de roteamento proposto em [WAC12]                                                                                           | 46   |

| Figura 23 – Proposta de arquitetura para roteador com tolerância a falhas, para uma porta de entrada e uma porta de saída                                  | 47   |

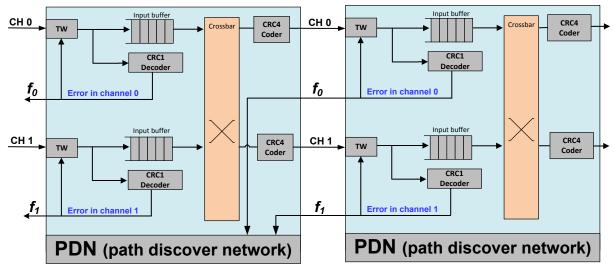

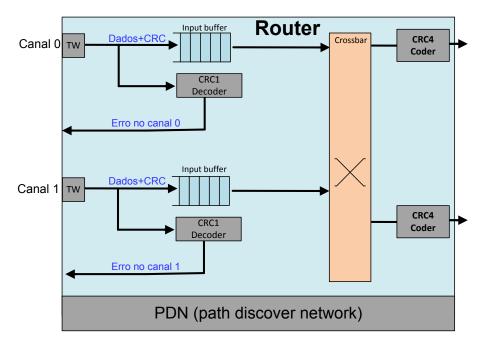

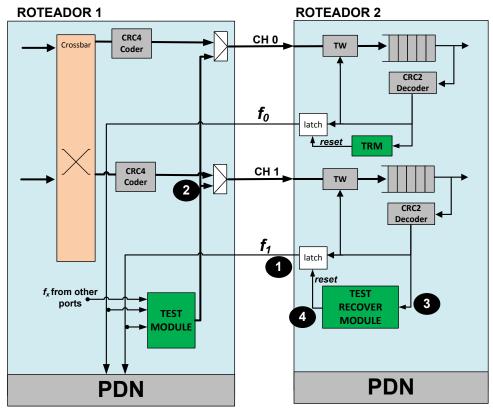

| Figura 24 - Arquitetura do roteador, com os módulos de decodificação e codificação de CRC                                                                  | 49   |

| Figura 25 - Arquitetura da célula de <i>test wrapper</i> [WAC12].                                                                                          | 50   |

| Figura 26 – Células de isolação adicionadas às portas de entrada do roteador para isolar as por falhas.                                         |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figura 27 - Arquitetura do roteador sob avaliação, com decodificares nas portas de entrada                                                      | .51 |

| Figura 28 - Procedimento de detecção e reenvio de pacote em caso de falha em um canal enlac                                                     |     |

| Figura 29 - Pseudocódigo da função para reenviar pacotes usando XY                                                                              | .54 |

| Figura 30 - Pseudocódigo da função para reenviar pacotes usando roteamento na origem                                                            | .55 |

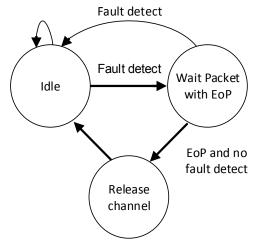

| Figura 31 - Protocolo de comunicação tolerante a falhas, com roteador operando em modo degradado e computação de um novo caminho [FOC15]        | .56 |

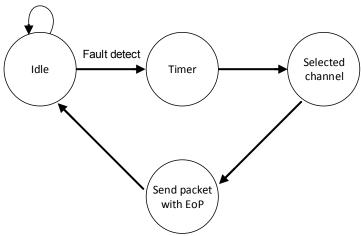

| Figura 32 - Máquina de estado do módulo TM.                                                                                                     | .58 |

| Figura 33 - Pacote de teste utilizado para verificar a integridade do canal.                                                                    | .58 |

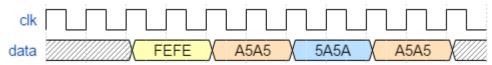

| Figura 34 – Maquina de estado do módulo TRM                                                                                                     | .59 |

| Figura 35 - Módulos de teste e recuperação para detectar falhas transientes. Para simplificar apenas o módulo CRC 2 está presente.              | .59 |

| Figura 36 - Arquivo que indica quais sinais onde serão injetadas falhas stuck-at                                                                | .60 |

| Figura 37 - Arquivo que indica quais sinais devem ter o valor lógico onde serão injetadas falhas stuck-at, e o tempo em que a falha desaparece. |     |

| Figura 38 - Script <i>fault-inject.do</i> que lê a lista de sinais que devem ter os valores lógicos fixados para simular a injeção de falhas.   |     |

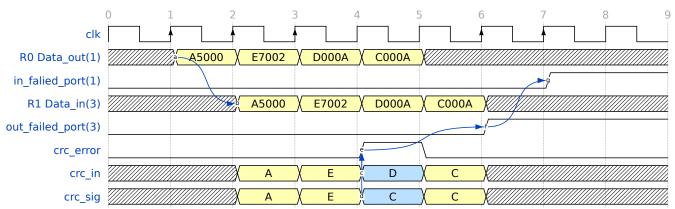

| Figura 39 - Detecção de falha em canal com utilização de CRC.                                                                                   | .62 |

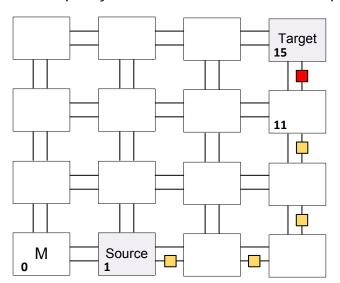

| Figura 40 - Cenário de Avaliação. Mestre localizado no PE 0, tarefa source mapeada no PE 1, e tarefa target mapeada no PE 15.                   |     |

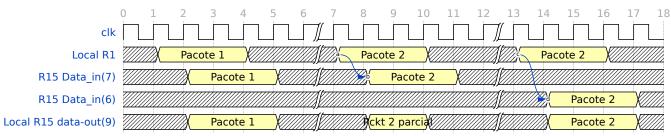

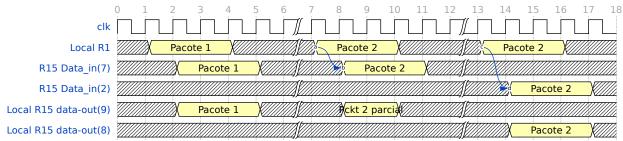

| Figura 41 - Cenário de teste com falha em apenas um canal, como roteador operando em modo degradado                                             |     |

| Figura 42 - Cenário de teste com falha no enlace, utilizando a proposta original de [WAC12]                                                     | .64 |

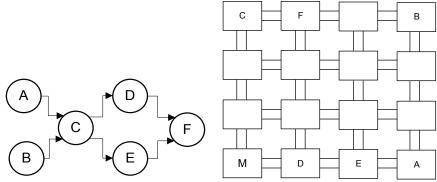

| Figura 43 – Grafo da aplicação sintética e mapeamento das tarefas                                                                               | .65 |

| Figura 44 - Grafo da aplicação MPEG e mapeamento das tarefas                                                                                    | .65 |

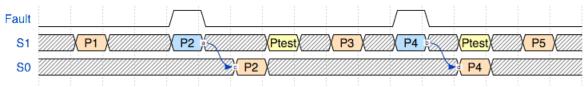

| Figura 45 - Recuperação de falhas transientes.                                                                                                  | .67 |

|                                                                                                                                                 |     |

## **LISTA DE TABELAS**

| Tabela 1 - Tabela comparativa entre as técnicas estudadas                            | 21 |

|--------------------------------------------------------------------------------------|----|

| Tabela 2 - Vista simplificada do modelo OSI e recursos de tolerância a falhas        | 39 |

| Tabela 3 – Descrição dos principais serviços suportados pelo <i>μkernel</i> da HeMPS | 45 |

| Tabela 4 - Análise de resultados obtidos através da campanha de injeção de falhas    | 66 |

| Tabela 5 - Comparativo do consumo de área, entre a MazeNoc [WAC13] e a MazeCRC       | 67 |

#### LISTA DE SIGLAS

BIST Built-in self-test

CRC Cyclic redundancy check

ECC Error Control Coding

FIFO First-In First-Out

FPGA Field Programmable Gate Arrays

FT Fault Tolerant

HeMPS Hermes Multiprocessor System

MIPS Microprocessor without Interlocked Pipeline Stages

MPEG Moving Picture Experts Group

MPI Message Passing Interface

MPSoC Multi-Processor System-on-Chip

NI Network Interface

NoC Network-on-Chip

PE Processing Element

SEU Single Event Upset

SoC System-on-Chip

TMR Triple Module Redundancy

VHDL VHSIC Hardware Description Language VHSIC Very High Speed Integrated Circuit

VLSI Very-Large-Scale integration

## **SUMARIO**

| 1 | IN  | TRO          | DUÇÃO                                                                                     | 17  |

|---|-----|--------------|-------------------------------------------------------------------------------------------|-----|

|   | 1.1 | Def          | inições básicas                                                                           | 17  |

|   | 1.2 | Obj          | etivos do trabalho                                                                        | 19  |

|   | 1.3 | Cor          | ntribuições da Dissertação                                                                | 20  |

|   | 1.4 | Est          | rutura do documento                                                                       | 20  |

| 2 | ES  | TAE          | O-DA-ARTE                                                                                 | 21  |

|   | 2.1 | Téc          | nicas de tolerância a falhas em nível sistêmico                                           | 21  |

|   |     | 1.1<br>pproa | System Adaptivity and Fault-tolerance in NoC-based MPSoCs: the MADNESS Project ach        | 21  |

|   | 2.2 | Téc          | nicas de tolerância a falhas no nível do roteador                                         | 23  |

|   | 2.  | 2.1          | A Fault-Tolerant NoC Scheme Using Bidirectional Channel                                   | 23  |

|   | 2.  | 2.2          | Vicis: A Reliable Network for Unreliable Silicon                                          | 25  |

|   | 2.  | 2.3          | Fault Tolerant Mechanism to Improve Yield in NoCs Using a Reconfigurable Router           | 27  |

|   | 2.  | 2.4          | A Dynamically Adjusting Gracefully Degrading Link-Level Fault-Tolerant Mechanism for N 29 | oCs |

|   | 2.3 | Téc          | nicas de tolerância a falhas no nível de enlace                                           | 30  |

|   | 2.  | 3.1          | Implementation of Techniques for Fault Tolerance in a Network-on-Chip                     | 30  |

|   | 2.  | 3.2          | Implementação e Avaliação de Métodos para Confiabilidade de Redes Intra-Chip              | 32  |

|   | 2.4 | Alg          | oritmos de roteamento tolerante a falhas                                                  | 34  |

|   | 2.  | 4.1          | Topology-Agnostic Fault-Tolerant NoC Routing Method                                       | 34  |

|   | 2.  | 4.2          | A Fault-Tolerant and Hierarchical Routing Algorithm for NoC Architectures                 | 37  |

|   | 2.5 | Cor          | nsiderações finais                                                                        | 38  |

| 3 | PL  |              | FORMA DE REFERÊNCIA – MPSOC HEMPS                                                         |     |

|   | 3.1 |              | SoC HeMPS                                                                                 |     |

|   |     | 1.1          | Plasma-IP                                                                                 |     |

|   |     | 1.2          | NoC Hermes                                                                                |     |

|   |     | 1.3          | Repositório de Tarefas                                                                    |     |

|   | 3.2 |              | municação entre tarefas                                                                   |     |

|   | 3.3 |              | viços de microkernel                                                                      |     |

|   | 3.4 |              | nsiderações sobre o modelo da NoC                                                         |     |

| 4 |     |              | CÇÃO DE FALHAS NO ROTEADOR ATRAVÉS DE CRC                                                 |     |

|   | 4.1 |              | ção de módulos de CRC para detecção de falhas                                             |     |

|   | 4.2 | Adi          | cão de módulos de isolação de portas de entrada com falha                                 | 50  |

|   | 4.3        | Arquitetura desenvolvida para prova de conceito                                                         | .51 |

|---|------------|---------------------------------------------------------------------------------------------------------|-----|

| 5 | PR         | ROTOCOLO DE RECUPERAÇÃO DE FALHAS                                                                       | 52  |

|   | 5.1        | Controle para degradação parcial do enlace                                                              | .53 |

|   | 5.2        | Protocolo em nível de software                                                                          | .54 |

| 6 | MÉ         | ÉTODO DE RECUPERAÇÃO DO ROTEADOR                                                                        | 57  |

| 7 | ΑV         | /ALIAÇÃO                                                                                                | 60  |

|   | 7.1        | Injeção de falhas                                                                                       | .60 |

|   | 7.2        | Utilização da lógica de CRC para detecção de falhas                                                     | .61 |

|   | 7.3        | Avaliação do protocolo de operação em modo degradado                                                    | .62 |

|   | 7.4<br>cam | Avaliação quantitativa do protocolo de operação em modo degradado através de panha de injeção de falhas | .65 |

|   | 7.5        | Avaliação do protocolo de recuperação                                                                   | .66 |

|   | 7.6        | Avaliação do consumo de área                                                                            | .67 |

| 8 | Со         | onclusão e trabalhos futuros                                                                            | 68  |

| R | EFE        | RÊNCIAS                                                                                                 | 69  |

### **INTRODUÇÃO**

O contínuo desenvolvimento na tecnologia da fabricação de transistores gera circuitos integrados (CIs) cada vez menores. Para a efetiva utilização da quantidade de transistores que podem ser fabricados em um mesmo CI, a utilização de módulos de propriedade intelectual (IP) tem-se tornado um método padrão no projeto destes circuitos. A solução mais comumente utilizada para interconectar os diversos módulos IP são as arquiteturas de barramento, tanto centralizada como hierárquica.

arquitetura de interconexão, barramento, apresenta limitações Esta de escalabilidade, desempenho e consumo de energia em sistemas computacionais integrados em um único CI, como MPSoCs (multiprocessor system on chip). Dentre as soluções propostas para a interconexão de IPs, destaca-se a utilização de redes intra-chip (network-on-chip - NoC) [BEN02]. NoCs têm por característica a escalabilidade, o que permite que o constante crescimento do atraso nas comunicações. Outra característica é que a dissipação de potência é amenizada devido a suas propriedades físicas (fios mais curtos que os barramentos). A estrutura física de NoCs compreende segmentos de fios (enlaces), interconectados por blocos de roteamento (denominados na literatura por roteadores ou chaves), de forma a prover certo nível de qualidade de serviço (QoS) [BRA90]. Qualidade de serviço em NoC inclui parâmetros de desempenho a serem respeitados, como largura de banda disponível para a comunicação entre IPs, dissipação de potência e confiabilidade.

A redução no tamanho físico dos transistores os torna mais rápidos e com menor consumo de potência. Apesar desta redução parecerem benéficas, a probabilidade de falhas tende a crescer. As interconexões entre os componentes do CI tornam-se relativamente mais longas e mais estreitas, podendo sofrer efeitos como eletro-migração, curto-circuito ou fios aberto. Os transistores por possuírem canal mais curto, também ficaram mais suscetíveis a falhas transientes. Técnicas de projeto visando o baixo consumo podem gerar consequências negativas no correto funcionamento dos CIs. CIs operando com baixa tensão de alimentação são mais vulneráveis a falhas, fazendo com que o circuito sofra perturbações causadas pelas condições de ambiente (e.g. ruídos, SEUs, dentre outros).

Assim, projeto tolerante a falhas assume uma dimensão cada vez maior nas atuais tecnologias nanométricas. Em particular, o presente trabalho tem por *objetivo* estudar técnicas para tolerância a falhas em NoCs.

#### 1.1 Definições básicas

Confiabilidade é definida de acordo com a IEEE [IEE90] como a habilidade do sistema ou do componente de realizar determinada função sob uma determinada condição e por um período específico de tempo. Uma falha no sistema ocorre ou está presente quando o serviço que provê o sistema difere do serviço especificado ou do serviço que deveria ser oferecido.

Existem três tipos de falhas: permanentes, transientes e intermitentes [GRE07].

Falhas permanentes são falhas constantes, como falha no enlace, no roteador ou em um elemento de processamento. Falhas transientes são falhas esporádicas e podem ser geradas por fatores externos como interferência eletromagnética ou por algum ruído/erro do próprio circuito integrado, como *crosstalk*. Falhas intermitentes são ocasionadas por erros em rajada, geralmente se repetem em um mesmo local esporadicamente.

Falhas permanentes são causadas por uma irreversível mudança física no CI. A origem mais comum para esse tipo de falha é um defeito gerado no processo de fabricação. Falhas permanentes podem ocorrer durante toda a vida do circuito, particularmente quando o circuito começa a entrar na zona de envelhecimento. Característica comum a todas as falhas permanentes é que uma vez que a falha foi detectada, ela não irá desaparecer.

Falhas transientes geram um estado temporário de mau funcionamento causado por algum fator externo do ambiente, como radiação, ou um fator interno como ruído proveniente de outra parte do circuito. Falhas transientes não deixam nenhum resíduo no circuito, pois uma vez que o erro termina, o circuito volta a operar normalmente. Uma manifestação comum para erros transientes é a mudança do valor binário em um sinal. A ocorrência de uma falha transiente é tipicamente aleatória e difícil de ser detectada.

Falhas intermitentes são ocasionadas por erros em rajada. Estas falhas geralmente se repetem em um mesmo local, porém não são contínuas como as falhas permanentes. Falhas intermitentes são tipicamente associadas a um circuito instável ou velho, e são ativadas por um fator relacionado ao ambiente como mudança de temperatura ou mudança de voltagem. Elas frequentemente precedem falhas permanentes. Além disso, falhas intermitentes são difíceis de detectar, pois elas podem ocorrer apenas sob uma determinada condição do ambiente ou através de uma combinação especifica de entradas.

Para representar a quantidade de falhas de um sistema ou componente em relação ao tempo é muito utilizada a curva da banheira, conforme ilustrado na Figura 1 [JHA03]. Esta curva contém três zonas distintas. Durante o início da operação de um dado sistema, a curva começa com uma taxa decrescente de falhas, e os circuitos falhos nesta zona devem-se à "mortalidade infantil". Tipicamente na zona da mortalidade infantil as falhas são geradas devido a defeitos de fabricação, como problemas na oxidação ou nas máscaras utilizadas para a litografia. Na zona central da curva temos o tempo de vida útil do circuito. Falhas transientes podem ocorrer aleatoriamente, devido a diversos fatores como mencionado acima. Na parte final da curva temos a zona de envelhecimento. Nesta região a curva de falhas tem um crescimento devido ao final da vida útil do circuito. Falhas nesta região ocorrem devido à própria degradação dos componentes do circuito.

Podemos dizer que um defeito em um sistema eletrônico é diferença entre o hardware implementado e o projeto pretendido. Alguns exemplos típicos de defeitos em circuitos VLSI são:

Defeitos no processo de fabricação: capacitâncias parasitas, rompimento das linhas de metal, variabilidade na dopagem do silício, impurezas na superfície; Infant working life Wearout

Overall curve Random failures

Early failure

Wearout failures

Defeitos relacionados ao tempo: eletromigração, rompimento de dielétrico.

Figura 1 – Curva de envelhecimento do circuito [JHA03].

Time

Tipicamente são utilizadas diversas métricas para detecção e estimativa das falhas no funcionamento de sistemas eletrônicos e componentes. Dentre as técnicas para detecção de falhas, a técnica BIST [JHA03] (Built-In-Self-Test) é frequentemente utilizada. BIST é uma técnica utilizada em tempo de projeto, utilizando hardware adicional no circuito com o objetivo de realizar testes sem a dependência de equipamentos externos.

Para realizar a estimativa de falhas tipicamente são utilizados as seguintes técnicas: MTBF (*Mean-Time-Between-Failures*) ou MTTF (*Mean-Time-To-Failure*) e MTTR (*Mean-Time-To-Repair*). MTBF é o parâmetro utilizado para representar o tempo médio para a próxima falha ocorrer, sendo calculado da seguinte forma:

MTBF = Total do tempo de operação / Número de falhas encontradas

Outra métrica bastante utilizada para a validação em sistemas tolerantes a falhas com capacidade de se reparar/recuperar é o MTTR, definido como:

MTTR = Tempo gasto para realizar o reparo / Número de reparos

Com base nas métricas MTBF e MTTR é possível calcular a disponibilidade do sistema e podendo assim mensurar o impacto de falhas em aplicações:

Disponibilidade = (MTBF / (MTBF + MTTR)) \* 100%

Tradicionalmente são utilizadas técnicas de detecção e correção de erros para proteger os sistemas contra efeitos transientes de mau funcionamento. Porém, os projetistas precisam avaliar o custo de hardware. Mecanismos como redundância e detecção e correção de erros (EDC - error detection and correction) podem exigir um custo adicional de energia, dissipação de potência e aumento de área, podendo inclusive afetar o desempenho do circuito.

#### 1.2 Objetivos do trabalho

A presente Dissertação possui os seguintes objetivos estratégicos e específicos.

#### Objetivos estratégicos:

- Domínio da tecnologia de redes intra-chip (NoC);

- Domínio de técnicas de tolerância a falhas em NoC;

- Implementação de técnicas de tolerância a falhas em NoC permitindo a operação da mesma em presença de falhas.

#### Objetivos específicos:

- Modificação da rede MazeNoC [WAC12] para inclusão de decodificadores e codificadores CRC em alguns pontos do roteador de forma a prover mecanismos de detecção de falhas;

- Integração da MazeNoC-CRC (rede MazeNoC com mecanismos de CRC) com a plataforma HeMPS;

- Domínio de técnicas de injeção de falhas;

- Desenvolver um método de controle para permitir a operação da NoC com a degradação parcial do sistema após detecção de falhas;

- Propor um protocolo de comunicação tolerante a falhas;

- Desenvolver um método de recuperação do sistema após detecção de falhas.

#### 1.3 Contribuições da Dissertação

A presente Dissertação tem por objetivo contribuir no desenvolvimento de duas técnicas de tolerância a falhas para NoCs em projetos de MPSoCs: (i) operação do roteador em modo degradado em caso de detecção de falhas [FOC15]; (ii) recuperação do canal após ser detectado um falha. Ambas as técnicas são transparentes à aplicação final. A técnica de operação do roteador em modo degradado consiste em garantir que o enlace do roteador continue operando mesmo na presença de falha em um dos canais físicos. A técnica de regeneração do canal consiste no envio de um pacote de teste através do canal falho para determinar se o canal sofreu uma falha transiente ou permanente. Caso o pacote de teste seja recebido corretamente o enlace volta a operar normalmente.

#### 1.4 Estrutura do documento

Este documento está organizado como segue. O Capítulo 2 revisa o estado da arte de técnicas de tolerância a falhas abordando técnicas de nível sistêmico, nível de roteador, nível de enlace e algoritmos de roteamento tolerante a falhas. O Capítulo 3 apresenta a plataforma HeMPS, usada como base desse trabalho. O Capítulo 4 apresenta a técnica de detecção de falhas no roteador. O Capítulo 5 apresenta protocolo de recuperação de falhas. O Capítulo 6 apresenta o método de recuperação do roteador. O Capítulo 7 apresenta a avaliação dos resultados. O Capítulo 8 apresenta os trabalhos futuros, sendo seguidas pelas referências bibliográficas.

#### **ESTADO-DA-ARTE**

A estrutura deste Capítulo está dividida conforme os temas de pesquisa relacionados ao trabalho. Na primeira sessão apresenta-se o estado da arte para tolerância a falhas em nível sistêmico. Na segunda sessão têm-se as pesquisas relacionadas à tolerância a falhas em nível de roteador. Na terceira sessão apresenta-se o estado da arte para tolerância a falhas em nível de enlace. Na quarta sessão apresentam-se os trabalhos relacionados a algoritmos de roteamento tolerante a falhas. O Capítulo encerra com uma avaliação crítica sobre os trabalhos revisados.

A Tabela 1 resume os trabalhos analisados nas seções subsequentes.

Tabela 1 - Tabela comparativa entre as técnicas estudadas.

| Técnica                                         | Resumo                                                                                                                                                 |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Algoritmo de remapeamento em tempo de execução. | A proposta envolve diferentes camadas de software e hardware para lidar com tolerância a falhas [MEL12].                                               |

|                                                 | Propõe uma NoC que suporta falhas em muitos componentes de rede, e ainda assim continuar operando corretamente [FIC09].                                |

| Lógica no roteador                              | Sugere um método de tolerância a falhas que utiliza buffers compartilhados entre os enlaces adjacentes quando uma falha no buffer é detectada [CON09]. |

|                                                 | Propõe um método tolerante a falhas com uma degradação proporcional a quantidade de falhas detectadas em um mesmo enlace. [VIT12]                      |

| Lógica no roteador aplicada                     | Técnicas de paridade e de CRC, com a retransmissão de dados em caso de detecção de uma falha [VEI10].                                                  |

| a enlaces                                       | Técnicas de CRC e Hamming para detecção de falhas, com a retransmissão de dados em caso de detecção de uma falha [SIL10].                              |

| Algoritmo de roteamento                         | Técnica de roteamento com foco em falhas permanentes, detectadas durante a execução do sistema [WAC13].                                                |

#### 1.5 Técnicas de tolerância a falhas em nível sistêmico

O objetivo de técnicas de tolerância a falhas em nível sistêmico é prover, tanto em nível de hardware quanto de software, mecanismos que permitam às aplicações recuperarem-se e executarem corretamente em caso de falhas.

## 1.5.1 System Adaptivity and Fault-tolerance in NoC-based MPSoCs: the MADNESS Project Approach

Meloni et al. [MEL12] propõem um sistema adaptativo e tolerante a falhas para MPSoCs baseados em NoC, utilizando métodos aplicados no Projeto MADNESS. O trabalho busca reduzir a perda de desempenho ao utilizar técnicas de remapeamento

dinâmico (migração de tarefas) devido à detecção de falhas em tempo de execução.

Sistemas embarcados atuais necessitam de técnicas adaptativas tolerantes a falhas, pois a carga de trabalho que o sistema necessita tratar não pode ser prevista em tempo de projeto. Novas aplicações podem ser executadas ou necessitam de um tempo de resposta com recursos de energia e processamento limitados. Para isso é necessário realizar um balanceamento da carga de trabalho nos PEs do sistema. O projeto MADNESS pode lidar com essas situações, com técnicas que permitem mudar o mapeamento de uma aplicação em tempo de execução.

A arquitetura do MPSoC considera uma memória distribuída e um modelo de *tile* interconectados a uma NoC. A arquitetura é um modelo personalizado para um número de processadores e uma topologia de rede. Em nível de software foi elaborado uma camada que permite a execução de aplicações utilizando um modelo chamado *Polyhedral Process Network* (PPN). Esse modelo foi escolhido pois permite gerenciar o estado das tarefas das aplicações em tempo de execução. ?

As técnicas de tolerância a falhas foram introduzidas em nível de hardware e software, explorando a técnica de migração de tarefas nos PEs. Quando uma tarefa está mapeada em um PE falho é necessário transferir a tarefa para um PE sem falha, para que a aplicação continue a execução sem interrupção. Primeiramente é detectado o PE falho para que o processo de migração comece. O PE falho é excluído do processo de remapeamento e um hardware no *tile* falho garante o processo de migração. E por fim, a decisão do remapeamento é tomada levando em conta a menor perda de desempenho possível.

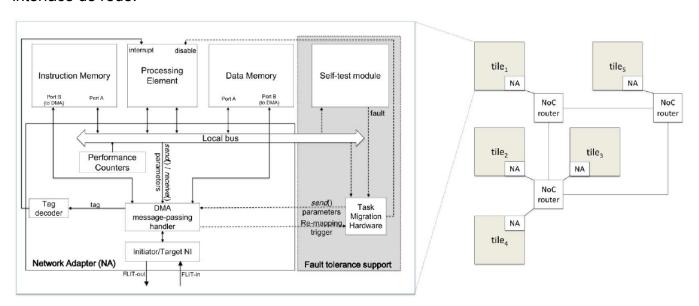

A Figura 2 ilustra a arquitetura proposta no projeto. A NI (*Network Interface*) é conectada com um gerenciador de mensagens com capacidade de DMA. Processadores RISC ou ASIP podem ser integrados utilizando a interface do barramento. A comunicação e a sincronização são gerenciadas através da memória mapeada nos registradores da interface de rede.

Figura 2 – Modelo da arquitetura proposta no Projeto MADNESS [MEL12].

A parte em cinza da Figura 2 representa o circuito adicional que fornece suporte à tolerância a falhas. Em casos em que a aplicação não é critica e um número limitado de erros é aceitável, uma rotina de teste é executada periodicamente em todos os PEs para detectar as falhas permanentes. O módulo de tolerância a falhas verifica o resultado das execuções de uma rotina em software e compara com os resultados previamente calculados. Caso haja alguma inconsistência, um sinal de erro é enviado ao módulo de migração de tarefas. Em casos de aplicações críticas, são utilizadas técnicas de testes em nível de rede. Cada tarefa é replicada em diferentes PE e depois do resultado ser processado, o mesmo é analisado para verificar a integridade do valor. Caso seja detectada uma falha, o PE falho é isolado e a aplicação é migrada para outro PE.

O módulo de hardware de migração de tarefas (TMH – task migration hardware) é usado caso um PE falhe. Ele é responsável por extrair os dados do tile falho. Ele recebe o sinal de falha do módulo de teste e inicia o procedimento para a migração. Uma condição fundamental para a migração de tarefas é que o PE falho não auxilie na migração. Para resolver esse problema o TMH é quem isola o PE falho para não participar da migração.

O projeto MADNESS define as estratégias de remapeamento em tempo de execução em duas classes. Na primeira, analisa-se exaustivamente todos os possíveis cenários de falhas em tempo de projeto, avaliando qual o melhor remapeamento para cada cenário. Com isso, quando uma falha ocorre não é necessário realizar um cálculo para detectar qual o melhor cenário. Contudo, essa abordagem requer o uso de memórias para armazenar tais cenários. A segunda técnica realiza o remapeamento em tempo de execução. O projeto MADNESS utiliza preferencialmente a segunda opção, pois esta requer uma quantidade menor de memória, não requerendo um estudo maior em tempo de projeto, e pode ser utilizado em aplicações que não são conhecidas *a priori*. Entretanto, a técnica executada em tempo de execução pode reduzir o desempenho das aplicações comparado à técnica realizada em tempo de projeto. Os autores relatam uma degradação do sistema em torno de 3% em casos onde foi necessário uma migração de tarefas.

#### 1.6 Técnicas de tolerância a falhas no nível do roteador

O objetivo de técnicas de tolerância a falhas no nível do roteador é prover, em nível de hardware, mecanismos adicionais de recuperação de falhas que permitam ao roteador recuperar-se e executar corretamente em caso de falhas.

#### 1.6.1 A Fault-Tolerant NoC Scheme Using Bidirectional Channel

Tsai et al. [TSA11] propõem uma NoC tolerante a falhas com enlaces bidirecionais. A arquitetura é capaz de suportar falhas transientes e permanentes nos enlaces do roteador. Em uma arquitetura tradicional de uma NoC com tolerância a falhas, quando um enlace falha o pacote é forçado a ser desviado por um caminho válido, fazendo com que tenha um maior custo na transmissão. Contudo, esse caminho válido pode não existir e com a mudança da rota original, pode ser gerado um *deadlock*. Para se encontrar um caminho alternativo algumas regras relacionadas com o algoritmo de roteamento podem ser violadas para encontrar o caminho válido. A proposta da técnica é utilizar uma rede

com canais bidirecionais reconfiguráveis, gerando uma maior flexibilidade para falhas transientes e permanentes.

Algumas técnicas utilizam roteadores e canais adicionais para garantir a confiabilidade da rede, porém isso causa um inevitável aumento no custo da NoC. Outras técnicas utilizadas para evitar *deadlocks* desenvolvem estratégias de roteamento através de desvios de pacote. Porém, esta última técnica requer uma reconfiguração das tabelas de roteamento causando um aumento da latência na transmissão dos pacotes. Essas técnicas são ineficientes para falhas transientes.

NoCs com canais bidirecionais e com largura de banda adaptativa foram propostas recentemente [LAN11] e [CHO09]. Canais bidirecionais suportam reconfiguração em tempo de execução para transmissões que demandam um maior desempenho. Contudo, o potencial de NoCs com canais bidirecionais em relação à confiabilidade não foi completamente explorado e estudado.

Em NoCs tradicionais, os roteadores vizinhos se comunicam com um par de canais unidirecionais, um para transmissão (TX) e outro para recepção (RX). NoCs com canais bidirecionais podem alternar a direção dos canais de transmissão RX e TX utilizando um mecanismo que suporte a mudança conforme a demanda do canal.

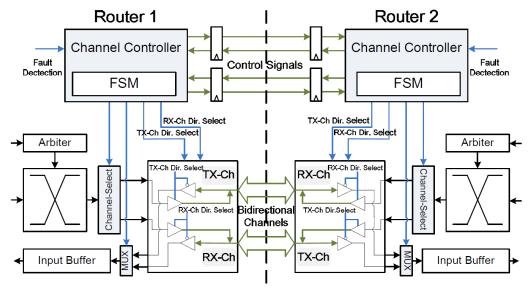

Na Figura 3 podemos observar os dois canais bidirecionais entre os roteadores vizinhos. Também é possível observar o canal adicional de controle para realizar dinamicamente a mudança da direção dos canais bidirecionais sempre que uma falha é detectada. Durante a execução normal dos roteadores, um canal é usado para transmissão e outro para recepção. Quando um canal falha, o canal operacional é reconfigurado para trabalhar de forma bidirecional, fazendo com que o canal opere tanto para recepção quanto para transmissão. No caso de falha em ambos os canais bidirecionais de uma mesma porta (e.g. porta norte), o controle do roteador informa a falha para os roteadores vizinhos para que o algoritmo de roteamento procure por rotas alternativas para aquele destino. Em casos onde a falha é transiente e o canal volte a funcionar ele reconfigura novamente os canais para operar separadamente. O método de recuperação do canal é fora do escopo deste trabalho. A proposta utiliza dois algoritmos de roteamento, ODD-EVEN [CHI00] e o XY, trabalhando em conjunto com os canais bidirecionais.

Os resultados encontrados demonstram que NoCs com canais bidirecionais de tamanho 8x8 apresentam confiabilidade de 90,80% caso tenham sete canais com falha. Combinando a técnica desenvolvida com os algoritmos de roteamento ODD-EVEN e XY foi obtida uma confiabilidade de 99,94% e 99,58% respectivamente. O custo em área adicional foi de 4,07% em relação a uma NoC unidirecional e de 1,86% de consumo de energia adicional.

Figura 3 – Arquitetura dos roteadores e suas interconexões incluindo os sinais de controle e os canais bidirecionais [TSA11].

#### 1.6.2 Vicis: A Reliable Network for Unreliable Silicon

Fick et. al. [FIC09] propõem uma NoC que suporta falhas em muitos componentes de rede e ainda assim continua funcionando corretamente. A rede Vicis utiliza como método a redundância em nível de rede e em nível de roteador para manter o funcionamento do sistema. A detecção da falha de um componente da rede é realizada em tempo de execução utilizando BIST para detectar exatamente qual componente apresenta falha. O trabalho descreve o funcionamento do método em quatro passos: 1) detecção do erro; 2) diagnóstico do erro; 3) reconfiguração do sistema; 4) recuperação do sistema.

Os mecanismos de detecção de erro informam que uma nova falha foi encontrada. Após é realizado um diagnóstico para determinar onde a falha foi detectada. A reconfiguração do sistema desabilita o componente com falha, e determina como será a nova configuração dos componentes funcionais. Por fim, o sistema de recuperação, caso detecte que um componente saiu do estado de falha, para um estado funcional restaura a configuração original do sistema.

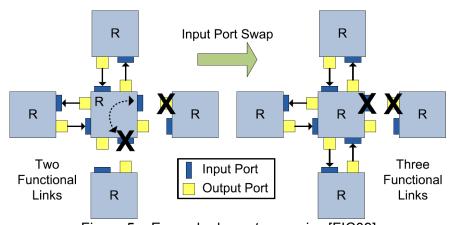

A NoC Vicis trabalha com enlaces bidirecionais, com dois canais físicos por enlace. Cada enlace necessita de duas portas de entrada e duas portas de saída para que o enlace opere corretamente. Caso uma dessas portas falhe, um canal do enlace torna-se indisponível. Neste caso três portas ainda estarão funcionais, possibilitando que elas sejam utilizadas em outro enlace.

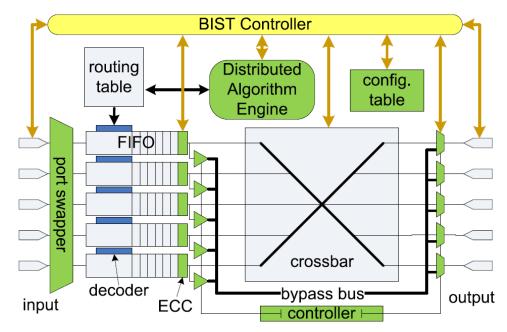

Conforme ilustrado na Figura 4, as portas de entrada do roteador são compostas por FIFOs (*First-in First-out*), e um decodificador. Um *port swapper* é posicionado em frente às FIFOs com o objetivo de alternar qual enlace físico está conectado a cada porta de entrada no roteador. As portas de saída não possuem o *port swapper* com o objetivo de economizar área. Os Autores relatam que como as FIFOS estão ligadas ao crossbar, não há necessidade de incluir um *port swapper* adicional.

Figura 4 – Arquitetura do roteador da Vicis [FIC09].

A Figura 5 ilustra um exemplo de uso do *port swapping*. Na Figura à esquerda apresentam falha a porta sul de entrada do roteador central, e a porta oeste de saída do roteador à direita do roteador central. Nesse estado, apenas as portas oeste e norte do roteador central podem operar corretamente. Na Figura 5, à direita, ilustra-se a configuração após o *port swapping*. Como resultado, três portas estão em funcionamento e apenas à porta leste do roteador central está em estado de falha. O *port swapper* não necessita ser conectado com cada porta de entrada para que seja conectado com cada enlace físico. A configuração da rede Vicis define que a porta local está habilitada para conectar-se a três portas diferentes e os demais enlaces estão habilitados a conectarem-se em duas portas de entrada. Isto resulta em uma maior prioridade para a porta local, garantindo assim o funcionamento desta porta sempre que possível.

Figura 5 – Exemplo de port swapping [FIC09].

Após o algoritmo de *port swapping* terminar o processo, cada roteador e o algoritmo de roteamento são informados sobre quais enlaces são funcionais. O algoritmo de roteamento então realiza a reconfiguração da rede encerrando o processo. Para realizar o roteamento da rede a Vicis utiliza o algoritmo de roteamento proposto por Fick et al. [FICO9a], pois não utiliza canais virtuais e por ter baixo custo de implementação.

Conforme ilustrado na Figura 4, o barramento de *by-pass* em paralelo ao crossbar permite que os *flits* contornem o *crossbar* caso ele apresente em falha. O controlador do *crossbar* é configurado através do BIST para direcionar o tráfego através do *crossbar* ou o contornar utilizando o barramento de *by-pass* caso seja detectado uma falha no *crossbar*. Caso muitos *flits* necessitem usar o barramento de by-pass simultaneamente, então é escolhido um *flit* para ser enviado e os outros aguardam até o próximo ciclo. Os caminhos alternativos permitem que a NoC Vicis mantenha a rede operacional mesmo que múltiplas falhas ocorram no *crossbar*, perdendo desempenho, porém operando corretamente.

Os resultados relatados foram que a NoC Vicis teve um custo de área em torno de 42% superior à rede de referência, sendo considerado pelos Autores um custo aceitável comparado com a NoC NMR (*N-modular-redundancy*), que teve um aumento superior a 100% em área. Quanto à confiabilidade da rede, a NoC Vicis garante 100% de confiabilidade mesmo que apenas 50% dos roteadores continuem funcionando. A NoC Vicis obteve um bom desempenho em deixar os IP's conectados a pelo menos outro IP da rede. Os autores relatam que proposta se mostrou altamente tolerante a falhas de hardware. Cada roteador utiliza BIST para diagnosticar as falhas, e os algoritmos de reconfiguração mantém o roteador operando.

#### 1.6.3 Fault Tolerant Mechanism to Improve Yield in NoCs Using a Reconfigurable Router

Concatto et al. [CON09] propõe um método de tolerância a falhas que utiliza buffers compartilhados entre os enlaces adjacentes quando uma falha em algum buffer é detectada. A técnica utiliza códigos de Hamming e TMR (*Triple Modular Redundancy*) para proteger os dados. O objetivo da proposta é diminuir a latência do sistema e aumentar o tempo de vida do sistema, juntamente com um baixo consumo de energia.

A técnica utiliza um roteador baseado no roteador RASOC, utilizado na rede SOCIN [ZEF03]. SOCIN é uma NoC com topologia malha com roteadores parametrizáveis, que utiliza o algoritmo XY para realizar o roteamento. O RASOC é um roteador com cinco portas bidirecionais (Local, Norte, Sul, Leste e Oeste). O roteador RASOC foi escolhido devido à possibilidade da reconfiguração dos buffers utilizados em cada porta de entrada. Uma porta pode emprestar uma parte ou o buffer inteiro para as portas adjacentes. Para reduzir as interconexões apenas as portas vizinhas de uma dada porta compartilham os buffers. Com isso cada porta tem a disponibilidade de compartilhar três buffers caso seja necessário. Em casos em que o buffer de uma porta esteja cheio, ele pode solicitar o uso dos buffers adjacentes. O método pressupõe que a NoC passe por um teste off-line para detectar e identificar os buffers falhos. Cada roteador tem um flip-flop extra por cada porta de entrada, para informar qual buffer apresenta falha.

A Figura 6 ilustra a porta Sul do roteador. Foram utilizados multiplexadores extras para permitir a reconfiguração dos buffers. Quando apenas uma unidade do buffer falha, o buffer inteiro não é descartado, apenas a unidade falha é isolada e a próxima unidade do buffer é usada no lugar da unidade defeituosa. Cada porta recebe três entradas de dados. Considerando a porta Sul como exemplo: sua própria entrada (din\_S) é conectada com a entrada da porta à direta (din\_E) e com a entrada da porta à esquerda (din\_W), como

ilustrado na Figura 6. Todas as portas de comunicação tem a mesma arquitetura com exceção da porta local que não compartilha seu buffer.

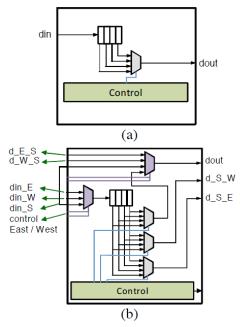

Figura 6 – FIFO de entrada (a) original (b) modelo proposto [CON09].

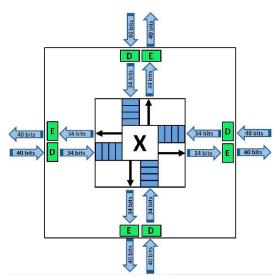

O trabalho proposto tem por objetivo combinar três técnicas de tolerância a falhas permanentes. Cada técnica abrange uma parte do circuito para resultar no menor custo adicional de área e desempenho. Foi utilizado o roteador reconfigurável como solução para os buffers com falha. A técnica de códigos da Hamming protege os enlaces caso ocorra alguma falha que inverta um bit. Conforme ilustrado na Figura 7, o processo de codificação e decodificação ocorre antes do dado entrar no buffer. Foi necessário incluir seis bits adicionais no enlace para o código de Hamming, somado aos trinta e quatro bits (trinta e dois de dados e dois de controle) totalizando quarenta bits. A terceira técnica utilizada para controle da FIFO foi TMR, visto que a FSM que controla a FIFO é muito pequena e tem apenas três estados. A TMR triplica a FSM dando assim uma maior tolerância a falhas para o controle da FIFO.

Figura 7 – Códigos de Hamming nos enlaces da NoC. E – Codificação, D – Decodificação [CON09].

Os resultados descritos pelos Autores foram que combinando as três técnicas citadas, um total de 63% do circuito do roteador da NoC está protegido (enlaces, buffers e o controle). Contudo não foi possível cobrir todas as falhas permanentes no roteador. O *crossbar* e o algoritmo de roteamento não possuem mecanismo de detecção e correção de falhas. O trabalho relata um aumento da área do circuito (172um² de *overhead*) e uma diminuição da frequência de operação, porém o método de reconfiguração manteve o desempenho e reduziu a energia dissipada.

## 1.6.4 A Dynamically Adjusting Gracefully Degrading Link-Level Fault-Tolerant Mechanism for NoCs

Vitkovskiy et. al. [VIT12] propõe um método tolerante a falhas com uma degradação proporcional a quantidade de falhas detectadas em um mesmo enlace. O método é chamado de PFLRM "Partially-faulty link recovery mechanism". O princípio básico do método é uma transmissão multi-ciclo fazendo um deslocamento de flits através dos fios em falha do enlace, conforme um determinado nível de máximo de falhas nos fios. Assim, os fios que estão em falha são ignorados, enquanto o roteador reagrupa os bits deslocados inicialmente no flit. O projeto PFLRM tem um leve aumento de área na arquitetura da NoC e uma pequena mudança no controle de fluxo dos pacotes.

A maior contribuição do PFLRM é lidar com um ambiente com muitas falhas, sem a necessidade de utilizar algoritmos de roteamento adaptativos, visto que o enlace não é completamente desabilitado. Um determinado número de fios falhos pode tornar não mais benéfico continuar utilizando o enlace funcionando parcialmente. Neste ponto o método faz com que o enlace se torne inativo. Em casos onde o enlace é desabilitado a rede pode utilizar um algoritmo de roteamento adaptativo.

O método PFLRM recupera os flits corrompidos atráves de uma PFL (Partially-faulty link) utilizando três etapas:

- 1) Ocorrência de uma falha e a detecção.

- 2a) Geração de um vetor de falha.

- 2b) Calculando a latência para a recuperação.

- 3) Retransmissão dos flits, utilizando o vetor de falha para enviar os flits, ao chegar no roteador adjacente o flit é recuperado.

Todas as três fases são executadas apenas quando uma falha ocorre. Depois que o vetor de falhas é gerado apenas a última fase é necessária, até que eventualmente seja detectado uma nova falha em um fio diferente.

Os resultados mostraram que o mecanismo PFLRM gerou um aumento de área e potência do roteador de 12,08% e 13,83% respectivamente. Os autores relatam que um aumento de área no chip como um todo seria de apenas 3%. Com isso se justificaria o uso do método PFLRM, para sistemas onde é benéfico que a rede mantenha a conectividade em um ambiente propício a muitas falhas.

#### 1.7 Técnicas de tolerância a falhas no nível de enlace

O objetivo de técnicas de tolerância a falhas no nível de enlace é prover, em nível de hardware, mecanismos que permitam que a rede continue trabalhando corretamente mesmo se um enlace parar de funcionar.

#### 1.7.1 Implementation of Techniques for Fault Tolerance in a Network-on-Chip

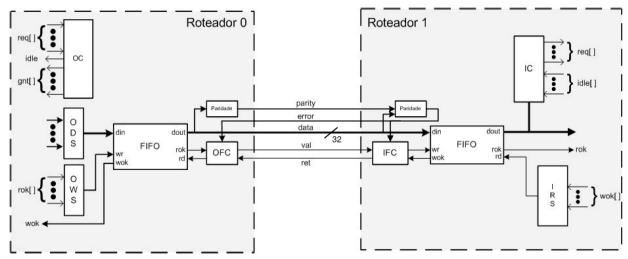

Veiga et. al. [VEI10] propõem duas técnicas para tolerância a falhas transitórias de *crosstalk*. As técnicas desenvolvidas foram de CRC [VEI10] e paridade com retransmissão de dados em caso de detecção de uma falha. As técnicas foram implementadas na rede SoCIN, modificando o bloco de controle de fluxo do roteador ParIS. O objetivo foi proteger os enlaces contra falhas de *crosstalk* nos canais de enlace.

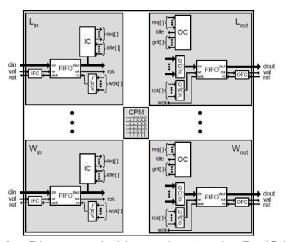

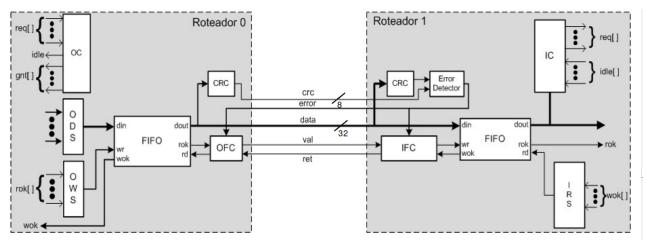

A Figura 8 ilustra o diagrama de blocos do roteador ParlS. O roteador é constituído por um conjunto de módulos e internamente cada módulo é formado por um conjunto de blocos. O alvo do trabalho foram os blocos IFC (*Input Flow Controller*) e o OCF (*Output Flow Controller*). Os respectivos blocos são responsáveis pelo fluxo de entrada e saída de dados do roteador.

Figura 8 – Diagrama de blocos do roteador ParlS [VEI10].

Falhas causadas por *crosstalk* geram uma inversão de bits no canal de dados. Para simular o erro foi utilizado um módulo de injeção de falhas chamado Sabotador que é inserido no canal de dados. O módulo Sabotador monitora os dados transferidos em cada canal da rede e modifica o valor de alguns bits de dados para gerar o efeito de *crosstalk*.

Para realizar a técnica de paridade, foram realizadas alterações nos módulos de entrada e saída do roteador. Foi adicionado um fio de paridade e um fio de sinalização de erro para cada canal. A técnica proposta utiliza um único bit de paridade, que é calculado na saída do bloco OFC (Figura 9). A cada dado transmitido é acrescentado um bit de modo que o total de bits em '1' seja par. Foi desenvolvido um circuito especifico para o cálculo de paridade, sendo realizado sobre os bits de dados. Quando o IFC recebe os bits de dados e o bit de paridade, é realizado o cálculo de paridade no canal de entrada e comparado com o bit de paridade recebido. Se o valor calculado for o mesmo, o dado é

considerado correto e é enviada uma sinalização de sucesso para o transmissor utilizando o fio *ret*, conforme ilustrado na Figura 9. Caso contrário, o receptor envia uma mensagem de erro através do fio *error*, solicitando uma retransmissão do dado. Caso ocorra *crosstalk* e um número par de bits for invertido, a técnica não consegue identificar o erro.

Figura 9 – Enlace da rede SoCIN incluindo os circuitos e os sinais para a técnica de paridade [VEI10].

A Figura 10 ilustra a modificação realizada nos módulos para desenvolver a técnica de CRC. Para desenvolver a técnica de CRC foi necessário modificar os módulos de entrada e saída, de forma semelhante à técnica de paridade. Foi acrescido um fio de CRC para cada quatro fios de dados e um fio de sinalização de erro. Foi necessário criar um componente de codificação do CRC no módulo de saída e um componente de decodificação no módulo de entrada. O módulo de saída é responsável por enviar os dados e gerar o CRC a ser enviado para o roteador destino. O modulo de entrada por sua vez recebe o código gerado e os dados enviados, comparando os bits de CRC recebidos com o CRC gerados localmente. Se os bits forem iguais então o dado é computado. Caso contrário, o receptor envia um sinal de erro ao transmissor para que seja feita a retransmissão do dado. Uma vez detectado o erro, o decodificador CRC desabilita o sinal de escrita na FIFO para que o dado não seja consumido.

Figura 10 – Enlace da rede SoCIN incluindo os circuitos e sinais para a técnica de CRC [VEI10].

Os Autores relatam que as técnicas de paridade e CRC geram um custo adicional

de fios no enlace. Para ambas técnicas é necessária a inclusão de um fio (*error*) para sinalizar o erro detectado. Na técnica de paridade, além do fio *error* é também necessário um segundo fio para a sinalização de paridade (*parity*), com um custo adicional de área igual a 6,25%. Na técnica de CRC o custo foi de 28,125% pois é necessário incluir um fio de controle a cada quatro fios de dados. As técnicas desenvolvidas têm por objetivo apenas detectar o erro, e solicitar um reenvio dos dados, nenhuma das técnicas tem mecanismos de correção do erro.

#### 1.7.2 Implementação e Avaliação de Métodos para Confiabilidade de Redes Intra-Chip

Silva [SIL10] propõe duas técnicas de tolerância a falhas para detectar e corrigir falhas transientes em sistemas expostos aos efeitos de crosstalk. Crosstalk é caracterizado pela interferência em um sinal resultante da atividade de chaveamento em linhas vizinhas. O Autor desenvolveu as técnicas de CRC/Hamming nos enlaces e CRC/Hamming na origem.

O ambiente de desenvolvimento das técnicas foi a rede Hermes [CAR09]. A rede Hermes é uma rede parametrizável, modelada em VHDL, em nível RTL. O algoritmo de roteamento escolhido foi o XY e o tamanho básico da rede foi de 8x8 com a topologia do tipo malha bidirecional.

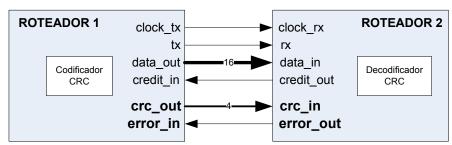

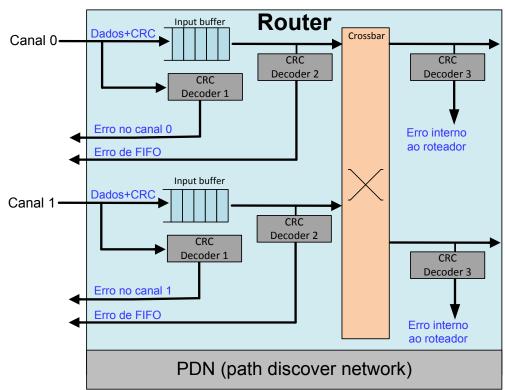

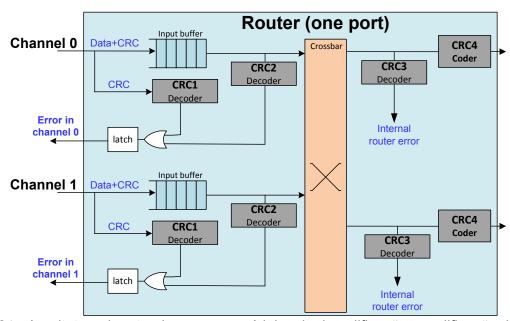

A Figura 11 ilustra a interface de comunicação entre dois roteadores. O codificador CRC é adicionado em cada porta de saída do roteador, e o decodificador CRC é inserido em cada porta de entrada. Conforme ilustrado na Figura 11, quando o roteador 1 deseja enviar um dado para o roteador 2, o Codificador CRC gera a codificação em função do dado a ser enviado em data\_out. O código gerado é enviado através do sinal crc\_out. Ao receber o dado, o Roteador 2 calcula o CRC para o dado recebido e compara com o código CRC recebido em crc\_in. Caso o dado tenha alguma inconsistência é enviado um sinal de erro através de error\_out solicitando o reenvio.

Figura 11 – Interface entre uma porta de saída e uma porta de entrada dos roteadores, com adição dos sinais de crc\_in, crc\_out, erro\_in e erro\_out [SIL10].

A Figura 11 ilustra a técnica de CRC roteador a roteador com reenvio em nível de flit. As vantagens da técnica são que a detecção do erro ocorre antes da decisão de roteamento. Desta maneira protegendo a rede contra pacotes com erro. O método mais rápido, e requer menos área, se comparado com a retransmissão de pacotes? completos, pois o mesmo deveria ser completamente armazenado no buffer para que o cálculo de CRC fosse executado.

A segunda técnica proposta, CRC na origem, tem por objetivo economizar a área

da rede. A técnica consiste em colocar o codificador/decodificador CRC na interface de rede (NI) do módulo conectado à porta local do roteador que origina os dados. Desta maneira não é necessário que cada porta de saída do roteador tenha um codificador CRC. Contudo, os bits de CRC têm que ser incluídos no *flit*, sendo necessário assim um aumento da largura de todos os buffers da rede, o que ocasiona ao final do processo um aumento de área. A verificação do CRC é executada em cada porta de entrada da interface de rede, com isso quatro módulos de CRC são economizados na área do roteador.

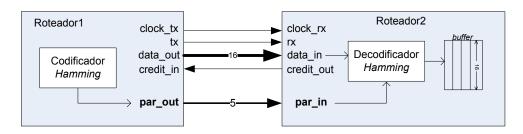

A terceira técnica proposta, *utilização de códigos de Hamming nos enlaces*, buscando corrigir 1 erro de bit em caso de *crosstalk*. Códigos de *Hamming* são códigos lineares desenvolvidos para a correção de erros, frequentemente utilizados para o controle de erros em aplicações de comunicação digital e em sistemas de armazenamento de dados. Eles têm a capacidade de corrigir apenas um erro por bloco e tem por vantagem serem simples de decodificar. No caso da utilização de códigos de *Hamming* não foi utilizado nenhum mecanismo de reenvio, pois o código de *Hamming* não provê nenhuma forma de sinalizar se houve erro em mais de um bit. A Figura 12 ilustra a arquitetura interna dos roteadores com a utilização do codificador/decodificador com códigos de *Hamming*.

Figura 12 – Interface entre dois roteadores de uma rede com Hamming nos enlaces [SIL10].

O processo de decodificação adotado na arquitetura é transparente para o roteador, pois não consome nenhum ciclo adicional de relógio. Quando o dado chega à porta de entrada ele é repassado ao decodificador *Hamming*. O dado é verificado e o corrige caso um bit tenha sido alterado. O buffer recebe o dado já decodificado fazendo com que a latência da rede não se altere. A cobertura de falhas do código de *Hamming* é muito menor do que a cobertura do CRC, pois se houver mais de um bit com erro ele não consegue detectar, e por consequência o reenvio do pacote não é possível de ser solicitado e o dado é repassado com erro.

A quarta e última técnica desenvolvida foi a de *Hamming na origem*, tendo por objetivo a tolerância de falhas interna ao roteador e a correção de erros simples nos enlaces. Conforme ilustrado na Figura 13, é utilizado código *Hamming* na interface de rede que origina os flits. Na interface de entrada e saída de cada roteador também é utilizado *Hamming*, possibilitando a correção de falhas nos enlaces e de falhas internas nos buffers.

Devido à inclusão dos Codificadores *Hamming* em cada porta de entrada e saída do roteador e na interface local, a rede tem um grande aumento em sua área. Contudo, esta rede oferece a maior cobertura de falhas nos testes relatados no trabalho utilizando

apenas códigos de *Hamming*. A única falha não detectada nesta arquitetura é caso ocorra à inversão de um bit em uma das tabelas de roteamento do *crossbar*. Caso isso ocorra o pacote pode ser encaminhado para um caminho errado, o que pode causar um *deadlock* na rede.

Figura 13 - Diagrama simplificado de uma rede com Hamming na origem [SIL10].

Os resultados encontrados foram que utilizando CRC nos enlaces o aumento de área foi de 12% contra 26% utilizando CRC na origem. A diferença de 14% deve-se ao fato que mesmo não utilizando CRC nas portas de saída o tamanho do buffer foi aumentado gerando assim uma maior área da rede. A utilização de *Hamming* nos enlaces gerou um aumento de 1% na área da rede, a técnica de *Hamming* na origem e nos enlaces gerou um aumento de 49% na rede, devido aos codificadores acrescentados na origem e em cada porta de entrada e saída, porém esta é a arquitetura que apresenta maior cobertura de falhas transientes utilizando apenas códigos de *Hamming*..

#### 1.8 Algoritmos de roteamento tolerante a falhas

O objetivo de técnicas de tolerância a falhas em nível de algoritmo de roteamento é prover, tanto em nível de hardware quanto de software, mecanismos que permitam a NoC encontrar um caminho alternativo na ocorrência de falhas.

#### 1.8.1 Topology-Agnostic Fault-Tolerant NoC Routing Method

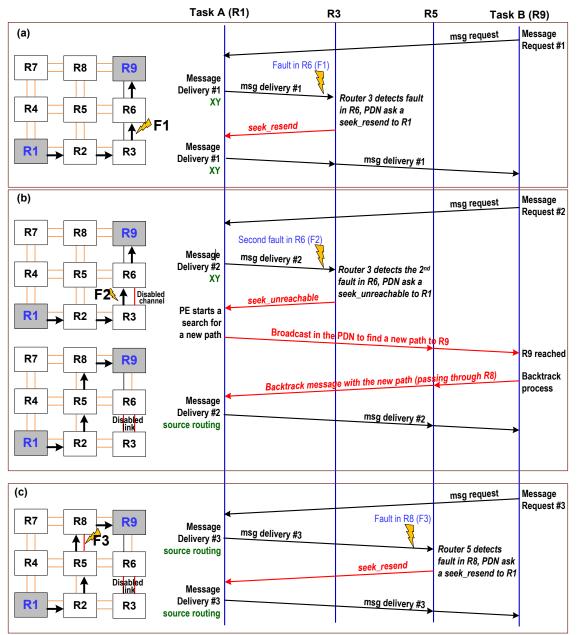

Wachter et al. [WAC13] propõem uma técnica de roteamento com foco em falhas permanentes, detectadas durante a execução do sistema. A técnica engloba topologias de rede regulares e irregulares e é independente em relação ao tamanho da NoC. A falha é detectada em tempo de execução utilizando algoritmos de teste, como BIST (fora do escopo deste trabalho).

O algoritmo de roteamento proposto inicia considerando que a NoC está sem falhas, sendo os pacotes enviados utilizando o algoritmo XY de roteamento. Uma vez que o pacote alcança o destino, é enviada uma confirmação para a origem avisando que o pacote foi recebido sem erros. Caso a confirmação não seja recebida, a origem considera que o destino é inalcançável. O algoritmo de roteamento é responsável pela procura de um novo caminho válido, explicado a seguir. Uma vez encontrado o novo caminho ele é registrado na memória do PE. O método é executado apenas uma vez a cada mensagem de confirmação perdida, evitando assim que a cada pacote o método seja reexecutado.

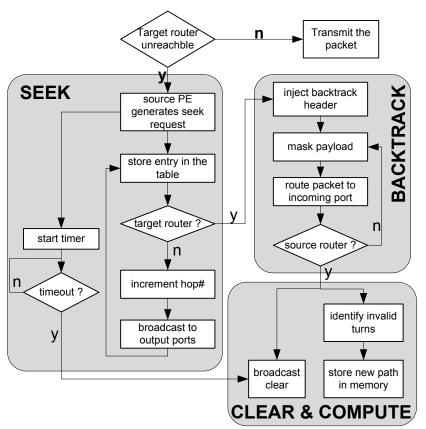

O método proposto inicia ao detectar um destino inalcançável. O método possui um

módulo responsável pela transmissão da requisição, este módulo será melhor explicado nos parágrafos seguintes. O primeiro passo do processo é denominado de seek step. Uma requisição é enviada a todos os roteadores vizinhos à origem, buscando alcançar o destino. Em cada passo da busca os seguintes dados são armazenados nos roteadores: S/T/P/# (origem, destino, porta de entrada no roteador e número de saltos). Cada roteador ao receber a requisição verifica na sua tabela de roteamento se é o destino solicitado. Caso não seja, é incrementado o número de saltos e repassada à requisição para todos com exceção porta roteadores vizinhos, da de origem O processo é repetido roteador a roteador, independentemente de se encontrar o destino. O processo é semelhante a uma onda que parte da origem da requisição, visitando todos os roteadores da rede.

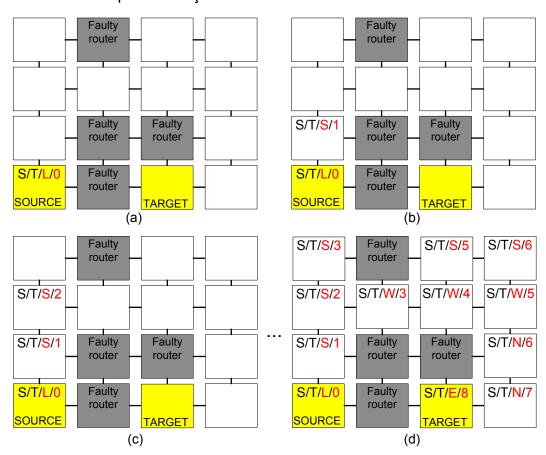

A Figura 14, ilustra um cenário com quatro roteadores falhos, um roteador origem e um roteador destino. Inicialmente o roteador origem envia uma requisição para encontrar um caminho válido até o destino (Figura 14(b)) para o único roteador vizinho não falho. O processo é repetido (Figura 14(c)), até se alcançar o roteador alvo (Figura 14(d)). Notar que o processo de propagação da "onda" visita todos os roteadores da rede, independentemente se o destino foi ou não alcançado. Este processo é realizado desta forma para se reduzir o controle do processo de propagação.

O segundo passo do método é o processo de regresso. Este processo consiste em retornar do destino à origem, utilizando o caminho livre de falhas encontrado durante o primeiro passo. O pacote de regresso ao alcançar o roteador origem terá a informação das voltas necessárias para alcançar o destino.

Figura 14 – Demonstração do método proposto por [WAC13] em uma NoC 4x4.

O terceiro passo do método é determinar um caminho livre de *deadlocks*. O PE ao receber a informação do caminho, armazena este na tabela de roteamento do PE para futuras transmissões, utilizando roteamento na origem. *Deadlocks* são evitados utilizando dois algoritmos de roteamento, *west-first* e *east-first*, cada um em um canal físico distinto. Em paralelo ao cálculo do caminho livre de *deadlocks*, o PE origem solicita que as tabelas utilizadas na etapa um (*seek*) sejam limpas, para permitir futuras buscas de caminhos.

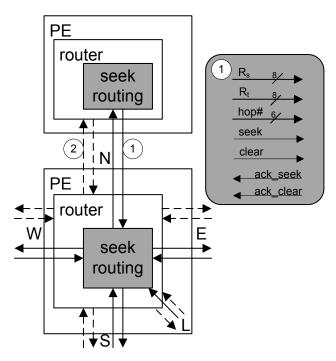

Ao realizar o broadcast na rede para enviar as requisições (*seeks*) pode-se gerar um congestionamento na rede, causando uma queda de desempenho nas aplicações. Por essa razão, o Autor sugere a criação de um módulo de roteamento específico para quando houver requisições, conforme ilustrado na Figura 15.

Figura 15 – Conexões entre os roteadores e o modulo de roteamento [WAC13].

A Figura 15 ilustra como o módulo adicional é conectado entre os roteadores vizinhos, criando-se duas redes disjuntas. A rede convencional é representada através das linhas tracejadas, e a rede específica para o módulo de requisição através das linhas contínuas. Os enlaces do módulo de requisição são utilizados apenas quando uma requisição é solicitada ou para fazer a limpeza das tabelas de roteamento. Desta maneira, o congestionamento da NoC é evitado, mantendo o desempenho da rede durante os processos de requisição.

Os resultados encontrados foram que uma área adicional de 10% do PE foi gerada, porém com um grande ganho de confiabilidade em diversos cenários, topologias de rede e diferentes dimensões de NoC. A prioridade do método consiste na busca por um caminho livre de falhas utilizando um módulo ligado a uma rede dedicada para a busca de um caminho livre de falhas. Em termos de desempenho de comunicação a latência teve um acréscimo não significativo, menor que 1%, devido ao uso do módulo de roteamento adicional. A área adicional no roteador para a inclusão do modulo de roteamento foi de aproximadamente 50%.

#### 1.8.2 A Fault-Tolerant and Hierarchical Routing Algorithm for NoC Architectures

Valinataj et al. [VAL11] sugerem um algoritmo hierárquico de roteamento tolerante a falhas. O algoritmo utiliza reconfiguração dinâmica para lidar com falhas permanentes. A cada reconfiguração o algoritmo cria uma nova rota de roteamento para cada pacote sem utilizar canais virtuais. O método seleciona o caminho de cada pacote a cada roteador com base nas informações locais dos enlaces adjacentes que são armazenadas em um registrador local.

O método pressupõe que a NoC passe por um teste *off-line* para detectar e identificar os enlaces falhos. O método possui três níveis de tolerância a falhas: no primeiro, FT\_XY, o algoritmo pode lidar com falhas que ocorrem em um enlace; no segundo nível, RDR1, o algoritmo consegue lidar com múltiplos enlaces falhos; no terceiro nível, RDR2, o algoritmo considera falhas nos roteadores.

Os Autores utilizaram como base o algoritmo de roteamento XY para desenvolver o novo método. Quando um enlace falho é detectado, um novo caminho é definido usando a menor distância possível entre os roteadores se nenhuma volta proibida for violada. Caso contrário, o novo caminho poderá ser mais longo, evitando as voltas proibidas. O registrador interno utilizado para armazenar o estado dos enlaces falhos utiliza quatro bits para armazenar esta informação. O algoritmo de roteamento FT\_XY é livre de *deadlock*, pois utiliza os mesmos princípios de proibição de voltas utilizados no XY. A diferença entre o XY e o FT\_XY é que o FT\_XY após os testes realizados para detecção de falhas é feito o cálculo do caminho dos pacotes para os roteadores vizinhos utilizando a política de voltas do algoritmo XY. O Autor utiliza tabelas de caminhos alternativos para contornar um enlace falho.

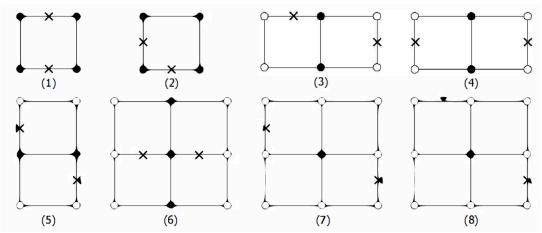

O método RDR1 estende as características utilizadas no algoritmo FT\_XY para tolerar falhas em múltiplos enlaces. Quando dois enlaces falham, coincidindo com o novo caminho do pacote, o algoritmo FT\_XY não é capaz de corrigir a falha e o pacote pode ir para um caminho errado. Existem trinta situações diferentes onde duas falhas podem ocorrer em uma NoC de topologia malha. As situações foram agrupadas em oito grupos conforme ilustrado na Figura 16.

Figura 16 – Oito diferentes grupos de situações onde ocorre duas falhas simultâneas em uma NoC [VAL11].

As falhas em dois enlaces podem ser toleradas sem a utilização de canais virtuais se forem apropriadamente consideradas. Os Autores modificaram o algoritmo FT\_XY para que ele conseguisse lidar com um número maior de falhas criando assim o algoritmo RDR1. O método RDR1 pode tolerar quinze situações de falhas e dez situações parcialmente sem o uso de canais virtuais. A diferença entre os dois níveis de tolerância é o tamanho de configuração dos registradores. O registrador que armazena as informações de falha passa a ter oito bits.

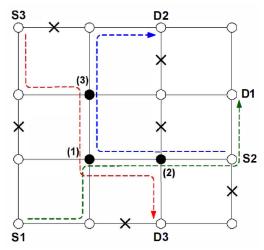

A Figura 17 ilustra três caminhos obtidos utilizando o algoritmo em uma rede com muitos enlaces em falha. A origem S1 com destino D1, origem S2 e destino D2 e origem S3 e destino D3. Os roteadores destacados em preto são comuns aos três caminhos, pois são usados para contornar os enlaces em falha.

Figura 17 – Caminho obtido através do algoritmo RDR1 em uma rede com 25% de enlaces com falha [VAL11].

O terceiro algoritmo de roteamento RDR2 é similar ao RDR1, com a diferença que pode tolerar roteadores com falhas. Caso ocorra alguma falha permanente no roteador e ele não consiga encaminhar os pacotes corretamente, o algoritmo assume que os quatro enlaces do roteador estão falhos. Os registradores dos roteadores vizinhos têm seus dados atualizados para que esses enlaces não sejam utilizados.

Os resultados reportam um aumento na área do roteador de 16,2% para o algoritmo FT\_XY, 31,8% para o RDR1 e de 40% para o RDR2. O método apresentado é adequado para NoCs que necessitam de tolerância a falhas e não podem ter um aumento muito significativo de área.

#### 1.9 Considerações finais

Foram apresentados trabalhos com objetivos distintos, técnicas de tolerância a falhas em diferentes níveis: sistêmico [MEL12], roteador [FIC09], enlace [SIL10] e algoritmos de roteamento [VAL11]. Em [FIC09] ilustra uma modificação no roteador para que a rede continue operando mesmo na presença de muitas falhas. [SIL10] módulos de CRC são uma boa alternativa para detecção de falhas. Cada uma das técnicas busca tratar uma falha específica ou seja tratando apenas uma dimensão do problema. O trabalho de [WAC13] aborda tanto o roteamento de pacotes como o nível sistêmico

(comunicação entre PEs). Os trabalhos [FIC09], [SIL10] e [WAC13] serviram de base para o desenvolvimento das técnicas que serão explicadas nos capítulos seguintes.

Buscando criar uma abordagem completa para técnicas de tolerância a falhas, é proposta neste trabalho uma solução para tolerância a falhas em nível de roteador e enlace. Estas técnicas integram-se com o trabalho proposto por [WAC13] visto que o trabalho de [WAC13] é focado nas camadas de comunicação de enlace e rede e futuramente na camada de aplicação. A presente Dissertação é voltada para a camada física e de enlace, proporcionando assim tolerância a falhas em diversos níveis de comunicação.

A Tabela 2 apresenta os níveis OSI (sem os níveis de apresentação e de sessão), e para cada nível citam-se características importantes da arquitetura adotada no presente trabalho (segunda coluna). A terceira coluna apresenta os recursos adicionados em cada nível para se prover tolerância a falhas. Notar que o nível superior, o nível de aplicação, não requer modificações no código do usuário. O mesmo código projetado para a plataforma original pode ser utilizado na plataforma tolerante a falhas.

Recursos adicionados de tolerância a Nível Arquitetura falhas CRC adicionado nas portas de entrada do Física Canais físicos duplicador por enlace (16- bit flit) roteador Test wrappers; Enlace Controle de fluxo baseado em créditos Descarte de pacotes NoC auxiliar; controle para operar em Rede Roteamento adaptativo modo degradado; busca por um caminho livre de falhas protocolo de comunicação tolerante falhas; Transporte Troca de mensagens tetransmissão de pacotes Aplicação API de comunicação Não alterada

Tabela 2 - Vista simplificada do modelo OSI e recursos de tolerância a falhas.

#### Cada nível tem as seguintes características:

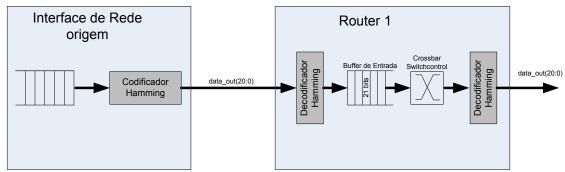

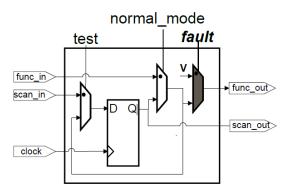

- Nível Físico: Consiste em dois canais físicos com o objetivo de manter a comunicação em caso de falha em um dos canais. Foram adicionados módulos de CRC para detectar falhas nos canais e no buffer de entrada.