# Analysis of FPGA SEU Sensitivity to Combined Effects of Conducted EMI and TID

Juliano Benfica<sup>1</sup>, Bruno Green<sup>1</sup>, Bruno C. Porcher<sup>1</sup>, Letícia Bolzani Poehls<sup>1</sup>, Fabian Vargas<sup>1</sup>, Nilberto H. Medina<sup>2</sup>, Nemitala Added<sup>2</sup>, Vitor A. P. de Aguiar<sup>2</sup>, Eduardo L. A. Macchione<sup>2</sup>, Fernando Aguirre<sup>2</sup>, Marcilei A. G. da Silveira<sup>3</sup>

<sup>1</sup>Electrical Engineering Department, Catholic University – PUCRS, Brazil. vargas@computer.org <sup>2</sup>Instituto de Física, Sao Paulo University – USP, Brazil. medina@if.usp.br <sup>3</sup>Depto. de Física, Centro Universitário – FEI, Brazil. marcilei@fei.edu.br

Abstract— This work proposes a novel methodology to evaluate SRAM-Based FPGA SEU susceptibility to noise on VDD power pins and total-ionizing dose (TID). The procedure was demonstrated for SEU measurements on a Xilinx Spartan 3E FPGA operating in an 8MV Pelletron accelerator, whereas TID was deposited by means of a Shimadzu XRD-7000 X-ray diffractometer. The injected noise on power supply bus comprised of voltage dips of 16.67% and 25% of VDD at two different frequencies 10Hz and 5kHz, and was performed according to the IEC 61.000-4-29 international standard.

*Index Terms*—SEU Sensitivity, SRAM-Based FPGA, Power-Supply Noise, EMI, TID, Combined Test, Spartan 3E.

### I. INTRODUCTION

The widespread use of Field-Programmable Gate Arrays (FPGAs) in our daily lives has become a general consensus among IC and embedded system designers, with numerous applications in the fields such as telecommunication, automotive [1], medical and aerospace & defense [2]. However, the latter application field requires not necessarily competitive costs but instead, highly reliable devices by default. In this sense, SRAM-based FPGAs are pretermitted with respect to flash or anti-fuse devices [3]. This is the case of FPGAs used in the design of embedded systems for satellite applications due to the continuous sensitivity increase to single-event upset (SEU), electromagnetic interference (EMI) and total-ionizing radiation (TID) [4,5]. This is particularly true for SEU and EMI because IC sensitivity deteriorates as technology scales down. Note that for smaller geometry technologies, information is stored in smaller capacitors, clock frequency tends to increase and power supply is driven to values much lower than 1 volt, which renders ICs more sensitive to noise and external perturbations such as SEU and EMI.

Furthermore, the process of qualifying ICs to critical applications is usually treated as an independent, fragmented event, i.e., engineers certify devices to EMI, TID or SEU or eventually to all of them, but often not taking into account the combined effects one phenomenon may take over the other. In this scenario, this paper proposes a novel methodology to analyze the SEU sensitivity of FPGA devices to combined effects of conducted EMI and TID. The procedure was

demonstrated for SEU measurements on a Xilinx Spartan 3E FPGA exposed to combined noise on power supply bus comprised of voltage dips of 16.67% and 25% of  $V_{DD}$  at frequencies of 10Hz and 5kHz respectively, and total-ionizing dose (TID). Noise was injected according to the IEC 61.000-4-29 standard [6].

## II. METHODOLOGY DESCRIPTION

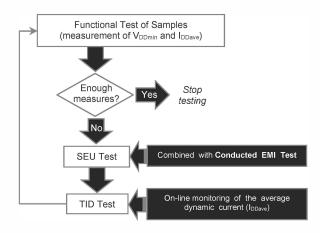

Hereafter, the methodology is introduced by describing an experiment performed on two Xilinx/Spartan 3E FPGAs (part number XC3S500E-4PQ208), from different fabrication lots. In the remaining of the paper, these devices under test (DUTs) are identified as FPGA1 and FPGA2. The test flow applied to these components is depicted in Fig. 1. Both FPGAs were sitting on a new version of a dedicated, configurable platform for IC combined tests of total-ionizing dose radiation and electromagnetic interference, whose first version was introduced in [7]. Initially, a functional test was performed to check the fresh component nominal operating conditions: minimum operating voltage ( $V_{DDmin}$ ) and average dynamic current ( $I_{DDave}$ ).

Fig. 1. Test flow applied to the two Xilinx Spartan 3E FPGAs.

For the functional test and the TID test, the DUTs were configured with the LEON3 softcore processor [8] running a bubble sort program. LEON3 is a synthesizable VHDL model of a 32-bit 7-stage pipeline processor compliant with the SPARC V8 architecture. The model is highly configurable, and particularly suitable for system-on-a-chip (SoC) designs.

The full source code is available under the GNU GPL license, allowing free and unlimited use for research and education. LEON3 is also available under a low-cost commercial license, allowing it to be used in any commercial application to a fraction of the cost of comparable IP cores. The ISE-Xilinx design framework was used to configure and validate the embedded system (i.e., the processor and the bubble sort program) on the fresh Spartan 3E FPGAs.

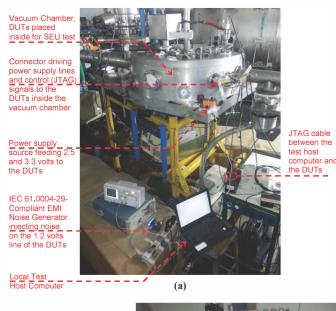

Then, the SEU test was initiated in order to measure the SEU susceptibility of the two DUTs by exposing them to heavy ions inside an 8MV Pelletron accelerator (see Fig. 2a). The devices were irradiated with the following ions: <sup>12</sup>C, <sup>16</sup>O, <sup>28</sup>Si and <sup>35</sup>Cl.

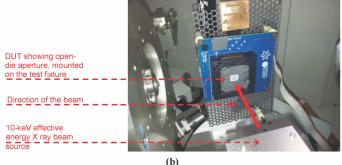

Fig. 2. Test environment: (a) 8MV Pelletron accelerator, (b) 10-keV Shimadzu XRD-7000 X-ray diffractometer.

In the sequence, the TID test was initiated by exposing the DUTs to a 10-keV effective energy X ray beam in a Shimadzu XRD-7000 X-ray diffractometer (see Fig. 2b). It was used 100 rad/s dose rate during this process. The irradiation period was controlled in order that the total doses absorbed by the devices were 750 krad and 950 krad. The samples were held 10 cm away from the beam source to ensure homogeneity in the area to be irradiated. The dose rate was estimated by measuring exposure in an ionization chamber and the X-ray dose rate in silicon was calibrated using air and silicon mass attenuation coefficients. The effective energy was measured using aluminum foils of different thickness and calculating the half–attenuation Al layer. In fact, for TID effects, 10 keV X-ray

radiation is a very convenient source of radiation owing to its higher charge yield compared to protons, alpha particle and heavy ions. The above test flow was repeated twice for each of the FPGAs: in the first run, it was deposited 150 krad on FPGA1 and 400 krad on FPGA2, whereas in the second run it was deposited additional 600 krad on FPGA1 and 550 krad on FPGA2. At the end of the experiment, these devices received a total ionizing dose of 750 krad (FPGA1) and 950 krad (FPGA2).

### III. OBTAINED RESULTS AND DISCUSSIONS

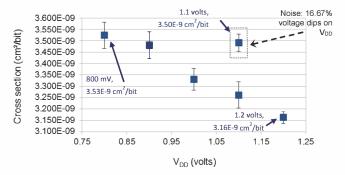

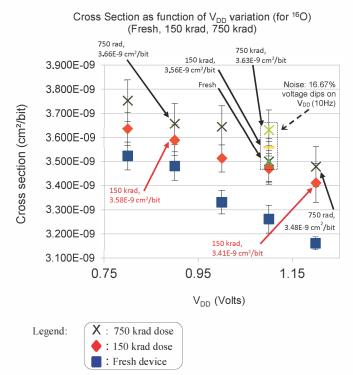

Fig. 3 presents the FPGA1 SEU cross section as a function of (a) voltage reduction: from the nominal value (1.2 volts) down to 800 mV; and (b) noise on power supply lines (16.67% voltage dips on V<sub>DD</sub>, at a frequency of 10 Hz). The bit-flip counting procedure was conducted by performing continuous readback of the configuration bitstream of the FPGA. It is worth mentioning that in this case, the configuration bitstream was composed of the configuration bits plus the BlockRAM bits used to store user information. As observed, when  $V_{DD}$  is reduced from 1.2 to 0.8 volts (33.33%), the average FPGA1 SEU sensitivity (configuration bits + BlockRAM bits) increases from  $3.16 \times 10^{-9} \text{ cm}^2/\text{bit}$  to  $3.53 \times 10^{-9}$  cm<sup>2</sup>/bit (i.e., 11.70%). For those readers not familiar with SEU practical experiments, it is worth noting the definition of SEU cross section as being the total area of the circuit such that, if exposed to radiation, there will be SEUs. So, as larger is the SEU cross section, more sensitive is the circuit to single-event upsets.

Cross Section as function of V<sub>DD</sub> variation (for <sup>16</sup>O)

Fig. 3. FPGA1 SEU cross section as a function of: (a) voltage reduction from the nominal value (1.2 volts) down to 800 mV; and (b) noise on power supply lines (16.67% voltage dips on  $V_{DD}$ , at a frequency of 10 Hz). Results for fresh component.

It is important to note that noise on power supply lines seems to be more harmful to the FPGA SEU sensitivity than  $V_{DD}$  reduction: SEU cross section increases from 3.16 x 10<sup>-9</sup> cm<sup>2</sup>/bit to 3.50x10<sup>-9</sup> cm<sup>2</sup>/bit (i.e., by 10.76%) when 16.67% voltage dips are applied on  $V_{DD}$ , which is quite close to the 11.70% SEU cross section degradation (3.53x10<sup>-9</sup> cm<sup>2</sup>/bit) for a  $V_{DD}$  = 800 mV (33.33% voltage reduction on  $V_{DD}$  bus). In other words, **16.67% voltage dips on V\_{DD}** induces the same SEU cross section as the one yielded by **reducing V<sub>DD</sub> by 33.33%**. From this scenario and aiming to guarantee a given SEU cross section, one could suggest design engineers to take more care to prevent noise than small power supply reductions from appearing on the FPGA bus during system lifetime. This goal can be reached, for instance, by implementing specific RC filters at the FPGA input power pins so that to prevent external noise from entering the chip [9]. The same experiment was also carried out with FPGA2, which yielded similar results. In this case, it was applied 5 kHz, 25% voltage dips on the V<sub>DD</sub> bus.

Fig. 4 provides results for FPGA1 at three different instants: fresh, after deposition of 150 and 750 krad. As observed, as long as radiation is being deposited, SEU cross section is being increased by a factor of 5.16% with respect to the fresh condition (averaged 5 measurement points for 150 krad curve divided by the averaged 5 measurement points of the fresh curve) and 7.55% (resp. 750 krad curve). At the same time, one can also conclude that no matter the component is fresh or irradiated, SEU cross section increases dramatically as response to  $V_{DD}$  reduction from 1.2 to 0.8 volts: SEU cross section degrades in average 11.40% for fresh device, 6.57% for the 150 krad irradiated device and 7.85% for the device with 750 krad.

Fig. 4. FPGA1 SEU cross section as a function of: (a) voltage reduction from the nominal value (1.2 volts) down to 800 mV; and (b) noise on power supply lines (16.67% voltage dips on  $V_{DD}$ , at a frequency of 10 Hz). Results for fresh, 150 and 750 krad component.

Finally, the combination of "noise on power pins plus TID" is more harmful to the chip than the combination of " $V_{DD}$  reduction + TID", as can be observed: for the fresh component, 16.67% voltage dips on  $V_{DD}$  induces similar SEU cross section as the one yielded by reducing  $V_{DD}$  by 33.33%. This behavior can also be observed for the irradiated component:

A) 16.67% voltage dips on  $V_{DD}$  induces a SEU cross section increase (at  $3.56 \times 10^{-9} \text{ cm}^2/\text{bit}$ , 150 krad curve, with respect to  $3.41 \times 10^{-9} \text{ cm}^2/\text{bit}$ ,  $V_{DD} = 1.2$  volts), quite similar to the SEU cross section ( $3.58 \times 10^{-9} \text{ cm}^2/\text{bit}$ ,  $V_{DD} = 0.9$  volts) induced by 25% VDD

#### reduction.

B) 16.67% voltage dips on  $V_{DD}$  induces a SEU cross section increase (at  $3.63 \times 10^{-9}$  cm<sup>2</sup>/bit, **750 krad curve**, with respect to  $3.48 \times 10^{-9}$  cm<sup>2</sup>/bit,  $V_{DD} = 1.2$  volts), quite similar to the SEU cross section ( $3.66 \times 10^{-9}$  cm<sup>2</sup>/bit,  $V_{DD} = 0.9$  volts) induced by **25% VDD reduction**.

## IV. CONCLUSIONS

This paper briefly described a dedicated methodology to analyze the SEU sensitivity of FPGA devices to combined effects of conducted EMI and TID. The procedure was demonstrated for SEU measurements on a Xilinx Spartan 3E FPGA device (part number XC3S500E-4PQ208). The injected noise on power supply bus comprised of voltage dips of 16.67% and 25% of V<sub>DD</sub> at frequencies of 10Hz and 5kHz respectively, and it was performed according to the IEC 61.000-4-29 international standard.

Analyzing Fig. 4, one can conclude that noise (16.67% voltage dips on  $V_{DD}$ , 10Hz) induces similar SEU cross section as the one yielded by reducing  $V_{DD}$  (33.33%). So, at least for this frequency and for this component, noise on power bus pins seems to be more harmful to SEU cross section than  $V_{DD}$  reductions.

At present, we are analyzing and comparing the impact of low-frequency and high-frequency noises on the SEU cross section degradation of FPGA2 (which received a total ionizing radiation of 950 krad and operated under exposition of 25% voltage dips at frequency of 5 kHz. Preliminary experiments indicate that low-frequency noise induces more SEU cross section degradation than the high-frequency one. This conclusion will be confirmed by means of future experiments to be conducted with the same components, for similar voltage dips and frequencies in the range of [10 - 5kHz] and above. Currently, we are also repeating similar experiments with the flash-based ProASIC3 A3PE1500 FPGA from Microsemi.

#### ACKNOWLEDGEMENTS

This work has been supported in part by **CNPq** (National Science Foundation, Brazil) under contract n. 303701/2011-0 (PQ), Project **CITAR-FINEP**, **FAPESP** (contract n. 2012/03383-5) and **Hewlett-Packard Brazil** Ltd. using incentives of Brazilian Informatics Law (8.2.48 from 1991).

#### REFERENCES

- [1] www.microsemi.com/document-portal/doc\_view/131297-automotive-top-tenproduct-information-brochure. Last access: Jan 2016.

- [2] www.xilinx.com/applications/aerospace-and-defense/avionics.html. Last access: Jan 2016.

- [3] C. Bernardeschi, L. Cassano, A. Domenici, "SRAM-Based FPGA Systems for Safety-Critical Applications: A Survey on Design Standards and Proposed Methodologies", Journal of Computer Science and Technology, 30(2): 373–390, Mar. 2015.

- [4] J. Freijedo, L. Costas, J. Semião, J. J. Rodríguez-Andina, M. J. Moure, F. Vargas, I. C. Teixeira, J. P. Teixeira, "Impact of power supply voltage variations on FPGAbased digital systems performance", Journal of Low Power Electronics, vol. 6, August 2010, pp. 339-349.

- [5] H. Quinn, P. Graham, J. Krone, M. Caffrey, S. Rezgui, "Radiation-induced multibit upsets in SRAM-based FPGAs", IEEE Trans. on Nuclear Science, vol.52, no.6, pp. 2455- 2461, Dec. 2005.

- [6] "IEC 61.000-4-29: Electromagnetic compatibility (EMC) Part 4-29: Testing and measurement techniques – Voltage dips, short interruptions and voltage variations on d.c. input power port immunity tests", First Edition, 2000-01. (http://www.iec.ch)

- [7] J. Benfica, L. B. Poehls, F. Vargas, J. Lipovetzky, A. Lutenberg, E. Gatti, F. Hernandez, "Customized Platform for TID and EMI IC Combined Measurements: Case-Study and Experimental Results", Journal of Electronic Testing, v. 28, Springer, p. 803-816, 2012.

- [8] S. B. Dhia, M. Ramdani, E. Sicard, "Electromagnetic Compatibility of Integrated Circuits – Techniques for Low Emission and Susceptibility", ISBN: 978-0-387-26600-8, Springer, 2006.