### PONTIFICAL CATHOLIC UNIVERSITY OF RIO GRANDE DO SUL FACULTY OF INFORMATICS GRADUATE PROGRAM IN COMPUTER SCIENCE

# ON THE VIRTUALIZATION OF MULTIPROCESSED EMBEDDED SYSTEMS

## ALEXANDRA DA COSTA PINTO DE AGUIAR

Dissertation presented as partial requirement for obtaining the degree of Ph. D. in Computer Science at Pontifical Catholic University of Rio Grande do Sul.

Advisor: Prof. PhD. Fabiano Passuelo Hessel

## Dados Internacionais de Catalogação na Publicação (CIP)

| A282o                                                                                        | Aguiar, Alexandra da Costa Pinto de<br>On the virtualization of multiprocessed embedded systems /<br>Alexandra da Costa Pinto de Aguiar. – Porto Alegre, 2014.<br>109 p. |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tese (Doutorado) – Fac. de Informática, PUCRS.<br>Orientador: Prof. Fabiano Passuelo Hessel. |                                                                                                                                                                          |

|                                                                                              | <ol> <li>Informática. 2. Máquinas Virtuais. 3. Microprocessadores.</li> <li>I. Hessel, Fabiano Passuelo. II. Título.</li> </ol>                                          |

| CDD 004.36                                                                                   | CDD 004.36                                                                                                                                                               |

|                                                                                              |                                                                                                                                                                          |

## Ficha Catalográfica elaborada pelo Setor de Tratamento da Informação da BC-PUCRS

Pontifícia Universidade Católica do Rio Grande do Sul FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

### TERMO DE APRESENTAÇÃO DE TESE DE DOUTORADO

Tese intitulada "On the virtualization of multiprocessed embedded systems", apresentada por Alexandra da Costa Pinto de Aguiar, como parte dos requisitos para obtenção do grau de Doutor em Ciência da Computação, aprovada em 30/08/2013 pela Comissão Examinadora:

Prof. Dr. Fabiano Passuelo Hessel Orientador

Prof. Dr. Tiago Coelho Ferreto

Prof. Dr. Rodolfo Jardim de Azevedo

Kekolto Azer into

Prof. Dr. Rômulo Silva de Oliveira

UFSC

UNICAMP

PPGCC/PUCRS

PPGCC/PUCRS

Homologada em24/04/2014 conforme Ata No. 006 pela Comissão Coordenadora.

Prof. Dr. Luiz Gustavo Leão Fernandes Coordenador.

PUCR

**Campus Central** Av. Ipiranga, 6681 - P. 32 - sala 507 - CEP: 90619-900 Fone: (51) 3320-3611 - Fax (51) 3320-3621 E-mail: ppgcc@pucrs.br www.pucrs.br/facin/pos

I dedicate this work and everything it represents to my parents. (Dedico este trabalho e tudo que ele representa a meus pais.)

"Stay hungry, stay foolish." (Steve Jobs)

#### ACKNOWLEDGMENTS

This text is written in Brazilian Portuguese, so my beloved ones can read it eventually.

Este momento é sempre bastante esperado. Quando se chega no ponto de agradecer alguém é porque todo (ou uma parte significativa) o caminho foi percorrido. É claro que a vontade intrínseca de cada ser o ajuda a conquistar seus objetivos... mas não há quem alcance qualquer nível de sucesso sem ajuda do outro. E agora, é chegado o momento de agradecer.

À Deus, ao Universo, a esta força misteriosa e superior que me abençoa constantemente em tantos aspectos da minha vida. A começar pela maior dádiva que se pode ter: uma família. Meus pais, incansáveis. Ajudando em absolutamente tudo o que podiam e, por vezes, até exagerando e se doando mais do que deviam. Bárbara Maix disse: "Mostremos com exemplos aquilo que com palavras ensinamos". E posso com 100% de certeza afirmar: não há no mundo melhores exemplos de pais do que vocês. Amo muito e o agradecimento por tudo será sempre eterno.

À meu maninho querido, Muca, que me surpreende constantemente com seu desprendimento das coisas que eu não consigo me desprender. Sempre trazendo alegria, irreverência e, por que não, constrovérsia à minha vida... afinal, irmão é pra essas coisas... te amo piá.

Aos meus "meio-irmãos" que estão sempre enviando energias positivas para que tudo se encaminhe bem, ainda que a correria da vida moderna nos impeça de conversar mais e termos mais tempo em convívio.

Ao meu orientador, Fabiano, que me acolheu nesta longa jornada desde que vim "do interior" sempre com paciência, liderança e conselhos tão necessários. Definitivamente, eu tive o melhor orientador que poderia querer.

À Felipe e Sérgio por serem tão parceiros e não me jogarem do sétimo andar depois de mais um "gente, vamo fazer esse paper"... Aos colegas Marcos e Carlos que tiveram participação direta na construção deste trabalho que, definitivamente, não poderia ser feito sem a parceria e colaboração de vocês. Aos demais colegas do laboratório, que sempre ajudaram quando necessário. A diversos colegas professores que aguentaram por tanto tempo a frase "hoje não, tem a tese".

Agradeço em especial à Andriele e ao Ricardo que tantas vezes toparam tomar um café no térreo apenas para amenizar o estresse do trabalho acumulado enquanto falávamos de algum seriado, filme ou ator que eu havia me apaixonado. À Sabrina que se mostrou uma grande amiga nos últimos anos e, sim Sá, ainda vamos ter tempo para mais coisas :) Ao Rafael que está passando por tudo que eu passei com dois anos de atraso... se prepara :P Ao Marcelo por ter sido um exemplo de persistência e um grande amigo :D A muitos amigos de longa data que finalmente vão poder parar de perguntar "e a tese, como vai?!" :-) Aos meus primos, tios, tias e sobrinhas com quem não pude estar tão presente quanto gostaria em função desta imensa "empreitada".

Pode parecer ridículo aos que não entendem esta relação, mas aos meus cachorros. Primeiro pro Zé que teve que ser doado ao longo desta jornada e acabou se adaptando tanto à casa da vó que nem voltou. Aos meus bebês mais novos, Tony e Jorge, que pegaram os últimos meses loucos disso tudo.

Às minhas séries e filmes favoritos que ajudaram a relaxar quando não havia outra alternativa. À minha biblioteca imensa de músicas que faz parte da minha vida quase que na mesma proporção do oxigênio.

Infelizmente, não conseguiria expressar os nomes de todas as pessoas que deveria. Apenas que, um doutorado pode ser comparado à uma maratona. É você que treina, que sofre as contusões, que precisa persistir. Mas você não alcança à linha de chegada sem um bom técnico, sem bons tênis, sem água, sem pessoas te animando e incentivando quando cada metro parece insuperável. Talvez você nem lembre de todas essas pessoas, mas elas estiveram lá. Talvez, você não tenha como agradecer a cada um individualmente, mas todos fizeram parte do seu sucesso. Assim, eu reconheço aqui a participação de cada um que me ajudou a chegar até aqui. E, a todos que tiveram participação nisso tudo, meu mais sincero <muito obrigada>.

# VIRTUALIZAÇÃO EM SISTEMAS EMBARCADOS MULTIPROCESSADOS

### RESUMO

Virtualização surgiu como novidade em sistemas embarcados tanto no meio acadêmico quanto para o desenvolvimento na indústria. Entre suas principais vantagens, pode-se destacar aumento: (i) na qualidade de projeto de software; (ii) nos níveis de segurança do sistema; (iii) nos índices de reuso de software, e; (iv) na utilização de hardware. No entanto, ainda existem problemas que diminuíram o entusiasmo com relação ao seu uso, já que existe um overhead implícito que pode impossibilitar seu uso. Assim, este trabalho discute as questões relacionadas ao uso de virtualização em sistemas embarcados e apresenta estudos voltados para que arquiteturas MIPS multiprocessadas tenham suporte à virtualização.

Palavras-Chave: máquinas virtuais, hypervisores, virtualização, MPSoC.

# ON THE VIRTUALIZATION OF MULTIPROCESSED EMBEDDED SYSTEMS

### ABSTRACT

Virtualization has become a hot topic in embedded systems for both academia and industry development. Among its main advantages, we can highlight (i) software design quality; (ii) security levels of the system; (iii) software reuse, and; (iv) hardware utilization. However, it still presents constraints that have lessened the excitement towards itself, since the greater concerns are its implicit overhead and whether it is worthy or not. Thus, we discuss matters related to virtualization in embedded systems and study alternatives to multiprocessed MIPS architecture to support virtualization.

Keywords: Virtual machines, hypervisors, virtualization, MPSoC.

# LIST OF FIGURES

| Figure 1.1 – Consolidation of several OSs using virtualization                                  | 26 |

|-------------------------------------------------------------------------------------------------|----|

| Figure 1.2 – Legacy software coexist with newer applications                                    | 27 |

| Figure 1.3 – User attack blocked by virtualization's inherent isolation $\ldots$                | 27 |

| Figure 1.4 – Different processor configurations: a) single physical core; b) multicore $\ldots$ | 28 |

| Figure 1.5 – Improved reliability for AMP architectures                                         | 28 |

| Figure 1.6 – Migration between virtual machines using the same OS on the same ISA               | 29 |

| Figure 2.1 – Former Typical Embedded System Model                                               | 34 |

| Figure 2.2 – Generic Hypervisor Model                                                           | 36 |

| Figure 2.3 – Typical Privilege Rings of Modern CPUs                                             | 37 |

| Figure 2.4 – Ring de-privileging caused by the hypervisor                                       | 37 |

| Figure 2.5 – Hypervisor Type 1                                                                  | 38 |

| Figure 2.6 – Hypervisor Type 2                                                                  | 38 |

| Figure 2.7 – Binary Translation for OS - Direct Execution for Applications                      | 39 |

| Figure 2.8 – Guest OS Kernel Code is an input to the Binary Translator                          | 40 |

| Figure 2.9 – Xen's paravirtualization approach                                                  | 42 |

| Figure $2.10 -$ Hypervisor control of pure virtualization (part A) and paravirtualization       |    |

| (part B)                                                                                        | 43 |

| Figure 2.11 – Hardware support to virtualization                                                | 43 |

| Figure 2.12 – TLB approach with Nested/Extended Page Tables                                     | 44 |

| Figure 3.1 – ARM TrustZone                                                                      | 46 |

| Figure 3.2 – EmbeddedXen Hypervisor Approach                                                    | 48 |

| Figure 3.3 – OKL4 Hypervisor Approach                                                           | 48 |

| Figure 3.4 – Windriver Hypervisor Approach                                                      | 49 |

| Figure 3.5 – VLX Hypervisor Approach                                                            | 50 |

| Figure 3.6 – Trango Hypervisor Approach                                                         | 50 |

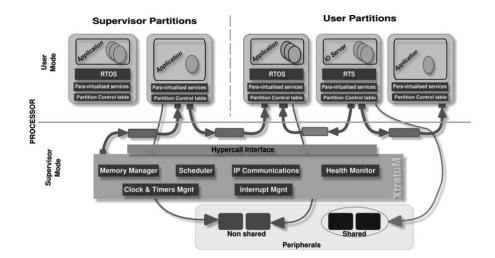

| Figure 3.7 – Xtratum Hypervisor Approach                                                        | 52 |

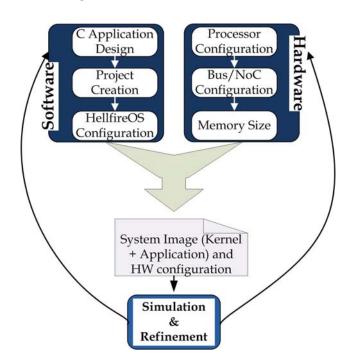

| Figure 4.1 – Hellfire Framework Design Flow                                                     | 57 |

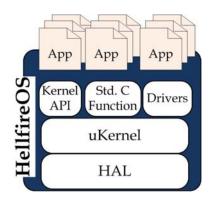

| Figure 4.2 – HellfireOS Structure Stack                                                         | 58 |

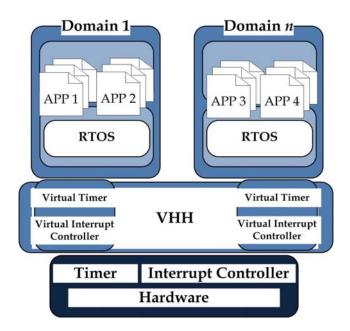

| Figure 4.3 – Virtual-Hellfire Hypervisor Domain structure                                       | 59 |

| Figure 4.4 – Virtual-Hellfire Hypervisor Memory Management                                      | 60 |

| Figure 4.5 – Virtual-Hellfire Hypervisor I/O Handling                                           | 60 |

| Figure 4.6 – VHH System Architecture                                                            | 62 |

| Figure 4.7 – VHH Integrated in the Hellfire Framework                                           | 63 |

| Figure 4.8 – Cluster-based MPSoC concept                                                     | 63 |

|----------------------------------------------------------------------------------------------|----|

| Figure 4.9 – VHH Memory for (A) Non-clustered systems (B) Clustered systems                  | 64 |

| Figure 4.10 – VHH Communication Infrastructure with NoC based Systems                        | 65 |

| Figure 4.11 – Virtual Cluster-Based MPSoC proposal                                           | 65 |

| Figure 4.12 – Virtual Cluster-Based MPSoC with Application Specialization                    | 66 |

| Figure 4.13 – Virtualization model for embedded systems                                      | 68 |

| Figure 4.14 – Flexible Mapping model for multiprocessed embedded systems                     | 69 |

| Figure 4.15 – Virtualization Hardware Platform main modules                                  | 70 |

| Figure 4.16 – MMU block diagram                                                              | 71 |

| Figure 4.17 – guest OS privileged instruction execution                                      | 72 |

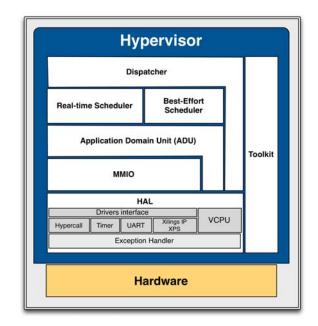

| Figure 4.18 – Hypervisor block diagram                                                       | 73 |

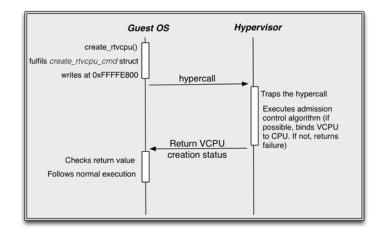

| Figure 4.19 – Sequence diagram of RT-VCPU creation                                           | 74 |

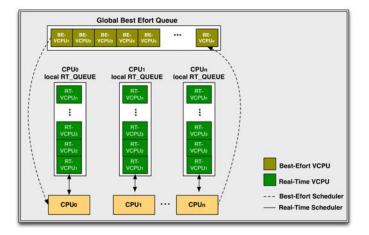

| Figure 4.20 – Real-time and best-effort multiprocessed strategy                              | 75 |

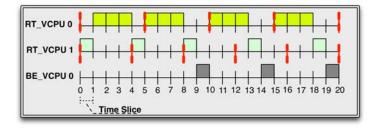

| Figure 4.21 – Real-time scheduling sample                                                    | 75 |

| Figure 4.22 – Real-time scheduling sample with voluntary preemption                          | 76 |

| Figure 4.23 – Producer-consumer virtualization scenario                                      | 78 |

| Figure 4.24 – Producer-consumer execution                                                    | 79 |

| Figure 4.25 $-$ Jitter measurement for system load of 90% in virtualized and non-virtualized |    |

| platforms                                                                                    | 80 |

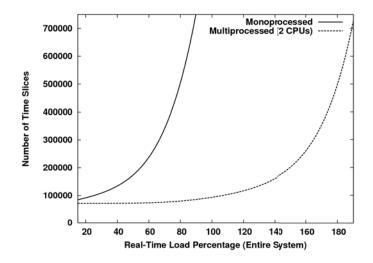

| Figure 4.26 – Real-time impact onto Best-Effort execution (mono- and multi-processed         |    |

| virtualized platforms)                                                                       | 81 |

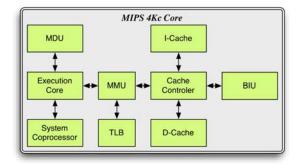

| Figure 4.27 – MIPS 4K core                                                                   | 83 |

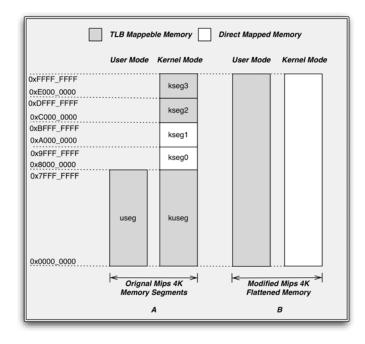

| Figure 4.28 – MIPS 4K memory management for User and Kernel modes of operation               | 84 |

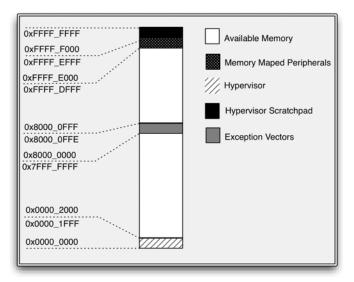

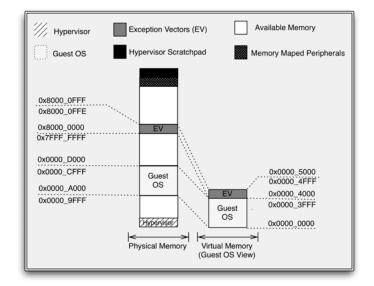

| Figure 4.29 – Hypervisor memory logical organization                                         | 86 |

| Figure 4.30 – Exception Vector modification                                                  | 87 |

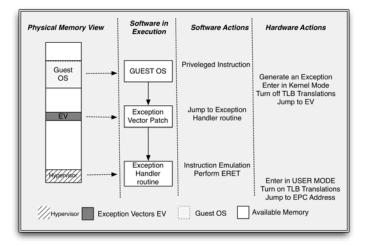

| Figure 4.31 – guest OS privileged instruction execution                                      | 88 |

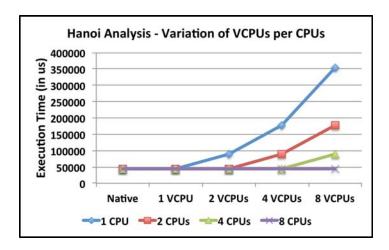

| Figure 4.32 – Virtualization execution overhead for the Hanoi algorithm                      | 91 |

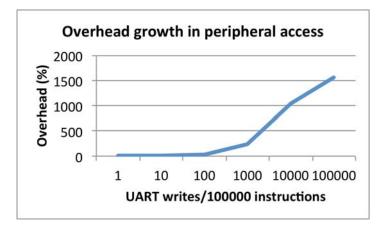

| Figure 4.33 – Virtualization overhead at UART accesses                                       | 92 |

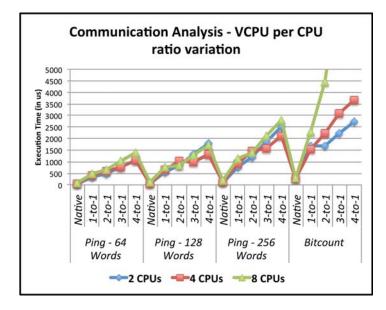

| Figure 4.34 – Communication Test with Synthetic Application (Ping Test)                      | 93 |

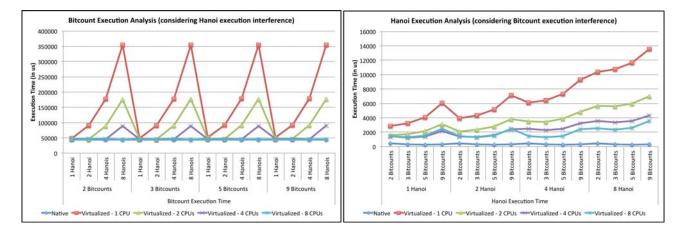

| Figure 4.35 – Mixed Scenario With Bitcount and Hanoi application's interference in each      |    |

| other's execution time                                                                       | 94 |

# LIST OF TABLES

| Table 2.1 – | Embedded applications' examples                      | 33 |

|-------------|------------------------------------------------------|----|

| Table 3.1 – | Comparison among different virtualization approaches | 56 |

| Table 4.1 – | Area results for MPSoCs configuration                | 67 |

| Table 4.2 – | Synthesis results on a Xilinx Virtex-4 FPGA          | 77 |

## LIST OF ACRONYMS

- ABI Application Binary Interface

- ADU Application Domain Unit

- AMP Asymmetric Multiprocessing

- AMT Active Management Technology

- API Application Programming Interface

- ASID Address Space IDentifier

- BE Best-effort

- DBT Dynamic Binary Translation

- DMA Direct Memory Access

- EDF Earliest Deadline First

- EPC Exception Program Counter

- EPT Extended Page Tables

- ES Embedded Systems

- FOTA Firmware Over the Air

- FPGA Field Programmable Gate Array

- GPL General-purpose License

- HAL Hardware Abstraction Layer

- HFOS HellfireOS

- HVM Hardware-assisted Virtual Machine

- IMA Integrated Modular Avionics

- IP Intellectual Property

- IPC Inter-process communication

- ISA Instruction-Set Architecture

- LL Load Linked

- LLVM Low Level Virtual Machine

- LOC Lines of Code

- MILS Multiple Independent Levels of Security

- MIPC Multicore/multi-OS Interprocess Communication

- MMU Memory Management Unit

- NI Network Interface

- NOCS Networks-on-Chip

- OS Operating System

OVP - Open Virtual Platform

RT – Real-time

RTOS – Real-time Operating System

SC – Store Conditional

SMP – Symmetric Multiprocessing

SVM – Secure Virtual Machine

TC – Translator Cache

TCO – Total Cost of Ownership

TLB – Translation Lookaside Buffer

TXT – Trusted Execution Technology

VCPU – Virtual CPU

VHH – Virtual-Hellfire Hypervisor

VT – Virtualization Technology

WCET – Worst Case Execution Time

# CONTENTS

| 1     | INTRODUCTION                                                        | 25  |

|-------|---------------------------------------------------------------------|-----|

| 1.1   | MOTIVATIONAL EXAMPLES FOR EMBEDDED VIRTUALIZATION                   | 26  |

| 1.2   | RESEARCH GOAL AND QUESTIONS                                         | 30  |

| 1.3   | CONTRIBUTIONS AND ORIGINAL ASPECTS                                  | 31  |

| 1.4   | STRUCTURE OF THIS DISSERTATION                                      | 32  |

| 2     | BACKGROUND CONCEPTS                                                 | 33  |

| 2.1   | EMBEDDED SYSTEMS                                                    | 33  |

| 2.2   | CLASSICAL VIRTUALIZATION                                            | 35  |

| 2.2.1 | VIRTUALIZATION LAYER - THE HYPERVISOR                               | 36  |

| 3     | LITERATURE REVIEW                                                   | 45  |

| 3.1   | HARDWARE SUPPORT IN EMBEDDED ARCHITECTURES                          | 45  |

| 3.2   | EXISTING HYPERVISORS                                                | 47  |

| 3.3   | ACADEMIC RESEARCH                                                   | 52  |

| 3.3.1 | SUMMARY                                                             | 55  |

| 4     | VIRTUALIZATION IN MPSOCS - PROPOSALS AND IMPLEMENTATIONS            | 57  |

| 4.1   | FIRST ATTEMPT - A HELLFIREOS IMPROVEMENT AND PARAVIRTUALIZED        | 57  |

| 4.1.1 | HELLFIRE FRAMEWORK                                                  |     |

| 4.1.2 | VIRTUAL-HELLFIRE HYPERVISOR (VHH), A HELLFIREOS-BASED HYPERVISOR    | 59  |

| 4.1.3 | CLUSTER-BASED MPSOCS                                                |     |

| 4.1.4 | SUMMARY                                                             |     |

| 4.2   | SECOND ATTEMPT - VIRTUALIZATION MODEL AND HARDWARE IMPLEMEN-        | 67  |

| 4.2.1 | VIRTUALIZATION MODEL                                                | 67  |

| 4.2.2 | HARDWARE PLATFORM                                                   | 69  |

| 4.2.3 | HARDWARE VIRTUALIZATION SUPPORT                                     | 71  |

| 4.2.4 | VIRTUALIZATION SOFTWARE AND REAL-TIME                               | 73  |

| 4.2.5 | EVALUATION AND RESULTS                                              | 76  |

| 4.2.6 | JITTER MEASUREMENT: VIRTUALIZED <i>VS.</i> NON-VIRTUALIZED PLATFORM | 79  |

| 4.2.7 | REAL-TIME INFLUENCE ON BEST-EFFORT EXECUTION: MONOPROCESSED         | . 5 |

| 1.4.1 | VS. MULTIPROCESSED                                                  | 80  |

| 4.2.8  | CASE-STUDY: PORTING HELLFIREOS TO MODIFIED MIPS     | 81  |

|--------|-----------------------------------------------------|-----|

| 4.2.9  | SUMMARY                                             | 82  |

| 4.3    | THIRD ATTEMPT - ANOTHER MIPS-PROCESSOR MODIFICATION | 82  |

| 4.3.1  | MIPS4K MODIFICATION AND VIRTUALIZATION SUPPORT      | 82  |

| 4.3.2  | MEMORY MANAGEMENT                                   | 83  |

| 4.3.3  | LOGICAL MEMORY ORGANIZATION                         | 86  |

| 4.3.4  | EXCEPTION VECTOR                                    | 86  |

| 4.3.5  | EXCEPTION RETURN                                    | 87  |

| 4.3.6  | TIMER                                               | 87  |

| 4.3.7  | MEMORY-MAPPED PERIPHERALS                           | 88  |

| 4.3.8  | MULTIPROCESSOR CONCERNS                             | 89  |

| 4.3.9  | RESULTS                                             | 89  |

| 4.3.10 | EVALUATION METHODOLOGY                              | 91  |

| 4.3.11 | PROCESSING OVERHEAD MEASUREMENT                     | 91  |

| 4.3.12 | COMMUNICATION OVERHEAD MEASUREMENT                  | 92  |

| 4.3.13 | MIXED SCENARIO MEASUREMENT                          | 93  |

| 4.3.14 | DISCUSSION                                          | 94  |

| 5      | FINAL CONSIDERATIONS                                | 97  |

| 5.1    | REVISITING RESEARCH QUESTIONS                       | 98  |

| 5.2    | RESEARCH PUBLICATIONS                               | 98  |

| 5.3    | LIMITATIONS, ONGOING AND FUTURE WORK                | 100 |

|        | REFERENCES                                          | 103 |

## 1. INTRODUCTION

Multi-purpose Embedded Systems (ES) are now considered as a solid reality in everyday's lives since each more new and exciting features and devices are available to customers. However, such a wide range of applications impacts directly on their design, constraints and goals. Also, embedded systems are increasingly counting on typical general-purpose computers' characteristics, such as the possibility for the final user to develop and download new applications onto the device throughout its lifetime [ZM00]. Within this context, embedded software itself has become a subjacent layer in the design flow unlike older approaches where hardware itself, or custom firmware used to be more prominent.

Despite this shift in perception, some traditional differences between general-purpose and embedded systems still remain [LP05]. Usually timing constraints are present along with a limited energy consumption budget and limitations regarding memory size. Still, the wide variety of predominant architectures present in ESs also contributes to increasing the difficulty in their design.

A relevant characteristic of embedded systems is the broad use of multiprocessed solutions, notably in the last decade [JTW05]. Combined with the aforementioned particularities, the use of multicore hardware requires a true change in the way embedded developers design their systems.

Therefore, virtualization, rather a successful technique exclusively applied on generalpurpose computers, arises as a possible solution to many of these problems, as it can increase ESs' performance, software design quality and security levels while reducing their manufacturing costs [Hei11]. However, due to the typical embedded constraints mentioned earlier, a lot of effort has been spent in order to demonstrate that virtualization can indeed improve the overall system quality at a reasonable cost [IO07], [BDB<sup>+</sup>08], [SCH<sup>+</sup>09], [CR10], [AFNK11].

Among all these efforts to apply virtualization on embedded systems, the main problems concern some of these systems' characteristics and the functionalities required by a virtualized platform, which can be conflicting most of the time. For example, Heiser [Hei08] highlights the need to run unmodified guest OS and applications besides providing strong spatial isolation to improve security. In [AG09], the need for low overhead components are said to be fundamental. The main problem, however, is that it is very difficult to target all such constraints at once.

Another challenge is that these conflicting needs have a strong relationship with the hypervisor's implementation as it depends completely on the underlying hardware. Thus, the architecture itself (and the characteristics of its Instruction-Set Architecture - ISA) can make the use of embedded virtualization feasible.

### 1.1 Motivational Examples for Embedded Virtualization

The first case for virtualization on embedded systems consists of allowing several operating systems to be executed concurrently. Here, the use of different operating systems can be specially classified in two different scenarios:

- 1. when legacy software must co-exist with current and incompatible applications; and

- 2. when it is desired to separate real-time software from user interface applications, by using either different or separated Operating Systems (OSs).

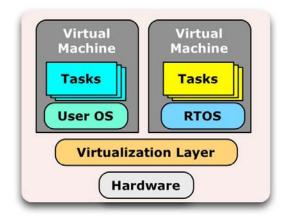

In this first case, software development quality can be increased, since the designer can choose, among several OSs, the one most suitable for the application or even the one with the best cost/performance ratio. Moreover, the time required to develop an application can be reduced, since in the case it is offered the support to a given OS, any former application can be reused without the onus of rewriting it [Sub09]. Figure 1.1 shows the basic use of virtualization, with the consolidation of several OSs in the same hardware platform.

Figure 1.1 – Consolidation of several OSs using virtualization

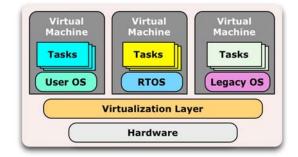

Furthermore, this approach offers advantages in achieving a unified software architecture that can be executed on multiple hardware platforms. In this case, a current issue in embedded systems - software portability - could be widely affected and developers would be able to satisfy the increasingly restricted time-to-market. The combination of real-time, legacy and general-purpose operating systems in the same device can be easily achieved with virtualization, as Figure 1.2 shows.

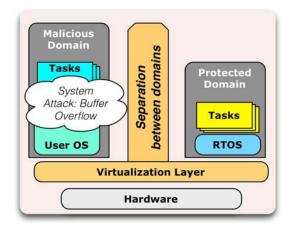

Besides, security is another important issue to be managed by virtualization, since it provides an environment that protects and encapsulates embedded operating systems and other software components. Initially, the idea of using an application-specific operating system apart from the Real-Time OS (RTOS) is encouraged as user attacks would only be able to cause damages at the user OS, thus keeping the RTOS and specific system components safe.

Figure 1.2 – Legacy software coexist with newer applications

This approach is depicted in Figure 1.3, where the scenario containing separate OSs and an ongoing user attack is shown. Nevertheless, in order to actually guarantee that virtualization will improve security, the underlying virtualization layer has to be significantly more secure than the guest OS.

Figure 1.3 – User attack blocked by virtualization's inherent isolation

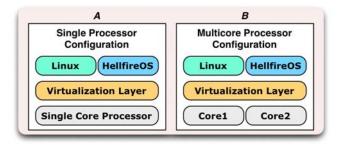

In multi-core architectures, there are different ways of utilizing the many system processors. A very common arrangement consists of running a single OS onto the processors, thus creating a symmetric multiprocessing (SMP) configuration. This approach brings the main advantage of making load balancing across the processors straightforward. When virtualization is adopted in multiprocessed architectures, there is the possibility of reducing the total number of physical processors. Figure 1.4 illustrates a configuration in which this is possible.

However, using different and multiple OSs in the same MPSoC can be an attractive option. Virtualization allows different virtual machines to provide services independently, which is a safer approach. A single software in control represents a single failure point and whenever the system crashes all the cores must be restarted. Although the hypervisor may represent a single point of failure it can be a safer approach provided it is implemented carefully.

In this case, an asymmetric multiprocessing (AMP) configuration is used, where each processor has its own separate OS, responsible for scheduling its own tasks. AMP is a configuration

Figure 1.4 – Different processor configurations: a) single physical core; b) multicore

that takes advantages of virtualization since it provides the arbitration of resources' usage between the virtual machines, avoiding the user OS to cause unexpected behavior on the RTOS [Her09]. If no virtualization is used, the only way to achieve such separation is by doing it manually, which is complex and more suitable to errors. Still, the virtualization layer can be responsible for mapping every virtual machine on each core of the multi-core processor or even map a single OS onto multiple cores, creating an SMP subset of cores [SLB07].

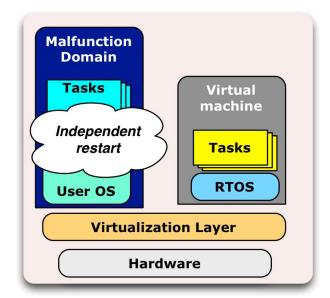

Thus, the reliability of AMP systems can be increased by guaranteeing resources (memory, devices) separation and the ability to, independently, restart virtual machines, as depicted in Figure 1.5. It is important to notice that this can also be used when an AMP subset of processors is present in the MPSoC.

Figure 1.5 – Improved reliability for AMP architectures

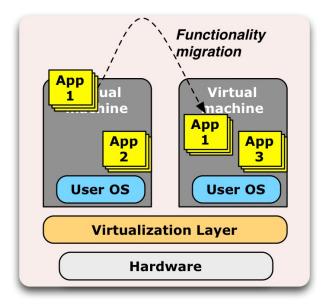

When working with SMP configurations, where several equal OSs are executing in different virtual machines, workload balancing can be improved, by migrating application between machines. It is then possible to exchange functionality between virtual machines, providing the opportunity for reuse and innovation. This is showed in Figure 1.6. The advantages of migration in embedded systems has been widely proved throughout the years [SP09], [BABP06], [NAMV05].

Figure 1.6 – Migration between virtual machines using the same OS on the same ISA

All these scenarios are suitable enough to be used in non-critical embedded systems, as multimedia mobile devices [ABK09], [YKY10]. Specially, as consumer demands continues to grow, stricter time-to-market tends to be more present and virtualization can enable their achievement.

Despite of typically being a very resource consuming technique, virtualization has been considered for some researchers to be used in critical embedded systems, such as in avionics [KW08]. Usually, security sensitive or mission critical systems need a protected environment [For10]. Then, these sensitive parts have their own OS and the virtualization layer separates them from non-trusted OSs and applications.

The separation provided by virtualization allows other scenarios. For example, when some parts of the system are required to boot up faster than others. For instance, a car or a camera must have some of their functions available at a really fast pace (tens of milliseconds after power on). A general-purpose OS will take much longer, therefore, virtualization can separate the functions to be run in exclusive virtual machines, boosting their boot time.

Separation also allows license protection to be achieved because proprietary application can be completely isolated from GPL OS. Intellectual Property (IP) protection can rely on virtualization's inherit separation, since private modules are safe from user's inappropriate handling. Firmware over the air (FOTA) upgrades could also be easier to be made with virtualization besides allowing that only a given part of the system reboots after the upgrade. Easier migration would allow extensive use cases for pervasive computers, as virtual machines could migrate among different devices, leading to a whole new level of remote device usage [Rud09].

### 1.2 Research goal and questions

**Research goal:** The goal of this research consists in studying the virtualization technique to the point of proposing a suitable way for it to be adopted in multiprocessed embedded systems.

For this research goal to be achieved, two main research questions had to be made along the way.

- 1. What is the impact of the architecture diversity typically found in ESs in employing the virtualization technique?

- 2. Considering the existing virtualization implementation approaches in general-purpose computers, which one is more suitable for a given embedded environment?

**Research question 1:** There are some characteristics desirable in an ISA that ease the implementation of virtualization in it. Classic studies of Popek and Goldberg [PG74] introduce a classification of the instructions of an ISA (Instruction Set Architecture) into three different groups, in order to derive the virtualization requirements:

- Privileged instructions: those that trap when used in user mode and do not trap if used in kernel mode<sup>1</sup>;

- 2. *Control sensitive instructions*: those that attempt to change the configuration of resources in the system, and;

- 3. *Behavior sensitive instructions*: those whose behavior or result depends on the configuration of resources

Those works first stated that, in order to virtualize a given machine, sensitive (control and behavior) instructions must be a subset of privileged instructions. However, even if that is not the case of a given ISA, virtualization can still be achieved. For instance, the Intel's x86 family counts on hardware support to overcome the fact that not all of its sensitive instructions are a subset of privileged instructions.

In embedded systems, since there is more than one predominant architecture, each case should be analyzed individually. In this research we chose to study virtualization impacts on a MIPS-based platform, since this architecture is widely adopted, being present in video-games, e-readers, routers, DVD recorders, set-top boxes, etc. Moreover, this research is placed in the context of the Embedded Systems Group (in Portuguese, Grupo de Sistemas Embarcados) at PUCRS, and there were previous researches that employed the same architecture, thus reusing and expanding the group's knowledge in this matter. Still, MIPS is compliant with Popek and Goldberg virtualization requirements, easing its implementation.

$<sup>^1 \</sup>text{User}$  and Kernel mode are operation modes provided by the architecture that allows safer execution of applications dividing what is privileged and what is not.

Unfortunately, the diversity of architectures used in embedded systems impacts on the fact that it is not possible to use a common virtualization solution to all of them. Since virtualization is also about improving the utilization of the underlying hardware, each platform should be carefully studied so a suitable proposal can be issued.

**Research question 2:** Mainly, the virtualization layer is responsible for providing several virtual machines and enabling them to execute their OSs individually, without one interfering in another. There are several ways of doing so, and the main techniques are:

- Trap and emulate, where each privileged instruction that is executed by the virtual machine is emulated by the virtualization layer, with large performance penalties;

- Paravirtualization, where each privileged instruction that would be executed by the virtual machine's OS is replaced by a proper and acknowledged system call, provided by the virtualization layer, so that no emulation is required. This approach requires access to the virtual machine OS source code and some extensive changes might be necessary;

- Hardware support, where the processor is aware that virtualization is a possibility and some level of support is added. In this case, the processor needs to offer support and virtual machine OSs can run without source code modification as long as they are ported to that architecture.

In many cases, paravirtualization offers the possibility of reducing virtualization overheads at the cost of needing to change the OS source code. However, we always believed this was not the best solution for embedded systems, since software complexity has already been increased due to the numerous features desired each more by users. So, using virtualization - which can improve design quality - at the cost of complex and numerous OS change is conflicting. Still, once the market started to see the virtualization potential, it was only a matter of time before leading market architectures such as ARM and PowerPC provided their own virtualization support. Finally, considering the timeframe in which this research has been developed, we propose some hardware modification so that a given MIPS platform counts on native virtualization support.

#### 1.3 Contributions and original aspects

Historically, embedded systems have been inspired by many techniques previously deployed in general-purpose computers that presented specific challenges when thought for embedded environments. Virtualization fits in that category. However, its implicit processing overhead and expressive need for memory can be considered the main challenges when bringing it to embedded platforms.

By answering the proposed research questions, this research contributes by investigating suitable ways of using virtualization in multiprocessed embedded systems providing an architecture that offers hardware support. Still, a virtualization model was conceived to offer different mapping strategies, that can be extended in the future. Some initial investigation regarding real-time achievement in virtualized multiprocessed embedded environments was also performed. And last, but not

least, from that model two different implementations were made in MPSoCs, as a proof-of-concept. Our implementation modified MIPS-based processors and it is important to highlight that, by the time this dissertation was developed, there was no official MIPS support to virtualization, so that the modifications suggested in the architecture - aiming multiprocessed platform - are the main original aspects of the research.

#### 1.4 Structure of this Dissertation

The remainder of this dissertation is organized as follows.

Chapter 2 - Background Concepts . This chapter presents background concepts especially focused on virtualization terms and known strategies that serve as basis to the entire research. This chapter is important considering this research context as it is placed in the embedded systems' field and virtualization concepts are not so widely known among researchers.

Chapter 3 - Literature Review. This chapter presents literature on embedded virtualization, showing that many researches prefer the use of paravirtualization. Also, since virtualization is also used by non-academic entities, commercial solutions are presented.

Chapter 4 - Virtualization Model Attemps. This chapter presents three different attempts to virtualization model in MPSoCs. First attempt considers using paravirtualization techniques while the following attempts propose hardware modification to MIPS-based processors.

Chapter 5 - This chapter presents the research validation process adopted throughout the research, discusses the contributions of this research, and disclose the threats to the validity of the contributions. The chapter concludes this dissertation with suggestions for future work.

## 2. BACKGROUND CONCEPTS

### 2.1 Embedded Systems

This section presents basic concepts regarding current embedded systems. The reader who is familiar with those concepts may skip to the next section.

A very common definition for embedded systems regards its strictness to a given application. Opposed to general-purpose systems, embedded systems used to be relatively simple devices, with limited and fixed number of software tasks. Embedded systems are present in a very wide range of applications, from consumer electronics to industrial automation among many others [Noe05], as shown in Table 2.1.

| Source: Adapted from [Noe05]              |                                   |  |  |

|-------------------------------------------|-----------------------------------|--|--|

| Field                                     | Embedded device                   |  |  |

|                                           | Digital and analog TV             |  |  |

| Consumer electronics                      | Games toys                        |  |  |

| Consumer electronics                      | Home appliances                   |  |  |

|                                           | Internet appliances               |  |  |

|                                           | Dialysis machines                 |  |  |

| Medical                                   | Infusion pumps                    |  |  |

| Medical                                   | Cardiac monitors                  |  |  |

|                                           | Prosthetics                       |  |  |

|                                           | Smart sensors, motion controllers |  |  |

| Industrial Automation and Control         | Man/machine interface devices     |  |  |

|                                           | Industrial switches               |  |  |

|                                           | Cell phones                       |  |  |

| Notworking and communications             | Pagers                            |  |  |

| Networking and communications             | Video phones                      |  |  |

|                                           | ATM Machines                      |  |  |

|                                           | Entertainment centers             |  |  |

|                                           | Engine controls                   |  |  |

| Automotive                                | Security                          |  |  |

|                                           | Antilock break control            |  |  |

|                                           | Instrumentation                   |  |  |

|                                           | Flight management                 |  |  |

| Aerospace and Defense                     | Smart weaponry                    |  |  |

|                                           | Jet engine control                |  |  |

|                                           | Printers                          |  |  |

| Commercial Office /Home Office Automation | Scanners                          |  |  |

| Commercial Office/Home Office Automation  | Monitors                          |  |  |

|                                           | Fax machines                      |  |  |

Table 2.1 – Embedded applications' examples Source: Adapted from [Noe05]

Such a wide range of applications and devices, and their increasing amount of features has severely impacted on their design throughout the years. Embedded systems used to be relatively simple devices with severe hardware constraints, like memory use, processing power and battery life. Mostly, their functionality was determined by hardware modules with few software usage. In this case, software layers consisted, basically, of device drivers, task scheduler and some control logic, resulting in software with low complexity. Besides, these systems used to be closed, which means that during their lifetime no change in the software was required [HNN05]. This scenario, however, has already changed. It is very common that general-purpose applications are desired to be executed on embedded systems. Also, applications written by developers that have little or no knowledge at all about embedded systems constraints can also be employed [ZM00].

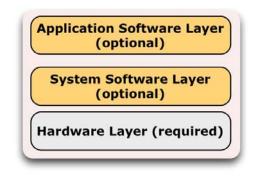

Nevertheless, we notice a rupture in a classical model of embedded systems' design [Noe05], as presented in Figure 2.1. Here, software and application layers are considered to be *optional* while current trends present the complete opposite. Each more, designers tend to implement system tasks in software and applications layers, since it allows higher flexibility, easier debug and higher reuse rates.

Figure 2.1 – Former Typical Embedded System Model Source: Adapted from [Noe05]

Still, some of the traditional differences between general-purpose computers and embedded systems remain [LP05]. For example, even on high-end multimedia entertainment-driven embedded systems, some real-time constraints are present and the energy consumption is often a matter of concern. Since these devices are supposed to operate through several hours (up to days) without any battery recharge the processor frequency choice is impacted and usually lower frequency rates<sup>1</sup> are compatible with the energy consumption goals.

Another common restriction is memory usage. Modern embedded devices are designed to be cost effective and excessive memory opposes to that. Memories are a high energy consuming resource, and frequently represent a cost factor issue [HPHS04].

Embedded systems present a varied set o constraints that directly impact on their designs. While some ESs are more concerned in area and energy consumption reduction, such as cell phones,

$<sup>^1\</sup>mbox{Valid}$  when compared to higher processor frequencies used in no-battery dependent devices, such as desktop computers.

others need the most predictable and deterministic behavior in spite of pure performance levels, such as some avionic systems. Such constraints impact on the processor choice so that there are several predominant architectures in ESs, such as ARM, MIPS, PowerPC and even some Intel Atom versions. On the other hand, general-purpose systems are mainly implemented onto the x86 architecture.

Finally, embedded systems are becoming more and more part of everyday life, being increasingly used in mission and life-critical scenarios as well as entertainment gadgets [Wol03]. Such a wide range of applications enables new techniques to be deployed and virtualization can bring many advantages in this scenario.

### 2.2 Classical virtualization

This section presents classical virtualization concepts and the reader who is familiar with those concepts may skip to the next section.

Computer virtualization is an old technique invented by IBM in the early 1960's aiming to improve hardware utilization. Also, software compatibility was another requirement as software needed to be compiled to each specific hardware and could not be reused among other systems. They caused a revolution in terms of commercial success - the hardware could evolve and the software could remain the same.

In the early times mainframes were a common technology and IBM's virtualization was responsible for partitioning a single hardware into several virtual platforms. Each virtual platform was able to execute its own applications, including older versions of OSs. After a while, mainframes started being replaced by workstations and the need for this type of virtualization ended naturally throughout the years.

Later, in 1999 VMware released the VMware Workstation, a product tailored to the x86 architecture that allowed the user to run multiple operating systems on a single desktop computer. By that time, it already was well established that the x86 architecture was the leader in terms of standards and also, the architecture itself was mature enough to hold the overhead of a virtualized system.

Still, enterprise market took a lot of advantage in using virtualization techniques, since the same workload could be consolidated on fewer physical machines, which represented a huge cost reduction factor. Security is also improved, since a failure within a given virtual machine does not spread throughout the system [Hei08].

Nevertheless, although it causes a single hardware point of failure, virtualization still is considered a safer approach when comparing to non-virtualized systems. Usually, service interrupts are not caused by hardware failures. Instead, the main problem usually is the use of non-reliable software. In that case, failures can be often related to the software size, for example, operating systems, which are usually big, tend to have many flaws. Therefore, if the virtualization layer is small (when comparing to a classical OS) virtualization can be considered a safer approach.

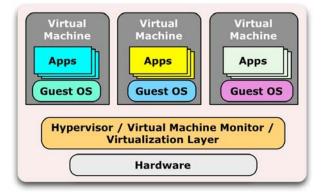

#### 2.2.1 Virtualization layer - the hypervisor

In virtualization, the leading role is played by a software known as the *hypervisor*, *Virtual Machine Monitor* - VMM, or *Virtualization Layer*. The hypervisor allows the creation and maintenance of multiple virtual machines, being responsible for their isolation by providing an abstract hardware layer. One of the most important roles played by the hypervisor is to arbitrate the access to the underlying hardware, so that *guest OSs* (OSs executing on each virtual machine) can share the physical resources. It is possible to say that the hypervisor manages virtual machines, composed by their OS and applications, in a similar way that a native OS manages its processes and threads. Figure 2.2 shows a generic idea of hypervisor, since it controls the hardware and provides the desired abstraction to the virtual machines.

Figure 2.2 - Generic Hypervisor Model

Since this similarity exists, it is not surprising that details regarding the implementation of a hypervisor are also present in modern operating systems' implementation. Therefore, in order to understand how a hypervisor works, some OSs concepts are important, such as the *privilege scheme*. Most modern operating systems work within two modes:

- kernel or supervisor mode, in which almost any CPU instructions are allowed to be executed, including *privileged* instructions - those that deal with interrupts, memory management, among others. Operating systems are executed in kernel mode, and;

- user mode, that basically allows the execution of instructions needed to calculate and process data. User applications run in this mode, and can only access the hardware by asking the kernel through system calls.

Originally, the user/kernel mode scheme was adopted due to RAM's division into pages. Before executing a given privileged instruction, the CPU must check a right 2-bit code associated with that instruction. Privileged instructions require a 00 code whereas the least privilege is conceded with a 11 code<sup>2</sup>.

$<sup>^{2}</sup>$ as a 4-bit code, four levels of privilege are allowed, with 00 being the highest and 11 the lowest

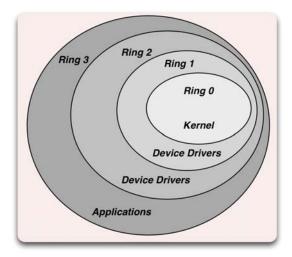

This scheme is often referred to as *protection rings* where rings are arranged in a hierarchy from the most to the least privileged. Therefore, in most operating systems, *Ring 0* (00 2-bit code) is the most privileged level and is able to interact directly with the physical hardware. Figure 2.3 depicts a common representation of the privilege rings scheme.

Figure 2.3 – Typical Privilege Rings of Modern CPUs

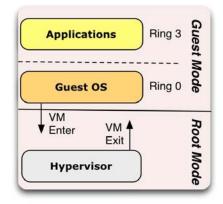

In a virtualized architecture, the hypervisor is the only software executed in the *Ring 0* privilege level. This has a severe consequence for guest OSs: they no longer run in Ring 0, instead, they run in Ring 1, with fewer privileges. This is known as ring de-privileging and allows the hypervisor to control guest OS accesses to resources, avoiding, for instance, one guest OS either to interfere in a neighbor's memory or to control hardware resources improperly. Ring de-privileging technique is exposed in Figure 2.4.

Figure 2.4 - Ring de-privileging caused by the hypervisor

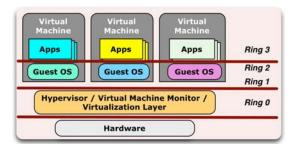

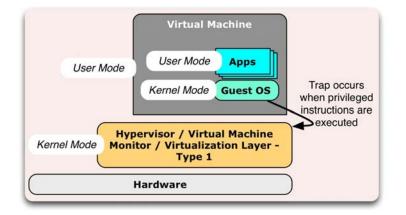

*Hypervisor Typology.* According to [Ros04], there are two main approaches to implement the virtualization technique, by using either hypervisor of type 1 (depicted in Figure 2.5) or type 2 (depicted in Figure 2.6).

In hypervisor type 1, also known as *hardware-level virtualization*, the hypervisor itself can be considered as an operating system, since it is the only piece of software that works in kernel mode, like depicted in Figure 2.5. Its main task is to manage multiple copies of the real hardware just like an OS manages multitasking.

Figure 2.5 – Hypervisor Type 1

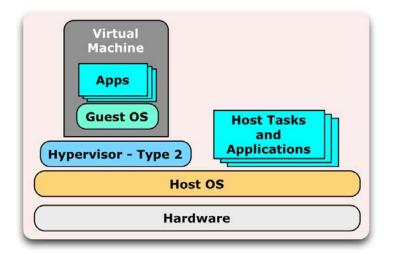

In type 2 hypervisors, also known as *operating system-level virtualization*, depicted in Figure 2.6, the hypervisor itself can be compared to another user application that simply "interprets" the guest machine's instructions.

Figure 2.6 – Hypervisor Type 2

*Requirements.* The most common requirements and the goals to be achieved by a hypervisor are [Ros04]:

- compatibility, since the hypervisor needs to provide the execution of legacy software;

- performance, a measure of the virtualization overhead, where the ideal is to run the virtual machine at the same speed as the software would run on the real machine; and

- simplicity, since a hypervisor failure leads every virtual machine running on the computer to fail. Also, to provide secure isolation among virtual machines requires a free of bugs' hypervisor so that attackers could not use it against the system.

#### Virtualization Challenges

In its first years, virtualization provided by IBM implemented a hypervisor that allowed virtual machines to be executed, as expected. The main problem, is that it was an extremely robust approach in which every privileged instruction executed by a virtual machine caused a *trap*, since it was running in a less privileged ring. Virtualization must be as transparent as possible and the hypervisor is responsible for it.

One of the main problems faced by designers when virtualization started being noticed again, back in the 1990's, was that CPU architectures, like the popular x86, were not designed to be virtualizable. Certain instructions, when executed in unprivileged mode, are simply ignored instead of causing the CPU to trap. For instance, instructions like the POPF that disables and enables interrupts represent trouble for the hypervisor.

*Binary Translation.* When VMWare launched VMWare Workstation back in 1999, these aforementioned issues of the x86 architecture hadn't been solved yet. So, VMWare used a technique known as *binary translation*, used also in Intel Itanium processor. Nevertheless, VMWare version was a lot lighter than Itanium's, which had to translate from x86 Instruction Set Architecture to IA64 ISA while VMWare's binary translation was based on an x86 to x86 translator, which, in many cases, just had to copy the exact same instruction.

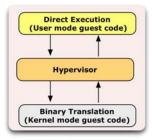

At run time, VMware translated the binary code coming from a guest OS and stored the adapted code in a memory structure known as Translator Cache (TC). It is important to highlight that user applications running on the top of guest OSs were not translated, since they continued to be executed in a non-privileged ring (as they would, if run natively). This scheme is depicted by Figure 2.7.

Figure 2.7 - Binary Translation for OS - Direct Execution for Applications

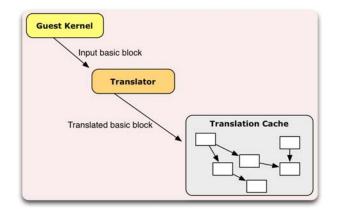

Analyzing this scheme, it is possible to see that the kernel code is the one that needs to be translated. This leads to the conclusion that the guest OS kernel is no longer executed - it is merely an input for the binary translator, as we can see in Figure 2.8.

The translation, in most cases, only copies the original code. Otherwise, when privileged instructions are desired or when hardware manipulation is required, the translator has to change the original code to either safer non-privileged instructions or to instructions with code reference to the virtual hardware. These manipulations can cause the translated code to be considerably larger than the original one.

Figure 2.8 – Guest OS Kernel Code is an input to the Binary Translator

When compared to full virtualization, which causes traps at each privileged instruction, provided by IBM, the technique of replacing code with safer instructions presents higher performance. Although, in some cases, the overhead found for this virtualization approach is not negligible. This occurs in some special cases:

- system calls;

- I/O access, interrupts and DMA;

- memory management; and

- unusual code situations, such as self-modifying and indirect control flows, among others<sup>3</sup>.

*System calls.* System calls are performed by user applications whenever they need to request the use of a privileged instruction. To perform system calls, x86 provides two simple instructions: SYSENTER (or SYSCALL) and SYSEXIT, that are responsible for beginning and finishing a system call, respectively.

Otherwise, additional work is needed to use virtualization due to the way virtualization (especially by binary translation) deals with privileged instructions: it replaces them with a slightly less privileged instruction that performs the same task. When using system calls, the main problem is that when SYSENTER is executed, it is sent to a privilege page in memory, where the OS is supposed to be. Instead, it finds the hypervisor which must emulate every system call, by translating its code and then coming back to the translated kernel code. It is quite clear that this is responsible for a big overhead, measured in VMWare [WCC<sup>+</sup>08], resulting that:

- a native system call takes, in average, 242 cycles, while

- the binary translated system call with a 32-bit guest OS takes, in average, 2308 cycles.

$<sup>^{3}</sup>$ This situation will not be considered for our analysis, since even in native OS, non-virtualized systems, it causes trouble for the operating system.

*Memory Management.* Another big challenge when implementing virtual machines is how the hypervisor interacts with the memory. Regular OSs maintain page tables that help during the translation of virtual memory pages into physical memory addresses. Since this is a much disseminated concept, modern x86 CPUs already provide support for this memory scheme directly in hardware. Thus, the translation itself is performed by the Memory Management Unit - MMU. For instance, in the x86 architecture, the current address is kept in the *CR3* register, also known as the hardware page table pointer, whereas the most used information are cached in the TLBs.

In virtualization, this has to be thought differently, since the guest OS cannot access the real page tables. Instead, it sees page tables executed on an emulated version of the MMU. This scheme gives the guest OS the illusion that it can translate the addresses itself, but truly, what happens is that the hypervisor is the only one to be dealing with it. Therefore, the real page tables are hidden from the guest OS and managed by the hypervisor, still being run on the real MMU in an approach named as *shadow page tables*.

Moreover, to maintain this approach, each time that the guest OS modifies its own page mapping, the virtual MMU module will trap the modification in order to adjust its shadow page table. Unfortunately, it causes a severe overhead: depending on the changes in the page table, the overhead takes from 3 to 400 times more cycles that a native execution [AA06]. Thus, memory intensive applications may suffer from a very big overhead due to memory management depending on how it is implemented.

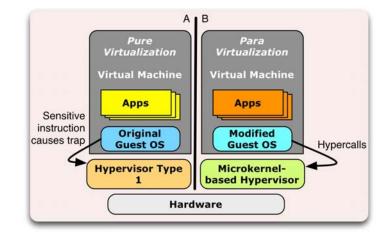

*Paravirtualization.* When using virtualization at hardware level (type 1 hypervisor of 2.5) without hardware support, the hypervisor is in charge of translating instructions whenever the virtual machine tries to execute a privileged instruction (I/O request, memory write etc), which causes a trap into the hypervisor. This is known as pure virtualization and is often a very expensive way of dealing with virtual machines [Wal02].

Therefore, another option when dealing with hardware level virtualization is named as *paravirtualization* and it can be used to replace sensitive instructions of the original code by explicit hypervisor calls (known as *hypercalls*). In reality, the guest OS is acting like a normal user application running on a regular OS, with the difference that the guest OS is running on the hypervisor. When paravirtualization is adopted, the hypervisor must define an interface composed by system calls to be used by the guest OS. Still, it is possible to remove all sensitive instructions of the guest OS, forcing it to use only hypercalls. Besides working on hardware that is unsuitable for pure virtualization, it can also bring performance boost.

In that sense, paravirtualization is not so much different from binary translation. While binary translation changes privileged code instructions into "harmless" code at run time, paravirtualization does the same, but in the source code. Both approaches present pros and cons. For instance, changes made still in the source code are more flexible than those done on the fly, which must happen quickly. Paravirtualization eliminates many unnecessary traps to the hypervisor when compared to binary translation. On the other hand, it requires full access to the source code, which can be faced as a huge disadvantage in some cases.

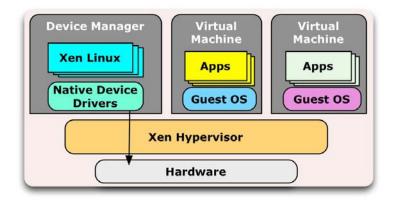

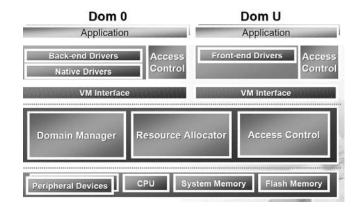

In paravirtualization, the hypervisor provides hypercall interfaces for critical kernel operations such as memory management and interrupt handling. Although they exist for various operations, they will only be accessed when needed. Thus, the same way that VMware became known when adopting binary translation, Xen's paravirtualization solution was widely adopted.

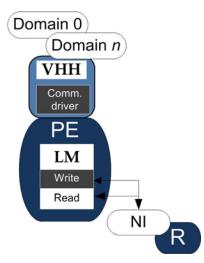

One of the best features of the Xen implementation of virtualization is in the way I/O is handled: Xen proposes a concept of a privileged virtual machine responsible for dealing with those operations, named as *Domain 0*. This virtual machine links the simplified interfaces that appear to the VMs as the real native drivers, by requiring no emulation whatsoever. The concept proved out to be so good that even VMWare adopted it in newer versions of ESX server, by implementing paravirtualized network drivers. Figure 2.9 depicts Xen's scheme of paravirtualization.

Figure 2.9 – Xen's paravirtualization approach

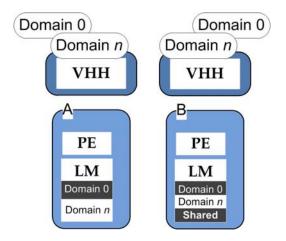

For comparison purposes, the difference between pure virtualization and paravirtualization is depicted in Figure 2.10. In part A of the figure, pure virtualization is shown. In this case, whenever the guest OS calls a sensitive instruction, a trap is caused to the hypervisor, which emulates the instruction behavior and returns the proper results. In part B, paravirtualization is showed. The guest OS has been modified in order to make hypercalls instead of containing sensitive instructions. In this case, the trap is similar to the one that occurs in non-virtualized systems, whenever a user application makes an OS system call.

Hardware Accelerated Virtualization. Since virtualization reached really noticeable use within the last years, challenges to achieve a better performance started to be a constant claim by the enterprise market, since software techniques were not good enough. Then, processor companies, like AMD and Intel, took advantage and increased their market share by releasing hardware support for virtualization.

Besides making existing execution modes virtualizable, basically, what Intel and AMD technologies did was to add a new execution mode to their processors, allowing the hypervisor to safely and transparently use direct execution when running virtual machines. This new execution mode increases the performance since the amount of traps needed to implement virtual machines is drastically reduced.

However, the first generation of hardware virtualization support did not reduce all overheads to minimum levels, as it would be expected. This occurred, especially because this first release was not an improvement of neither binary translation nor paravirtualization. Instead, the first idea was to eliminate the original reasons that did not allow x86 based machines to be virtualized. Here, we can highlight the need to allow every privileged instruction to cause a trap, when executed in a different privilege level. Still, a new execution mode was created, forcing hypervisor to be executed in the -1 level of the privilege ring (root mode).

The biggest advantage is that the guest OS runs at its intended privilege level (ring 0) and the hypervisor runs at an even higher privileged ring. Therefore, guest system calls do not require the hypervisor to interfere: as long as they do not involve critical instructions, the guest OS can provide kernel services to the user applications as easily as if it was a native execution, as depicted in Figure 2.11.

Figure 2.11 – Hardware support to virtualization

The problem faced by this implementation is that even though it is done in hardware, each transition from the virtual machine to the hypervisor (namely, VMexit and VMentry) requires

a fixed number of CPU cycles, which, depending on the internal CPU architecture can take from a few hundred cycles up to a few thousand cycles.

Thus, when Intel VT-x or AMD SVM (or AMD-V) has to handle with relatively complex operations such as system calls (which would be heavy anyway), the impact of the VMexit/VMentry switching can be considered light. On the other hand, if the actual operation to be emulated is simple, the overhead is significantly heavier.

Hardware support improvement. Managing the virtual memory of different guest OSs by translating their virtual pages into physical pages can be extremely CPU intensive. Each update of the guest OS page tables requires some update in the shadow page table. This is rather bad for the performance of software-based virtualization solutions but it definitively affects the performance of the earlier hardware virtualization solutions, since it causes a lot of VMexit and VMentry calls.

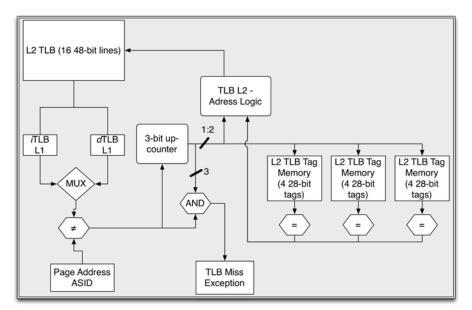

Then, with the second generation of hardware virtualization technologies, the AMD's nested paging and Intel's extended page tables (EPT), the problem was partially solved by providing a TLB that keeps track of both the guest OS and the hypervisor memory management. Figure 2.12 depicts how this approach works. The CPU with hardware support stores the virtual -to-physical memory mapping of the guest OS and also the physical memory to real physical memory transition of the guest OS. To do that, the TLB has a new specific tag for each virtual machine, called the Address Space IDentifier (ASID). It allows the TLB to know which TLB entry belongs to which virtual machine. Thus, the virtual machine does not flush the TLB: the entries of different virtual machines coexist in the TLB.

Figure 2.12 – TLB approach with Nested/Extended Page Tables

This approach makes the hypervisor implementation a lot simpler as it prevents the need to update the shadow page tables constantly. However, it makes the virtual to real physical address translation to be a lot more complex if the TLB does not have the right entry. In order to compensate it, larger TLBs are used since TLB misses become extremely costly.

## 3. LITERATURE REVIEW

Virtualization is a consolidated technique which dates back more than 30 years, being primarily proposed by IBM. Throughout the years, two main approaches have been adopted to implement it successfully. In *full virtualization* an almost complete simulation of the actual hardware is performed, enabling Guest OSes to run unmodified. In *paravirtualization* Guest OSes need to be modified to run avoiding the excessive amount of traps that occur when a Guest OS tries to execute a privileged instruction (when executing outside of its intended privilege ring).

However, full virtualization per se usually suffers from a large overhead from the emulation of privileged instructions while paravirtualization demands Guest OSes to be modified, which can increase both engineering cost and system's time to market. Hence, a viable solution is the use of hardware support for virtualization. For example, general-purpose processor vendors such as Intel and AMD have released, respectively, VT (Virtualization Technology) and SVM (Secure Virtual Machine) virtualization support for the x86 architecture. Next section presents the main architectures with hardware support to virtualization in the embedded systems' context.

## 3.1 Hardware support in embedded architectures

The embedded market has seen hardware-assisted virtualization being introduced in the last years. Intel itself has introduced the Intel VT technology also for its embedded processors [Int11]. In this case, many virtualization tasks are performed in hardware, such as memory address translation, which reduces the overhead and footprint of virtualization software improving its performance. For instance, switching between two OSes is significantly faster when memory address translation is performed in hardware compared to software. Still, it has unified the Intel VT-x along with the Intel AMT (Active Management Technology) technology that provides remote management and maintenance capabilities, and Intel TXT (Trusted Execution Technology) that protects embedded devices and virtual environments against rootkit and other system level attacks, to provide the Intel vPro support aiming to reduce the total cost of ownership (TCO) of embedded systems.

IntelVT-x provides several hypervisor assistance capabilities, including a true hardware hypervisor mode, enabling unmodified guest OSs to execute with reduced privileges. For example, Intel VT-x is able to prevent a guest OS from referencing physical memory beyond what has been allocated to the guest's virtual machine. In addition, VT-x enables selective exception injection, so that hypervisor-defined classes of exceptions can be handled directly by the guest OS without incurring the overhead of hypervisor software interposing. While VT technology became popular in the server-class Intel chipsets, the same Intel VT-x technology is available in Intel Atom embedded mobile processors [Moy13].

ARM has also introduced a virtualization support with an extension for its ARM v7-A architecture [Arc13], ARM VE. Basically, it consists of introducing a new execution mode for the

hypervisor with higher priority than the supervisor mode. This enables the hypervisor to execute at a higher privilege level than the Guest OSes, and the Guest OSes to execute with their traditional operating system privileges, removing the need to employ paravirtualization techniques. Still, improvements of mechanisms to aid interrupt handling are available, with native distinction of interrupt destined to secure monitor, hypervisors, currently active Guest OSes or non-currently-active Guest OSes. This dramatically reduces the complexity of handling interrupts using software emulation techniques and shadow structures inside the hypervisor. Finally, the provision of a System MMU that aids memory management and supports multiple translation contexts and two levels of address translation and hardware acceleration and abstraction.

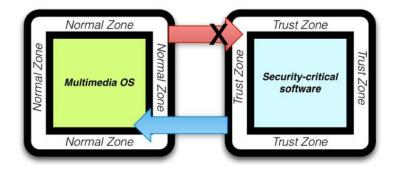

ARM still offers the ARM TrustZone technology. It enables a specialized, hardware-based form of system virtualization. Basically, it provides two different "zones": *normal* and *trusted*. Using this technology, a multimedia operating system (like the ones seen by the user in some smartphones) runs in the normal zone, while security-critial software runs in the secure zone. While secure zone supervisor mode software is able to access the normal zone's memory, the reverse is not possible, as shown in Figure 3.1. Thus, the normal zone acts as a virtual machine under control of a hypervisor running in the trust zone. However, unlike other hardware virtualization technologies, such as Intel VT-x, the normal-zone guest OS incurs no execution overhead relative to running without TrustZone. Thus, TrustZone removes the performance barrier to the adoption of system virtualization in resource-constrained embedded systems. TrustZone is orthogonal to ARM VE: the hypervisor mode introduced in VE enabled cores only applies to the normal state of the processor, leaving the secure state to its two-level supervisor/user mode hierarchy. Thus the hypervisor executes de-privileged relative to the trust zone security kernel. ARM VE also supports the concept of a single entity that can control both the trust- and the normal-zone hypervisor mode [Moy13].

Figure 3.1 – ARM TrustZone

Power.org (Power Architecture technology), announced virtualization support in the release of Power Instruction Set Architecture Version 2.06 [Pow12]. The document provides support for virtualization and hypervisors including a new guest mode and MMU extensions that enable the efficient implementation of hypervisors on the embedded Power Architecture platform. It allows a more efficient implementation of virtualization, partitioning of embedded systems, isolation of applications, and resource sharing. Freescale was the first to release platforms using processors that contain this extension.

Finally, in April of 2013 MIPS announced directions for future generations of processors to count with hardware support for virtualization. By the time this dissertation was written there were no commercial processors in the market using the technology. The main points concern offering another execution mode besides duplicating several structures to decrease virtualization overheads. It is important to notice that, by the time this research was developed, there was no MIPS hardware support to virtualization and that any similarity is just a mere coincidence.

## 3.2 Existing Hypervisors

Virtualization is a technique that offers many advantages and it is often found as a commercial solution. Therefore, this section brings some existing commercial and academic hypervisors.

**EmbeddedXEN Project.** EmbeddedXEN is an academic project of the XEN.org research group where the main target are embedded real-time applications. In this case, the hypervisor is executed in ARM cores, since this is one of the most used embedded processors. The EmbeddedXEN project provides to ARM developers a single multi-kernel binary image which includes XEN, Linux, miniOS and a XenomaiRT extension adapted to run onto embedded systems. Virtualization and isolation mechanisms are fully relied on the XEN hypervisor for general purpose computers. The main goal of this project is to provide viability and performance evaluation of the embedded virtualization. It is an open-source project and it can be used in any device, although the Server Xen version is not open-source which can restrict its use.

In terms of architecture, EmbeddedXEN creates a page table for each guest OS when the guest domain is created, in order to support virtual memory systems. Though some RTOSs do not use any virtual memory technique, using the physical memory itself, the hypervisor can map the physical memory allocated by a guest RTOS into the same virtual memory, statically. At run time, the guest OS is executed as if it was using a physical memory, being isolated one from another by the page table provided by the hypervisor. This is a very simple approach which enables to use unmodified OSs with the virtualization solution although it may cause paging failures [Pa09].

To summarize the main characteristics of the EmbeddedXEN approach, we can highlight: (i) in cases of exception handling, system calls are interpreted by the hypervisor, using software interrupts; (ii) memory mapping is done by mapping both hypervisor and visitors' domain (kernel and user process) at the same memory space, and; (iii) the access control domain is used to prevent users from accessing a given process in kernel space memory from the user space memory [org12]. Figure 3.2 depicts the internal structure of the hypervisor, based on the general purpose's version of Xen.

**OKL4.** Implemented by OK Labs (Open Kernel Labs), this hypervisor (named microvisor by the developers), is an Open Kernel system which offers support to the virtualization technique.

Figure 3.2 – EmbeddedXen Hypervisor Approach Source: [org12]

Basically, it is an L4 family microkernel commercially distributed hypervisor with low overhead rates, [Hei09]. It has a high performance IPC (Inter-process communication) message exchange mechanism, which helps the low overhead virtualization. A system call, that causes a trap triggered by any virtual machine, calls the microkernel exception manager, converting this event into an IPC message to the guest OS. The client deals with this process as a normal system call and the answer is returned through another IPC message [Hei09]. Still, the OKL4 uses IPC to manage guest OS interrupt calls and to allow the communications of device drivers and the synchronization of system components including the virtual machine's. OKL4 uses an efficient resource sharing management, where memory regions can be shared by different address spaces mapping. In order to prevent unprivileged access, these memory regions respect system's permissions [Hei09]. Figure 3.3 depicts an example of this approach.

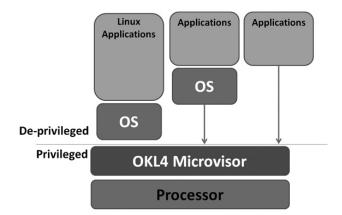

Figure 3.3 – OKL4 Hypervisor Approach Source: Adapted from [Hei09]

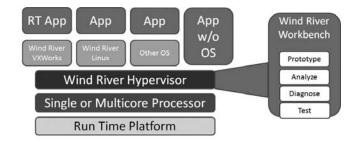

Wind River Hypervisor. An integral part of Wind River's Multicore Software Solution, Wind River Hypervisor focuses on high performance, small footprint, determinism, low latency and high reliability [Riv13]. In terms of processor, it supports single and multicore processors based on Intel and PowerPC architectures and it integrates with VxWorks and Wind River Linux. It also enables devices to be assigned to virtual boards as it provides device and memory protection between virtual boards.

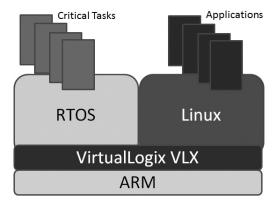

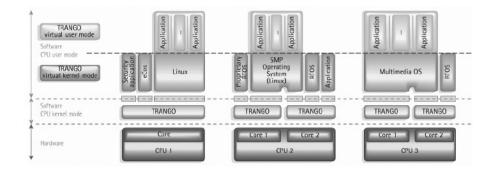

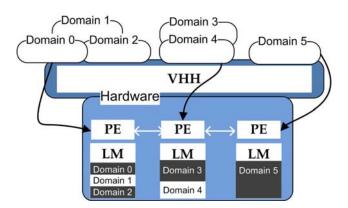

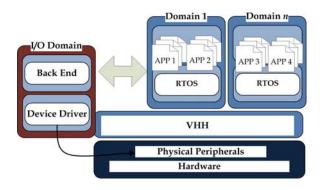

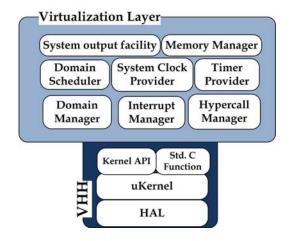

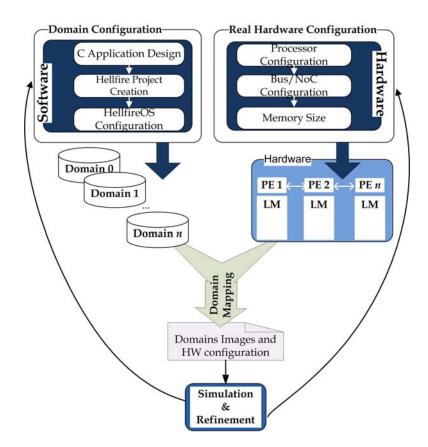

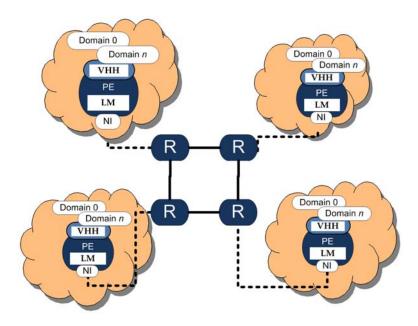

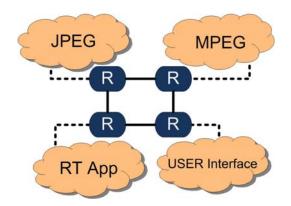

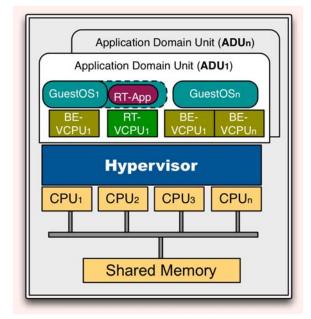

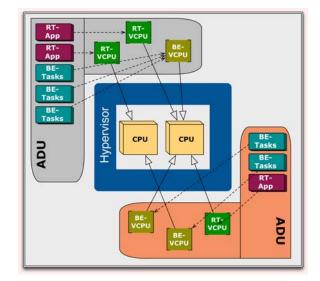

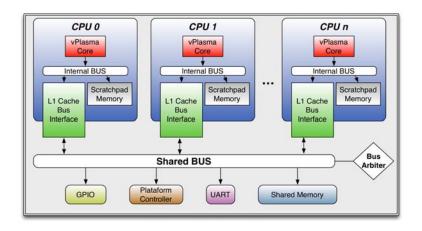

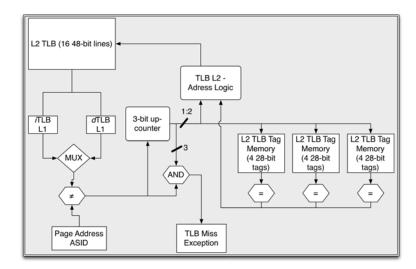

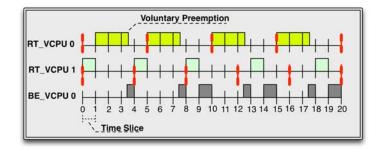

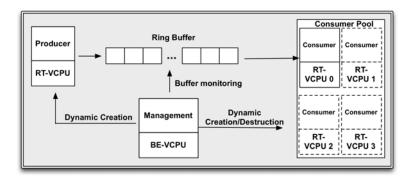

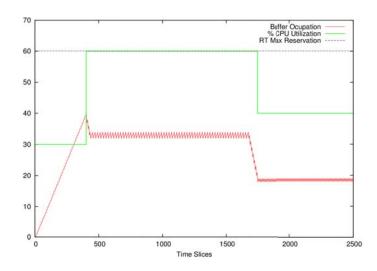

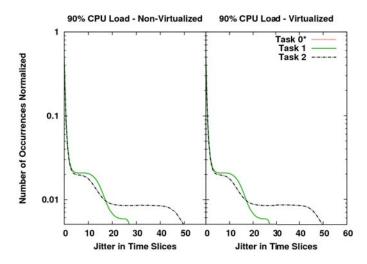

To ease configuration, it uses XML-based system and changes made in this configuration scheme do not require rebuilding the guest operating systems or the user applications. As a debug facility, multiple virtual boards can be checked by a physical Ethernet connection. Regarding core scheduling, it provides a priority-based scheduler and custom schedulers can be used too.