Bruno Naspolini Green

# Hardware-Based Approach to Support Mixed-Critical Workload Execution in Multicore Processors

Porto Alegre - RS, Brasil

2015

Bruno Naspolini Green

## Hardware-Based Approach to Support Mixed-Critical Workload Execution in Multicore Processors

Dissertação de mestrado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica da Pontifícia Universidade Católica do Rio Grande do Sul, como parte dos requisitos para a obtenção do título de Mestre em Engenharia Elétrica. Área de concentração: Sinais, Sistemas e Tecnologia da Informação Linha de Pesquisa: Sistemas de Computação.

Pontifícia Universidade Católica do Rio Grande do Sul – PUCRS

Faculdade de Engenharia

Programa de Pós-Graduação em Engenharia Elétrica

Advisor: Fabian Luis Vargas Co-Advisor: Aurélio Tergolina Salton

> Porto Alegre - RS, Brasil 2015

### HARDWARE-BASED APPROACH TO SUPPORT MIXED-CRITICAL WORKLOAD EXECUTION IN MULTICORE PROCESSORS

### CANDIDATO: BRUNO NASPOLINI GREEN

Esta Dissertação de Mestrado foi julgada para obtenção do título de MESTRE EM ENGENHARIA ELÉTRICA e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia Elétrica da Pontifícia Universidade Católica do Rio Grande do Sul

DR. FABIAN LUIS VARGAS - ORIENTADOR

DR. AURELIO TERGOLINA SALTON - CO-ORIENTADOR

**BANCA EXAMINADORA**

unande quesus de fue.

DRA. FERNANDA GUSMÃO DE LIMA KASTENSMIDT - DO PROGRAMA DE PÓS GRADUAÇÃO EM MICROELETRÔNICA - PGMICRO - UFRGS

Baulises

DRA. LETÍCIA MARIA BOLZANI POEHLS - DO PPGEE - FENG - PUCRS

Campus Central Av. Ipiranga, 6681 - Prédio 30 - Sala 103 - CEP: 90619-900 Telefone: (51) 3320.3540 - Fax: (51) 3320.3625 E-mail: engenharia.pg.eletrica@pucrs.br

# Agradecimentos

Inicialmente gostaria de agradecer ao meu orientador, Dr. Fabian Luis Vargas, e ao meu coorientador, Dr. Aurélio Tergolina Salton, pelos ensinamentos e pelo suporte dados durante todo o processo de desenvolvimento desta dissertação. Seus aconselhamentos foram vitais para a realização deste trabalho.

Aos colegas do laboratório EASE pela parceria nas atividades realizadas no mesmo ao longo do mestrado. E aos professores que contribuíram para a minha formação acadêmica.

À Pontifícia Universidade Católica do Rio Grande do Sul pela oportunidade a mim ofertada desde a minha graduação na mesma, onde desde então venho me aprimorando e aprofundando em meu âmbito de estudo na sua ampla e moderna estrutura física disponibilizada a nós estudantes.

À CAPES e à Hewlett-Packard Brasil Ltda. pelas bolsas de estudos a mim proporcionadas para esta oportunidade de aprendizado.

Ao meu amigo Brandon Arp pelos conhecimentos essenciais compartilhados que possibilitaram o desenvolvimento desta dissertação.

E finalizo agradecendo a meus pais e demais familiares pelo apoio incondicional dado a mim todo este tempo no desenvolvimento de meus conhecimentos e habilidades. Muito obrigado a todos!

## Resumo

O uso de processadores *multicore* em sistemas embarcados em tempo real de propósito geral tem experimentado um enorme aumento nos últimos anos. Infelizmente, aplicações críticas não se beneficiam deste tipo de processadores como se poderia esperar. O principal obstáculo é que não podemos prever e fornecer qualquer garantia sobre as propriedades em tempo real do software em execução nessas plataformas. O barramento de memória compartilhada está entre os recursos mais críticos, que degrada severamente a previsibilidade temporal do software *multicore* devido à contenção de acesso entre os núcleos. Para combater este problema, apresentamos neste trabalho uma nova abordagem que suporta a execução de carga de trabalho de criticidade mista em um sistema embarcado baseado em processadores multicore. Permitindo que qualquer número de núcleos execute tarefas menos críticas concorrentemente com o núcleo crítico que executa a tarefa crítica. A abordagem baseia-se na utilização de um Hard Deadline Enforcer (HDE) implementado em hardware, que permite a execução de qualquer número de núcleos (executando cargas de trabalho menos críticas) simultaneamente com o núcleo crítico (executando a carga crítica). A partir do melhor de nosso conhecimento, em comparação com as técnicas existentes, a abordagem proposta permite a exploração do desempenho máximo oferecido por um sistema *multicore*, garantindo a escalonabilidade da tarefa crítica. Além disso, a abordagem proposta apresenta a mesma complexidade de projeto, como qualquer outra abordagem dedicada a análise temporal para processadores de núcleo único, não importando o número de núcleos que são utilizados no sistema incorporado ao design. Caso técnicas atuais fossem utilizadas, a complexidade do projeto para análise temporal de sistemas de múltiplos núcleos aumentaria dramaticamente conforme o aumento do número de núcleos do sistema embarcado. Foi implementado um estudo de caso baseado em uma versão dual-core do processador LEON3 para demonstrar a aplicabilidade e assertividade da abordagem. Vários códigos de aplicações críticas foram compilados para este processador, que foi mapeado na FPGA Spartan 3E da Xilinx. Resultados experimentais demonstram que a abordagem proposta é muito eficaz na obtenção da alta performance do sistema respeitando o deadline da tarefa crítica.

**Palavras-chaves**: Processadores *Multi-core*, Aplicação Crítica, Sistema Embarcado de Alto Desempenho, Escalonamento de Tarefas Críticas, *Hard Deadline Enforcer* (HDE).

## Abstract

The use of multicore processors in general-purpose real-time embedded systems has experienced a huge increase in the recent years. Unfortunately, critical applications are not benefiting from this type of processors as one could expect. The major obstacle is that we may not predict and provide any guarantee on real-time properties of software running on such platforms. The shared memory bus is among the most critical resources, which severely degrades the timing predictability of multicore software due to the access contention between cores. To counteract this problem, we present in this work a new approach that supports mixed-criticality workload execution in a multicore processor-based embedded system. It allows any number of cores to run less-critical tasks concurrently with the critical core, which is running the critical task. The approach is based on the use of a dedicated Hard Deadline Enforcer (HDE) implemented in hardware, which allows the execution of any number of cores (running less-critical workloads) concurrently with the critical core (executing the critical workload). From the best of our knowledge, compared to existing techniques, the proposed approach allows the exploitation of the maximum performance offered by a multiprocessing system while guaranteeing critical task schedulability. Additionally, the proposed approach presents the same design complexity as any other approach devoted to perform timing analysis for single core processor, no matter the number of cores are used in the embedded system on the design. If current techniques were used, the design complexity to perform timing analysis would increase dramatically as long as the number of cores in the embedded system increases. A case-study based on a dual-core version of the LEON3 processor was implemented to demonstrate the applicability and assertiveness of the approach. Several critical application codes were compiled to this processor, which was mapped into a Xilinx Spartan 3E FPGA. Experimental results demonstrate that the proposed approach is very effective on combining system high-performance with critical task schedulability within timing deadline.

**Key-words**: Multicore Processor, Critical Application, High-Performance Embedded System, Critical Task Schedulability, Hard Deadline Enforcer (HDE).

# List of Figures

| Figure 1 $-$ | Basic notions concerning timing analysis of systems                                    | 26 |

|--------------|----------------------------------------------------------------------------------------|----|

| Figure 2 –   | Core components of a timing-analysis tool                                              | 27 |

| Figure 3 –   | Methods for calculating the upper bound of a task. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 28 |

| Figure 4 –   | IPET results for the ILP in Figure 3c.                                                 | 29 |

| Figure 5 –   | RapiTime block diagram.                                                                | 32 |

| Figure 6 –   | LEON3 processor core block diagram                                                     | 35 |

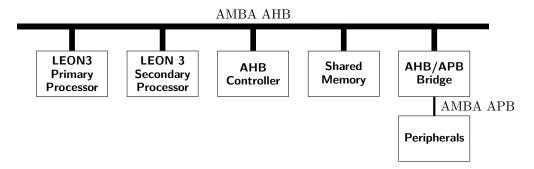

| Figure 7 –   | Dual-Core LEON3 processor block diagram.                                               | 38 |

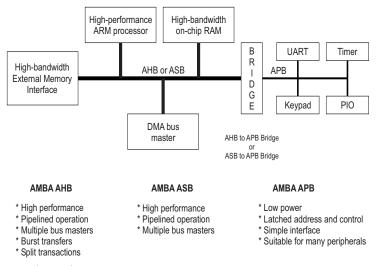

| Figure 8 –   | A typical AMBA system                                                                  | 39 |

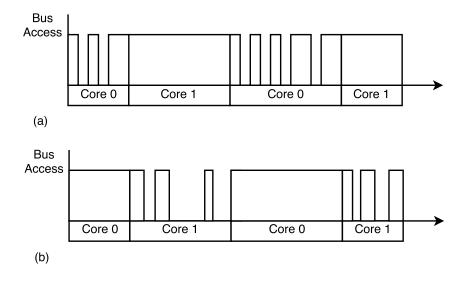

| Figure 9 –   | TDMA bus utilization example                                                           | 42 |

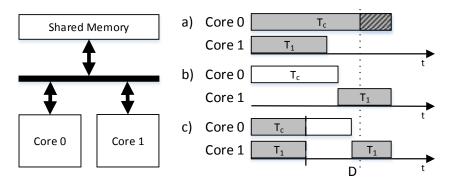

| Figure 10 –  | Scheduling based on WCET when are considered for execution (a) both                    |    |

|              | tasks, (b) only the critical task and (c) proposed approach                            | 42 |

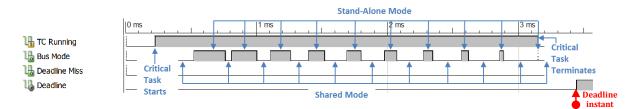

| Figure 11 –  | Timeline of a critical task execution.                                                 | 44 |

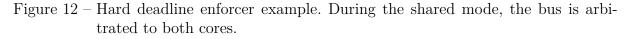

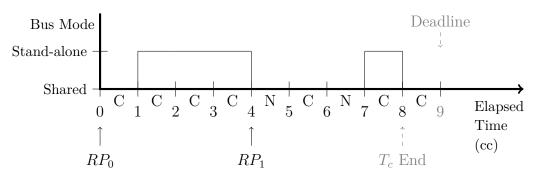

| Figure 12 –  | Hard deadline enforcer example. During the shared mode, the bus is                     |    |

|              | arbitrated to both cores                                                               | 45 |

| Figure 13 –  | Hard deadline enforcer example. During the shared mode, the bus is                     |    |

|              | arbitrated only to the non critical core                                               | 45 |

| Figure 14 –  | WCET tool block diagram.                                                               | 46 |

| Figure 15 –  | Measurement procedure of the latency of instructions passing through                   |    |

|              | the LEON3 micropipeline architecture.                                                  | 47 |

| Figure 16 –  | Single-core LEON3 processor block diagram used to sample instruction                   |    |

|              | times                                                                                  | 48 |

| Figure 17 –  | Timing compilation procedure example.                                                  | 49 |

| Figure 18 –  | Basic block annotation algorithm                                                       | 50 |

| Figure 19 –  | Timing annotation example                                                              | 51 |

| Figure 20 –  | Task CFG example                                                                       | 52 |

| Figure 21 –  | IPET example.                                                                          | 53 |

| Figure 22 –  | IPET $WCET_R$ example with a single loop                                               | 53 |

| Figure 23 –  | IPET $WCET_R$ example with a nested loop                                               | 55 |

| Figure 24 –  | Vertex max CPU cycles example                                                          | 56 |

| Figure 25 –  | Graph Traversal example.                                                               | 57 |

| Figure 26 –  | GTT example with a loop                                                                | 59 |

| Figure 27 –  | GTT example with a nested loop                                                         | 60 |

| Figure 28 –  | ComputeVertexCycles algorithm.                                                         | 61 |

| Figure 29 –  | MemoizedComputeVertexCycles algorithm.                                                 | 62 |

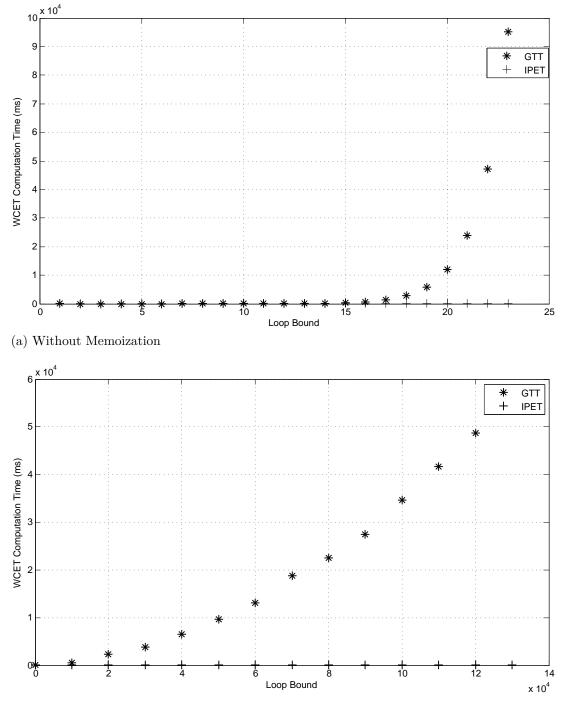

| Figure 30 –  | WCET computation time comparison.                                                      | 63 |

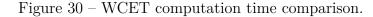

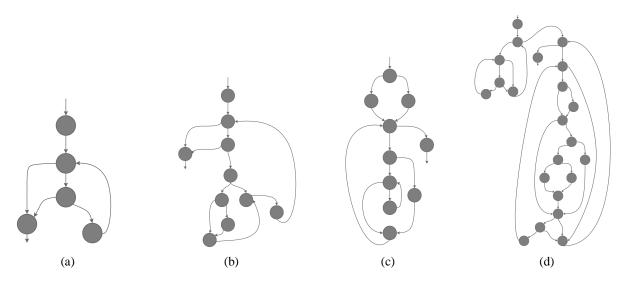

| Figure 31 –  | CFG Structures known to cause failures in the implemented GTT tool.                    | 64 |

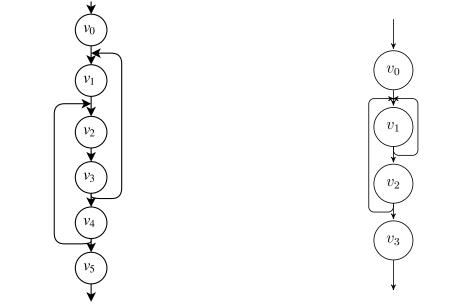

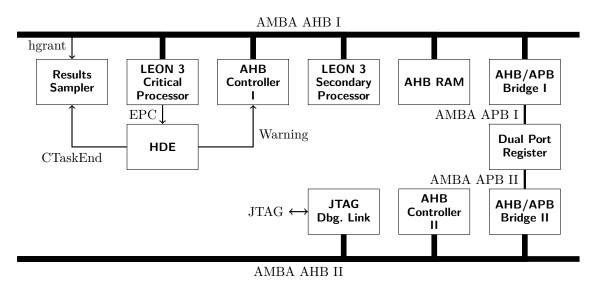

| Figure 32 –   | Block diagram of the interconnection of the LEON3 processor with the HDE             |

|---------------|--------------------------------------------------------------------------------------|

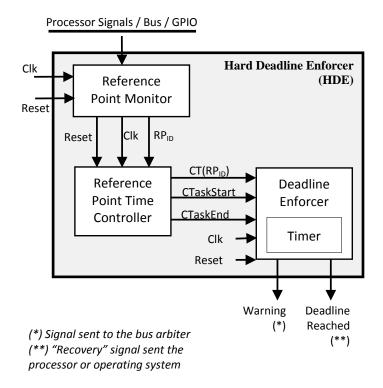

| Figure 33 –   | General view of the HDE internal blocks and their respective signals 66              |

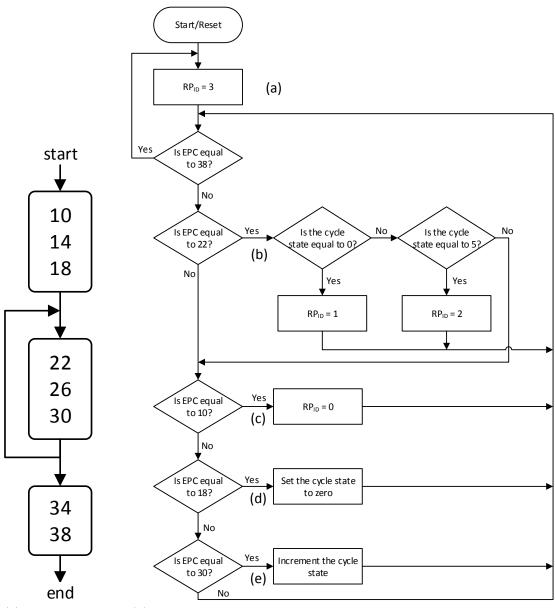

|               | Reference point monitor example                                                      |

| 0             | Flowchart of the HDE operation                                                       |

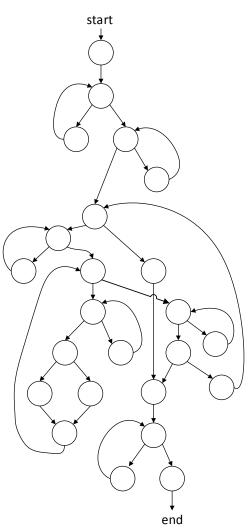

| 0             | Control-flow graphs (CFGs) of the application codes used to validate                 |

| 0             | the proposed approach: (a) Fibonacci Number Computation, (b) Bub-                    |

|               | ble Sort, (c) Dummy Application and (d) Heap                                         |

| Figure 37 –   | Timeline of a system run in the ISim HDL simulator showing the fol-                  |

|               | lowing parameters: (a) critical task (TC) running; (b) Bus mode op-                  |

|               | eration between "shared" and "stand-alone" modes; (c) HDE's output                   |

|               | (Deadline Miss) and (d) Deadline instant                                             |

| Figure 38 –   | Hildreth's quadratic programing procedure                                            |

| Figure 39 –   | Simplified MPC task CFG                                                              |

| Figure 40 –   | System used for the validation and evaluation of the HDE comprised                   |

|               | of a dual-core LEON3 processor                                                       |

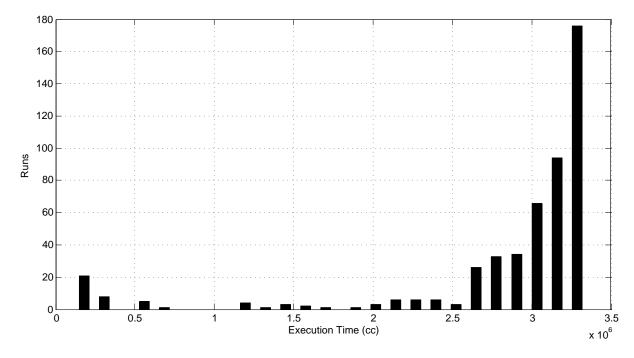

| Figure 41 –   | MPC task measured execution times                                                    |

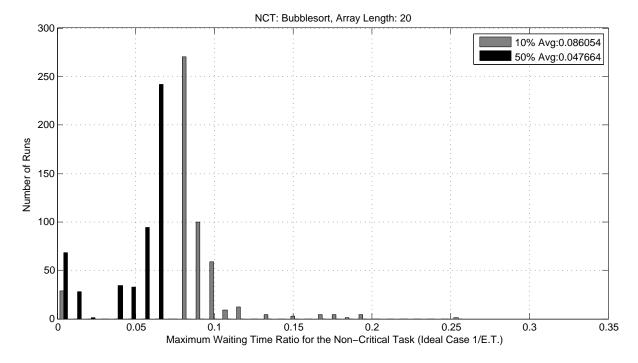

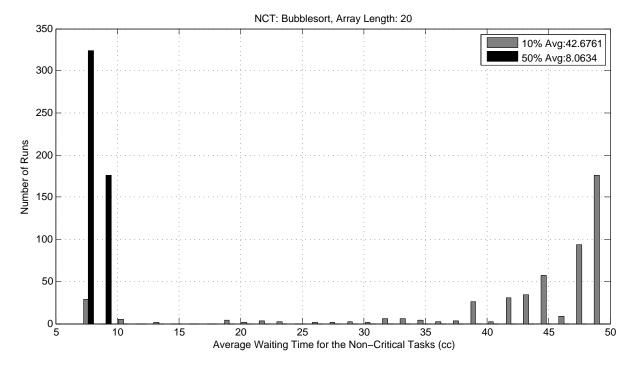

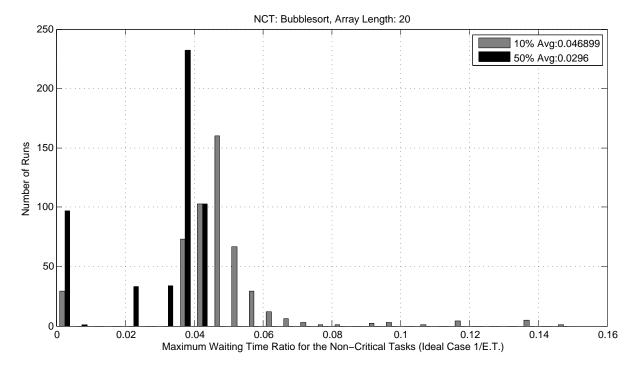

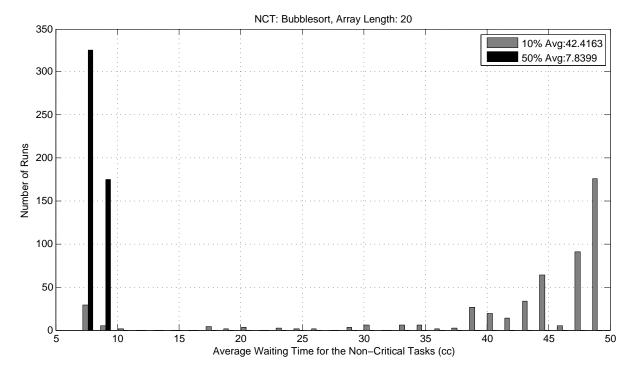

| Figure 42 –   | Maximum waiting times ratio of the non-critical task with an HDE of                  |

|               | 15 RPs                                                                               |

| Figure 43 $-$ | Average waiting times of the non-critical task with an HDE of 15 RPs. $ 82$          |

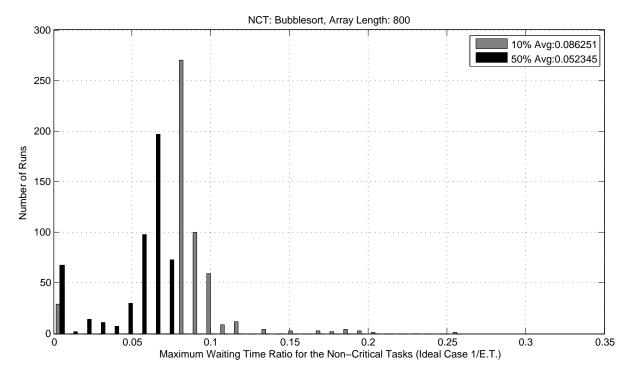

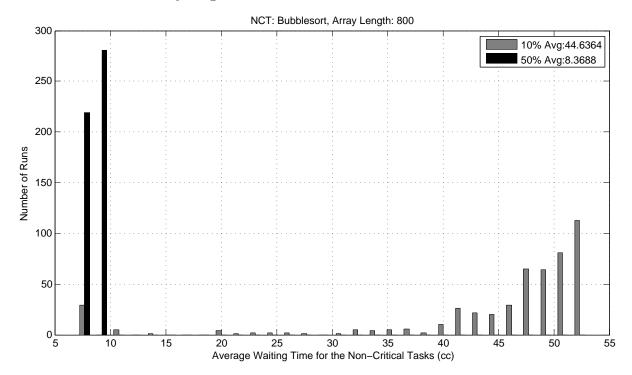

| Figure 44 –   | Maximum waiting times ratio of the non-critical task with an HDE of                  |

|               | 15 RPs, Bubblesort array length: $80083$                                             |

| Figure 45 –   | Average waiting times of the non-critical task with an HDE of 15 RPs,                |

|               | Bubblesort array length: 800                                                         |

| Figure 46 –   | Maximum waiting times ratio of the non-critical task with an HDE of                  |

|               | 28 RPs                                                                               |

| Figure 47 –   | Average waiting times of the non-critical task with an HDE of 28 RPs. 84             |

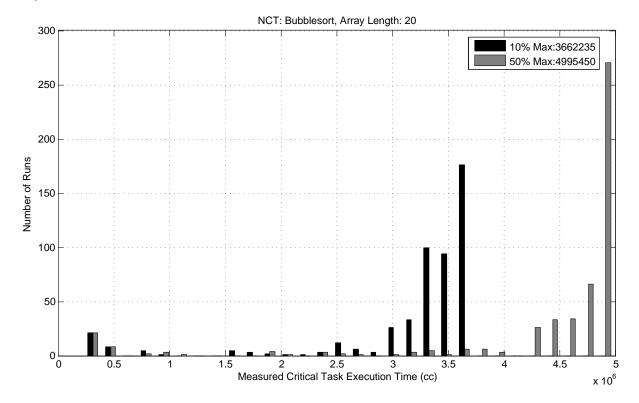

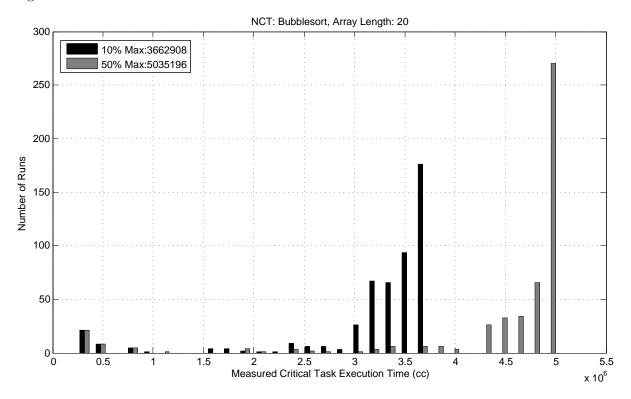

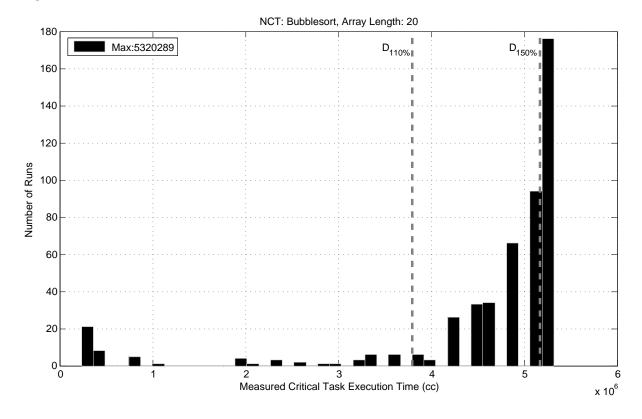

| 0             | Measured execution time of the critical task with an HDE of 15 RPs $85$              |

| 0             | Measured execution time of the critical task with an HDE of 28 RPs $85$              |

| -             | Measured execution time of the critical task without the HDE 86                      |

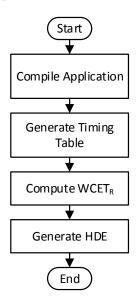

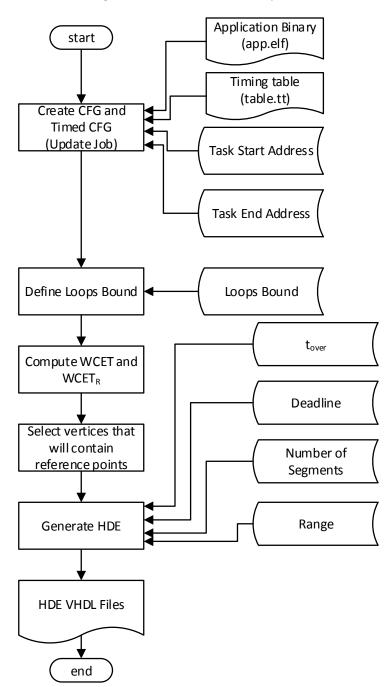

| 0             | Flowchart of a design process                                                        |

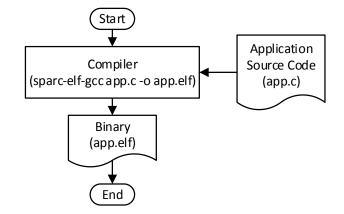

| -             | Flowchart of the steps involved in the compilation of the application 105            |

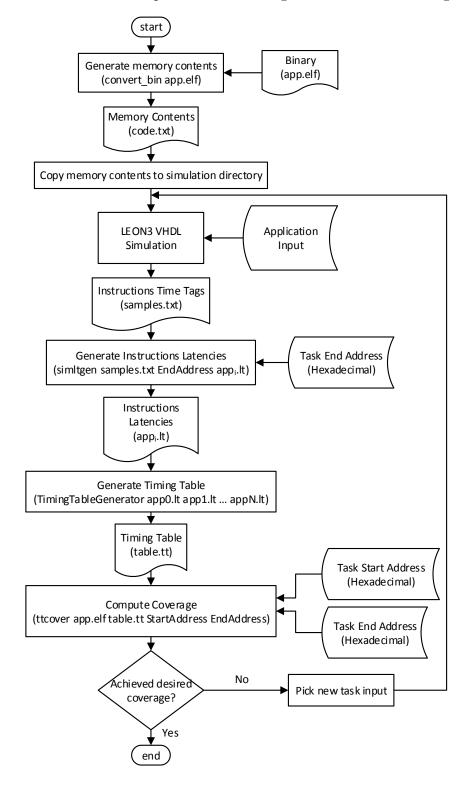

|               | Flowchart of the steps involved in the generation of the Timing Table. 106           |

| Figure 54 –   | Flowchart of the steps involved in the computation of the WCET and                   |

| -             | $WCET_R$ and the generation of the HDE by GTT                                        |

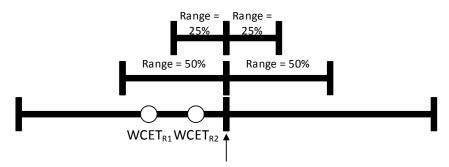

| Figure 55 –   | Example of selection of reference points with 2 segments and ranges of               |

|               | 25% and $50%$                                                                        |

| Figure 56 –   | Flowchart of the steps involved in the computation of the WCET and $WCET$ and $WCET$ |

|               | $WCET_R$ and the generation of the HDE by IPET                                       |

# List of Tables

| Table 1 – HDE example reference points.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . <th>44</th> | 44 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2 – GTT and IPET comparison.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .                                          | 61 |

| Table 3 – Reference points of the Reference Point Monitor example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 67 |

| Table 4 $-$ HDE area overhead for the evaluated applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73 |

| Table 5 – HDE area overhead by varying the number of loops. $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73 |

| Table 6 – Number of primitives by varying the number of loops.       .       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 73 |

| Table 7 – HDE area overhead by varying the number of reference points per loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74 |

| Table 8 – Number of primitives by varying the number of reference points per loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 74 |

| Table 9 – HDE area overhead by varying the number of reference points (for loop-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| less codes). RP added at every instruction in the code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 75 |

| Table 10 – Number of primitives by varying the number of reference points (for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| loopless codes). RP added at every instruction in the code. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75 |

| Table 11 – HDE area overhead by varying the number of reference points (for loop-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| less codes). RP added at every bunch of 100 instructions. $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75 |

| Table 12 – Number of primitives by varying the number of reference points (for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| loopless codes). RP added at every bunch of 100 instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 75 |

| Table 13 – DC motor parameters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77 |

| Table 14 – Area overhead of the HDE configured for the MPC task.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 86 |

| Table 15 – Number of primitives used in the design.    .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 86 |

| Table 16 – Comparison between TDMA and the HDE.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .        .       <            | 87 |

# List of abbreviations and acronyms

- AHB Advanced high-performance bus

- AMBA Advanced Microcontroller Bus Architecture

- APB Advanced peripheral bus

- BCET Best-case execution time

- CFA Control-flow analysis

- CFG Control-flow graph

- CT Critical time

- CPU Central processing unit

- DSU Debug support unit

- EPC Executed program counter

- FPGA Field Programmable Gate Array

- FCFS First-come, first-served

- GTT Graph traversal technique

- HDE Hard Deadline Enforcer

- IPET Implicit-path enumeration technique

- ILP Integer linear programming

- IF Instruction fetch

- JTAG Joint Test Action Group

- LFSR Linear-feedback shift register

- MPC Model predictive control

- RP Reference point

- $RP_{ID}$  Reference point time identification

- RAM Random-access memory

| SMP      | Symmetric multiprocessing           |

|----------|-------------------------------------|

| TDMA     | Time division multiple access       |

| ТА       | Timed automaton                     |

| VHSIC    | Very High Speed Integrated Circuit  |

| VHDL     | VHSIC Hardware Description Language |

| WCET     | Worst-case execution time           |

| $WCET_R$ | Remaining worst-case execution time |

# List of symbols

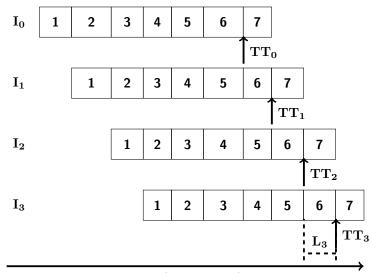

| $I_i$                 | Instruction $i$                                                |

|-----------------------|----------------------------------------------------------------|

| $A_i$                 | Address of instruction $i$                                     |

| $TT_i$                | Time tag of instruction $i$                                    |

| $L_i$                 | Latency of instruction $i$                                     |

| $a \leftarrow b$      | Assignment of $b$ to the identifier $a$                        |

| $v_i$                 | Vertex $i$                                                     |

| $e_i$                 | Edge $i$                                                       |

| $x_{v_i}$             | Count variable of vertex $i$                                   |

| $x_{e_i}$             | Count variable of edge $i$                                     |

| $t_{v_i}$             | Time coefficient of vertex $i$                                 |

| $p_{e_i}$             | Penalty coefficient of edge $i$                                |

| $e_{a \rightarrow b}$ | Directed edge pointing from vertex $a(v_a)$ to vertex $b(v_b)$ |

| $LB_{a \to b}$        | Loop Bound of the cycle with back-edge $e_{a \rightarrow b}$   |

| $x_{a \to b}$         | Count variable of edge $e_{a \to b}$                           |

| $a \setminus b$       | Relative complement of set $b$ in set $a$                      |

| $T_{v_i}$             | Maximum estimated CPU clock cycles of vertex $\boldsymbol{i}$  |

| $S_{e_{t \to h}}$     | State of the cycle with back-edge $e_{t \rightarrow h}$        |

| $C_{e_{t \to h}}$     | Constraint of the cycle with back-edge $e_{t \rightarrow h}$   |

| Z                     | Integer numbers set                                            |

| $T_s$                 | Sampling period                                                |

| $i_a$                 | Armature current                                               |

| $R_a$                 | Armature resistance                                            |

| $L_a$                 | Armature inductance                                            |

| J                | System inertia                                                  |

|------------------|-----------------------------------------------------------------|

| b                | Viscous friction coefficient                                    |

| $k_t$            | Torque constant                                                 |

| $k_{\omega}$     | Speed constant                                                  |

| $I_f$            | Field current                                                   |

| w                | Angular speed                                                   |

| $A^T$            | Transpose of the $A$ matrix                                     |

| x                | Euclidean norm of the x vector, that is, $  x   = \sqrt{x^T x}$ |

| A                | Cardinality of set $A$ .                                        |

| $0_{n \times 1}$ | Vector of zeros composed by $n$ lines                           |

# Contents

| 1       |                                                               | 21 |

|---------|---------------------------------------------------------------|----|

| 1.1     | Objectives                                                    | 22 |

| 2       | PRELIMINARIES                                                 | 25 |

| 2.1     | Real-Time Systems                                             | 25 |

| 2.2     | Timing Analysis                                               | 25 |

| 2.2.1   | Static Timing Analysis                                        | 26 |

| 2.2.2   | Measurement-based Methods                                     | 29 |

| 2.2.3   | Timing Analysis Tools                                         | 30 |

| 2.2.3.1 | AbsInt's WCET Analyzer aiT                                    | 30 |

| 2.2.3.2 | Bound-T Tool                                                  | 30 |

| 2.2.3.3 | RapiTime Tool                                                 | 31 |

| 2.3     | State-of-the-Art on Timing Analysis Techniques for MPSoC      | 32 |

| 2.4     | LEON3 Processor                                               | 35 |

| 2.4.1   | Instruction Pipeline                                          | 35 |

| 2.4.2   | Debug Support Unit (DSU)                                      | 36 |

| 2.4.3   | AMBA interface                                                | 36 |

| 2.4.4   | Cache System                                                  | 37 |

| 2.4.5   | Multi-Processor Support                                       | 37 |

| 2.4.6   | Register Windows                                              | 37 |

| 2.5     | Advanced Microcontroller Bus Architecture (AMBA)              | 38 |

| 2.5.1   | ΑΜΒΑ ΑΗΒ                                                      | 38 |

| 3       | PROPOSED METHODOLOGY                                          | 41 |

| 3.1     | Problem Description                                           | 41 |

| 3.2     | Proposed Solution                                             | 41 |

| 3.3     | WCET Computation Technique: a case-study on the LEON3 single- |    |

|         | core processor                                                | 45 |

| 3.3.1   | Program Execution on Target HW                                | 46 |

| 3.3.2   | Timing Compilation Procedure                                  | 48 |

| 3.3.3   | Timing Annotation                                             | 49 |

| 3.3.4   | $WCET_R$ Computation                                          | 51 |

| 3.3.4.1 | Implicit Path Enumeration Technique (IPET)                    | 51 |

| 3.3.4.2 | Graph Traversal Technique (GTT)                               | 56 |

| 3.3.4.3 | WCET Computation Technique Comparison                         | 58 |

| 3.3.4.4 | Limitations of the GTT and IPET tools                         | 62 |

| 3.4   | Hard Deadline Enforcer Development (HDE): a case-study on the                                 |  |  |  |

|-------|-----------------------------------------------------------------------------------------------|--|--|--|

|       | LEON3 dual-core processor                                                                     |  |  |  |

| 3.4.1 | HDE Interconnection with MPSoC                                                                |  |  |  |

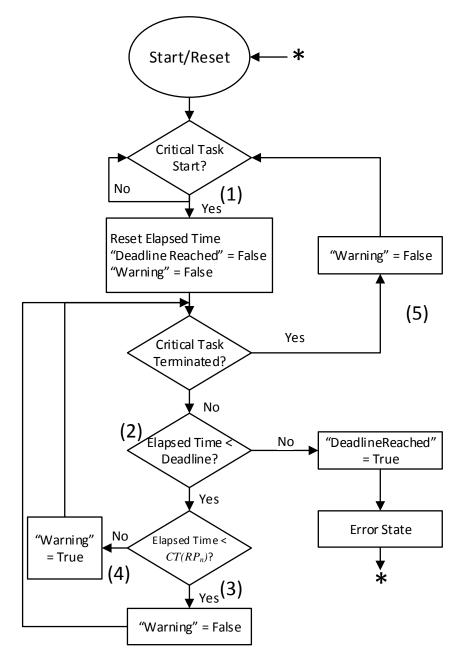

| 3.4.2 | HDE Architecture                                                                              |  |  |  |

| 3.4.3 | Limitations in the Insertion of Reference Points                                              |  |  |  |

| 4     | VALIDATION & EVALUATION                                                                       |  |  |  |

| 4.1   | Preliminary Results                                                                           |  |  |  |

| 4.2   | Complex Real-Time Control Application                                                         |  |  |  |

| 5     | CONCLUSION                                                                                    |  |  |  |

| 6     | FUTURE WORK                                                                                   |  |  |  |

|       | BIBLIOGRAPHY 93                                                                               |  |  |  |

|       | APPENDIX A – GRAPH SEARCH ALGORITHM                                                           |  |  |  |

|       | APPENDIX B – MODIFICATION IN THE LEON3 TO GENER-<br>ATE THE EXECUTED PROGRAM COUNTER<br>(EPC) |  |  |  |

|       | APPENDIX C – AMBA BUS CONTROLLER: SUPPORT FOR STAND-<br>ALONE BUS MODE                        |  |  |  |

|       | APPENDIX D – STEP BY STEP OF A DESIGN PROCESS 105                                             |  |  |  |

## 1 Introduction

It is of common agreement among designers and users that multicore processors will be increasingly used in future embedded real-time systems for critical applications where, in addition to reliability, high-performance is at a premium. The major obstacle is that we may not predict and provide any guarantee on real-time properties of software on such platforms. As consequence, the timing deadline of critical real-time tasks may be violated. In this context, the shared memory bus is among the most critical resources, which severely degrade the timing predictability of multicore workloads due to access contention among cores. In critical embedded systems (e.g., aeronautical systems), this uncertainty of the non-uniform and concurrent memory accesses prohibits the full utilization of the system performance. In more detail, the system is designed in such a way that the processor runs in the stand-alone mode when a critical task has to be executed, i.e., the bus controller allows only one core to run the critical workload, and inhibits the other cores to execute less-critical workloads till the completion of the critical task. In order to counteract this problem and properly balance reliability against performance as long as possible, we present in this work a new approach that supports mixed-criticality workload execution by fully exploiting processor parallelism. It allows any number of cores to run less-critical tasks concurrently with the critical core, which is running the critical task. The proposed approach is not based on any multicore static timing analysis or any timing model of multicore processor parts such as pipeline, cache memory and interactions of these parts with shared memory bus. Instead, the approach is based on the use of a dedicated Hard Deadline Enforcer (HDE), which works as follows: when a critical task starts running, the HDE allows the execution of any number of cores (running less-critical workloads) concurrently with the critical core (executing the critical workload) till the moment when the HDE predicts that the critical workload deadline will be violated if the processor continues running all cores concurrently. At this moment, the HDE inhibits the noncritical cores to execute less-critical tasks until the completion of the critical task by the critical core. Then, it is said that the system is switched from the "shared mode" (where two or more cores are fighting for shared memory bus access) to the "stand-alone mode", where a single (the critical) core is running. Given the above, the proposed approach presents the following features and advantages compared to the existing techniques:

a) It minimizes the computational complexity imposed by multicore static timing analysis: it needs only to analyze interactions between pipeline and cache models of a single core when executing a given critical task. All inter-core conflicts generated during the execution of the critical and the various less-critical tasks caused by their non-uniform and concurrent memory bus accesses are not taken into account by the HDE.

- b) From the above (a) statement, it is also concluded that the proposed approach does not need the development and it is not based on timing analysis models of multicore processors. Therefore, the approach is not based on the faithfulness of the multicore processor model to guarantee a precise workload timing prediction.

- c) In contrast to the existing approaches, the proposed approach does not require any knowledge about the implementation of the less-critical workloads or even the number of workloads that will run concurrently with the critical task. The HDE is configured according to specific code structure and timing characteristics of the critical task. Then, the HDE monitors online the critical task execution and automatically switches the bus usage from the "shared" mode to the "stand-alone" mode to guarantee the maximum possible processor performance with workload schedulability. Note that if the number of less-critical task to guarantee workload schedulability. This condition is ensured because the HDE can switch from the "shared mode" to the "stand-alone mode" automatically, no matters is the number of less-critical tasks are running in parallel with the critical one.

- d) The approach can be applied to any type of processor, considered that the designer is able to collect two signals from the processor ("Program Counter" and "Annul"). The latter signal indicates if the current instruction in the pipeline was actually executed or not.

- e) Given that the approach can be applied to any type of processor, it allows a large spectrum of real-time operating systems to be used. Thus, traditional and wellstablished real-time operating systems for critical applications such as VxWorks, LynxOS, Integrity or RTEMS and their advanced versions compliant with ARINC-653 (an avionics standard for safe, partitioned systems) (ARINC Specification 653, 2006a; ARINC Specification 653, 2007; ARINC Specification 653, 2006b) could also be considered in the whole system design.

- f) The proposed approach does not requires recompilation of the critical task in order to guarantee its timing deadline.

## 1.1 Objectives

The objectives of this work are as follows:

- The primary goal is the development of a hardware-based approach, namely "Hard Deadline Enforcer (HDE)" to guarantee the timing deadline of a single critical task running concurrently with one or more non-critical tasks in a multicore processor.

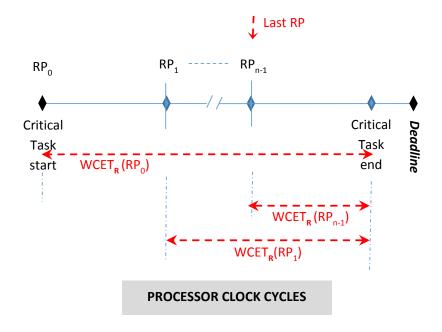

- The secondary goal is the automation of the determination process of the remaining worst-case execution time  $(WCET_R)$  parameter of reference points distributed strategically within the critical task. This automation by adopting an existing and well established technique found in the literature (IPET) to automate the determination of the  $WCET_R$  parameter by one side. by the other side, it was developed a new technique to determine this parameter, named GTT. Both techniques presents advantages and drawbacks and can, thus, be used complementary to each other.

## 2 Preliminaries

### 2.1 Real-Time Systems

Real-time systems are computing systems that must react in strict timing constraints. Therefore the correct system behavior not only depends in the correctness of the output but also depends in the moment in which the output was produced. A real-time task is a task that posses a timing constraint known as deadline. The deadline is the maximum time in which the system must produce the output. A real-time task is classified by the consequences caused by a missed deadline (BUTTAZZO, 2011) as follows:

- Hard: A hard real-time task has catastrophic results when a deadline is missed.

- Firm: The result of a firm real-time task loses its purpose after the deadline, but does not cause any damage.

- **Soft**: In a soft real-time task, the results produced after the deadline has some utility, but causing a performance degradation.

## 2.2 Timing Analysis

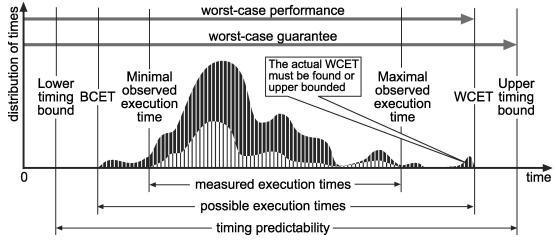

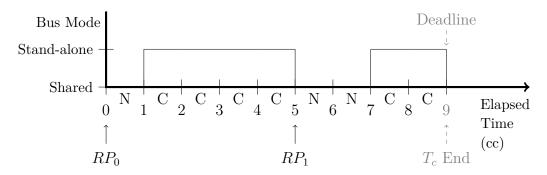

The timing of real-time tasks running in a real-time systems must analyzed to verify the deadline constraints of the tasks. If the constraints cannot be met in the evaluated system, the tasks can be optimized or the system must be replaced with a more powerful system in order to satisfy the constraints. Figure 1 illustrates basic notions concerning the timing analysis of systems. The execution time of a task varies depending on the input data or different behavior of the environment (WILHELM et al., 2008). The upper curve shows the distribution of execution times of the task, and the bottom curve is the distribution of measured times for a given set of inputs and environment behaviors.

A task typically shows a certain variation of execution times depending on the input data or different behavior of the environment. The longest response time is called the worst-case execution time (WCET). In most cases, the state space is too large to exhaustively explore all possible executions and thereby determine the exact WCET. Timing analysis tools tries to determine a timing upper bound that is higher than the WCET but as close to it as possible.

In most parts of industry, the common method to estimate execution time bound is to measure the end-to-end execution time of the task for some set of inputs (test cases) on the target hardware or on a clock cycle-accurate simulator. This determines the maximal

Figure 1 – Basic notions concerning timing analysis of systems.

Reference: Wilhelm et al. (2008).

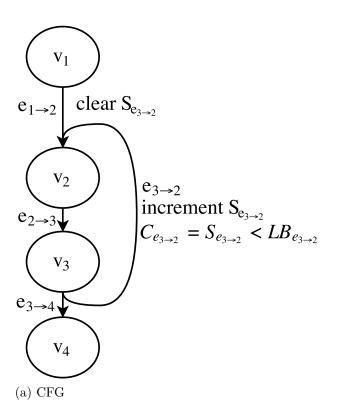

observed execution time. In general, this will underestimate the WCET and so is not safe for hard real-time systems. This method is often called dynamic timing analysis. In contrast to this method, there is the static timing analysis, which is the preferred method used by academia. This method does not rely on executing code on real hardware or on a simulator. Rather, it takes the task code itself, most often together with some annotations, constructs a control-flow graph (CFG) of the workload and analyzes the set of all possible paths through the CFG. Next, this technique combines control-flow analysis with (abstract) models of the processor architecture (e.g., pipeline, cache memory and bus-access policy models) in order to obtain the WCET bound for the workload.

### 2.2.1 Static Timing Analysis

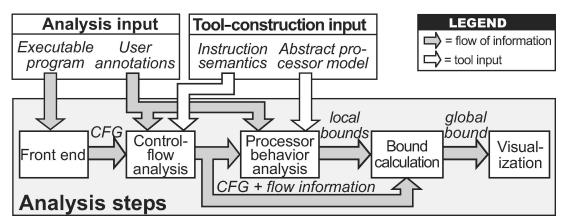

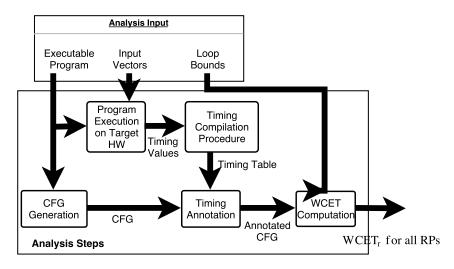

Figure 2 depicts the core components of a timing-analysis tool. The front end is responsible of generating the Control flow graph (CFG) of the application from the provided executed application. To do so, the instructions are decoded from the executed application based in the instruction set of the target architecture. The vertices in the CFG are known as basic blocks, which contains contiguous instructions. Branches are represented by edges in the CFG.

Value analysis can be used to determine the loops bounds, alternatively these can be provided by the user. Control-flow analysis (CFA) gathers information about possible execution paths in the application. That allows to potentially yield tighter bounds, by removing unfeasible paths in the bound calculation step.

The processor-behavior analysis uses abstract models of the processor to gather information on the processor behavior for the task under analysis. It analysis the behavior of components that affects the execution times, such as memory, caches, pipelines and branch prediction. A common method to analyze the cache is by abstract interpretation

Figure 2 – Core components of a timing-analysis tool.

Reference: Wilhelm et al. (2008).

(COUSOT; COUSOT, 1977; ALT et al., 1996; FERDINAND; WILHELM, 1999), memory accesses are classified (e.g. always hit, always miss, first hit).

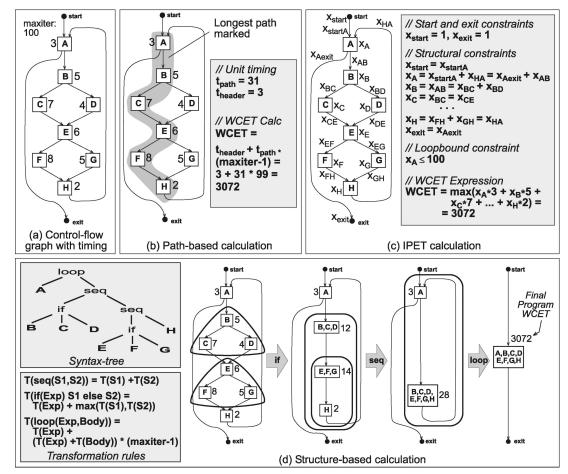

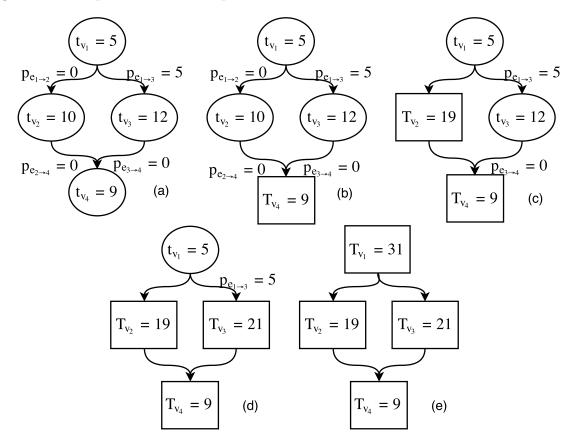

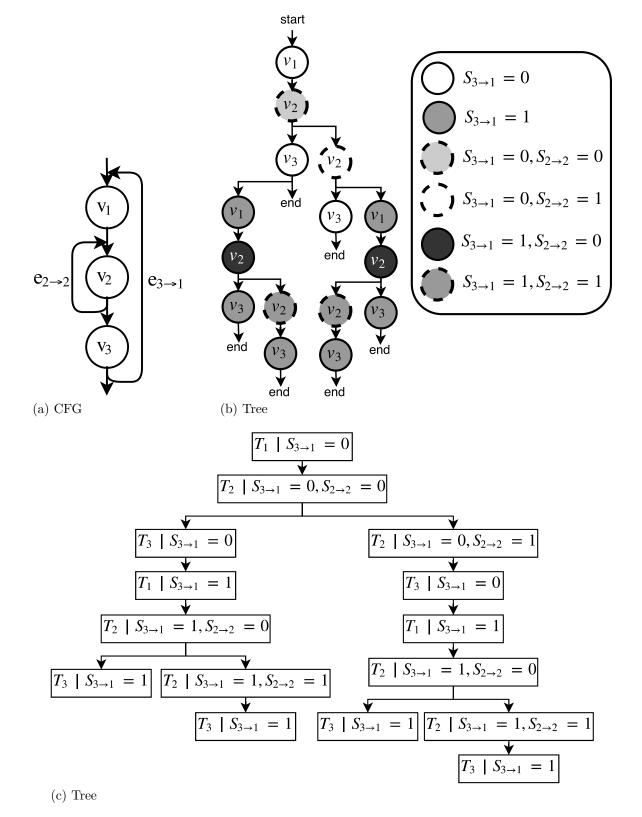

The bound calculation computes and upper bound of all execution times considering all possible paths of the task. It is based on the flow and timing information derived in the previous steps. Analytically determined or measured times can be combined by three main methods in the literature: *structure-based*, *path-based* and *implicit-path enumeration technique* (IPET) (WILHELM et al., 2008).

In the structure-based method, the upper bound is computed in a bottom-up traversal of the syntax tree of the task. It combines the computed task bounds for constituents of statements by following combination rules for the type of the statement.

Figure 3d depicts an example of the upper bound computation for the task in Figure 3a. It first determines the bound for the *if* statement composed by "E, F and G", which is  $T(E) + \max(T(F), T(G)) = 14$ , then it combines this time with the time of H, yielding 16. Then it computes the time of the "B, C, D" if statement, yielding 12, which is then combined with the time of "E, F, G, H", yielding 28. Finally it matches the resulting structure with a loop statement, which time is given by  $T(A) + (T(A) + T(B, C, D, E, F, G, H)) \times (maxIteration - 1) = 3 + (3 + 28) \times 99 = 3072$ , which is the upper bound of the task.

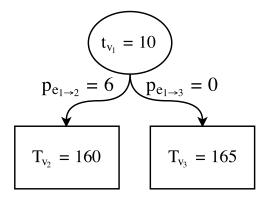

The Implicit Path Enumeration Technique (IPET), first proposed by (LI; MALIK, 1995), is a technique where the bound calculation is performed by formulating and solving an Integer Linear Programming (ILP) constrained optimization problem. In ILP, the objective function and variables are linear and are constrained to Z. Methods for solving ILP problems are detailed in (GARFINKEL; NEMHAUSER, 1972).

In IPET, a time coefficient  $(t_{entity})$  is given for each basic block in the task, which express the upper bound of the contribution of that basic block of every time it is executed. It is also given a count variable  $(x_{entity})$  for every basic block in the task, which counts

Figure 3 – Methods for calculating the upper bound of a task.

Reference: Wilhelm et al. (2008).

how many times that entity was executed. The objective function of the ILP problem is defined to be the sum of the product of the time coefficient and count variable for all basic blocks in the task  $(\sum_{i \in entity} x_i \times t_i)$ .

The structure of the task is described as a set of constraints in the count variables. The sum of the count variables of the edges that enters an entity is equal to the sum of count variables of the edges that leaves the entity, that is also equal to the count variable of the entity in which the edges entered (exited)., i.e.,  $x_B = x_{AB} = x_{BC} + x_{BD}$ . Loops bounds are defined as constraints in the count variable of the loop header, i.e.,  $x_A \leq 100$ .

The *start* and *exit* constraints specifies that the task was entered and exited once. Once the ILP problem is formulated, a tool such as  $lp\_solve$  (BERKELAAR, 2010) can be used to obtain the WCET and the count variable of all basic blocks of the task. Figure 4 depicts the solution for the ILP formulation in Figure 3c computed using the  $lp\_solve$ tool. It shows the WCET (3072) and the count variables of every basic block and edge. From the Figure 4, it can be noticed that the basic blocks *D* and *G*, were not executed, once they would not contribute for the WCET of the task.

| Variables | result | Variables | result |

|-----------|--------|-----------|--------|

|           | 3072   | xha       | 99     |

| xa        | 100    | xab       | 99     |

| xb        | 99     | xbc       | 99     |

| хс        | 99     | xbd       | 0      |

| xd        | 0      | xce       | 99     |

| xe        | 99     | xde       | 0      |

| ×f        | 99     | xef       | 99     |

| xg        | 0      | xeg       | 0      |

| xh        | 99     | xfh       | 99     |

| xstart    | 1      | xgh       | 0      |

| xend      | 1      |           |        |

An extension of IPET is presented in (OTTOSSON; SJODIN, 1997) to allow the independent modeling of micro-architectural aspects, it shows examples for modeling pipelined execution and set-associative caches. Ballabriga e Cassé (2008) decreases the WCET computation time by partitioning the CFG of the task into smaller parts, where a local WCET can be computed faster.

In path-based methods, the upper bound is given by computing bounds for different paths of the task, searching for the path with the longest execution time. The number of paths is exponential to the number of branch points in the task (WILHELM et al., 2008). Figure 3b depicts an example the path-based method, where the longest path is marked and its time is combine with the loop bound to computed the upper bound for the task. A path search method considering pipeline effects, caches and complex flows is described in (STAPPERT; ERMEDAHL; ENGBLOM, 2001).

#### 2.2.2 Measurement-based Methods

These methods works by executing the task or parts of the task with a set of inputs on the target hardware and sampling the time of every instruction or basic block of the task. A clock-cycle accurate simulator can be used instead of executing it in the target hardware. Measurement can be applied to task snippets as well, and then combining the results using methods of static methods, such as in Figure 3. Although, using measurement, safe bounds can only be guaranteed on simple architectures (WILHELM et al., 2008). Using measurement of parts of the tasks (or with instruction granularity), replaces the "processor-behavior analysis" in Figure 2. Then, using CFA to find all possible paths, and combining the measured times on the bound calculation step, all paths of the task is considered in the timing bound estimation. Although, if the measured times are not safe (e.g. due to cache), the estimated timing bound is not safe. Burns e Edgar (2000) predicts the WCET of tasks for complex processor architectures using measurement associated with statistical analysis, where the computation time is represented by a probability function and the WCET estimates have a level of confidence.

Bernat, Colin e Petters (2002), Bernat, Colin e Petters (2003) presents a method based in measurement and static analysis. It combines probabilistically the worst case effects observed in individual blocks collected during measurement into the worst-case path of the application.

### 2.2.3 Timing Analysis Tools

#### 2.2.3.1 AbsInt's WCET Analyzer aiT

aiT is a commercial WCET static analysis tool that provides support for several hardware platforms (Motorola PowerPC MPC 555, 565, and 755, Motorola ColdFire MCF 5307, ARM7 TDMI, HCS12/STAR12, TMS320C33, C166/ST10, Renesas M32C/85 (prototype), Infineon TriCore 1.3, LEON2 and LEON3). aiT first derives safe upper bounds for the execution time of basic blocks and then computes, by integer linear programming, an upper bound on the execution times over all possible paths of the program (FERDI-NAND; HECKMANN, 2004).

At first, aiT reconstructs the CFG from a binary program, then value analysis computes value ranges for register and address ranges for instructions accessing memory. Loop bound analysis determine the loop bounds for simple loops in the application. Cache analysis is performed using abstract interpretation, classifying memory references as cache misses or hits. Cache analysis is based in the results of value analysis to then predict the behavior of the cache. Pipeline analysis is perform and finally the WCET is computed by path analysis using integer linear programming.

The user must provide annotations if the automatic loop bound analysis fails. Furthermore, if some application does not adheres to the standard calling convention, the user might need to provide additional annotations describing the control-flow properties of the task (WILHELM et al., 2008).

#### 2.2.3.2 Bound-T Tool

The Bound-T tool was originally a commercial tool developed at Space Systems Finland Ltd, an was intended for verification of spacecraft on-board software. Tidorum Ltd extended Bound-T to other application domains. Since January 2014, the Bound-T tool is supplied free of charge in an open-source license. Although some modules that relies on proprietary information from third party vendors remains closed source. The Bound-T tool is based in static timing analysis, using implicit path enumeration technique to determine the worst-case path and the upper bound. The architecture is designed to be adaptable to different target processors, extensible with new kinds and methods of analysis, and portable to different host platforms (HOLSTI; SAARINEN, 2002).

The task being analyzed must not be recursive, must use standard calling conventions and function pointers are not supported. No cache analysis is yet implemented, and any timing anomalies in the target processor must be accounted for in the execution time of basic blocks of the CFG (WILHELM et al., 2008). The Bount-T tool supports the following target platforms: Intel-8051 series (MCS-51), Analog Devices ADSP-21020, ATMEL ERC32 (SPARC V7), Renesas H8/300, ARM7 (prototype) and ATMEL AVR and ATmega (prototypes) (WILHELM et al., 2008).

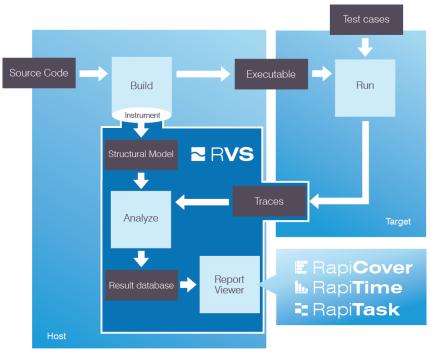

#### 2.2.3.3 RapiTime Tool

RapiTime aims at medium to large real-time embedded systems on advanced processors. The RapiTime tool targets the automotive electronics, avionics and telecommunications industries (WILHELM et al., 2008).

Figure 5 depicts the block diagram of the RapiTime tool. The user provides a set of source codes of that task under analysis, which is then built, from the executable, a structural model is generated. From test cases provided by the user, alongside with the executable, the application is run in the target hardware, generating timing traces. The application must be instrumented with instrumentation points which indicates that a section of the application was executed (RAPITA SYSTEMS LTD, 2015a). Which can be performed either by a software instrumentation library or by a lightweight software instrumentation with external hardware support. Alternatively the timing information can be captured by purely nonintrusive tracing mechanisms (like Nexus and ETM) or even traces from CPU simulators (WILHELM et al., 2008).

The structural model and the traces are used in the analysis step to compute probability distributions from the measured times, producing performance metrics and predicting the worst-case execution time (RAPITA SYSTEMS LTD, 2015a). Results can be observed for each function and subfunction of the analyzed task.

RapiTime does not relies on processor models, therefore it can work for any processor, as long as traces can be collected from the processor, and that the object code reader is ported for that processor. RapiTime cannot analyze programs with recursion and with nonstatically analyzable function pointers (WILHELM et al., 2008). The location of the jump performed by function pointers can only be determined at runtime (in the case that it is nonstatically analyzable), making it difficult to generate the structural model for these applications.

Figure 5 – RapiTime block diagram.

Reference: RAPITA SYSTEMS LTD (2015a).

## 2.3 State-of-the-Art on Timing Analysis Techniques for MPSoC

A lot of research has been carried out within the area of WCET analysis (PUSCHNER; BURNS, 2000). However, each task is, traditionally, analyzed in isolation as if it was running on a monoprocessor system. Consequently, it is assumed that memory accesses over the bus take constant amount of time to process. For multiprocessor systems with a shared communication infrastructure, however, transfer times depend on the bus load and are therefore no longer constant, causing the traditional methods to produce incorrect results (ROSÉN et al., 2011). As response to this specific need, several approaches dealing with WCET prediction in multicore platforms have been proposed (ROSÉN et al., 2011; CHATTOPADHYAY et al., 2014; LV et al., 2010; UNGERER et al., 2010).

In (ROSÉN et al., 2011), authors proposed a technique to achieve predictability of tasks running in multiprocessor systems. The approach is based on the simultaneous analysis of the critical task running in a given core with the shared-bus scheduling process, in order to bound the WCET for that task. In order to calculate the whole WCET of such task, the analysis needs to be aware of the TDMA bus, taking into account that cores must only be granted the bus during their assigned time slots.

In (CHATTOPADHYAY et al., 2014), authors proposed a unified WCET static timing analysis approach for multicore processors. This work is based on models of cache and shared bus, which interact with other basic micro-architectural models (e.g. pipeline and branch predictor unit). Each processor core is analyzed at a time by taking care of the inter-core conflicts generated by all other cores. In this multicore scenario, it is assumed a TDMA shared bus based on round robin arbitration policy, where a fixed length bus slot is assigned to each core. They also assume fully separated caches and buses for instruction and data. Therefore, the data references do not interfere with the instruction references. This work only models the effect of instruction caches. Since it is considered only instruction caches, the cache miss penalty (computed from cache analysis) directly affects the instruction fetch (IF) stage of the pipeline. Finally, authors consider the LRU cache replacement policy.

In (LV et al., 2010), authors proposed a method to bound WCET for workloads running in a multicore architecture where each core has a local L1 cache and all cores use a shared bus to access the off-chip memory. They modeled the local cache behavior of a program running on a dedicated core. Then, based on the cache model, they constructed a Timed Automaton (TA) to model when the programs access the shared bus. Examples for TDMA and FCFS buses were analyzed. The UPPAAL model checker (BENGTSSON et al., 1996) is used to find the WCET of the application.

In contrast to (ROSÉN et al., 2011)(CHATTOPADHYAY et al., 2014)(LV et al., 2010) that are approaches based on static timing analysis, in (UNGERER et al., 2010) authors described a project called "Merasa: Multicore Execution of Hard Real-Time Applications Supporting Analyzability". This work aimed at developing multicore processor design (described in SystemC) for hard real-time embedded systems and a technique to guarantee the analyzability and timing predictability of every feature provided by the processor. Publications presented results for a quad-core version of this processor, where each core consists of two pipelines and implements the TriCore (Infineon) instruction set. Each core provides up to four thread slots (separate instruction windows and register sets per thread), which allows simultaneous execution of one hard real-time task and three non-hard real-time tasks.

The processor architecture contains one inter-core bus arbiter, which arbitrates requests from different cores, and four intra-core bus arbiters (one per core) that arbitrate among thread requests from the same core. The processor shared memory can suffer from both intra- and inter-core interferences. To avoid these interferences, authors proposed a dynamically partitioned memory, which assigns a private subset of memory banks to each hard real-time task so that no other task has access to it (the Merasa operating system sets the memory partition assigned to each core by modifying special hardware registers). Also, the MERASA processor runs based on a Round Robin bus policy.

The MERASA system-level software represents an abstraction layer between the application software and the embedded hardware. It provides the basic functionalities of a real-time operating system as a foundation for application software running on the MERASA processor. MERASA system-level software guarantees the isolation of memory accesses of various hard real-time tasks that are running on different cores to avoid mutual and possibly unpredictable interferences. This isolation should also enable a tight WCET analysis of application code. The resulting system software can execute hard real-time tasks in parallel on different cores of the MERASA multicore processor.

The MERASA processor and techniques were validated by means of determining WCET for a given application based on the use of two CAD tools, one academic and one from industry: OTAWA (BALLABRIGA et al., 2010) and RapiTime (RAPITA SYSTEMS LTD, 2015b), respectively. While OTAWA extracts the control flow graph (CFG) from the binary code (thus, performing static timing analysis), RapiTime uses the extracted traces to estimate the WCET by measurements/simulations of the target hardware. Further, the MERASA project was continued on a new action: parMERASA (UNGERER et al., 2013).

Considered all the above mentioned approaches, our proposed approach represents a considerable improvement of the state-of-the-art, since:

- a) They are not trivial in such a way that they must not only analyze all interactions between pipeline and cache models of a single core when executing a given critical task. They also analyze all inter-core conflicts generated during the execution of the critical and the various less-critical workloads and their non-uniform and concurrent memory bus accesses. Note that such analysis is even more complex when the number of cores running in parallel increases.

- b) If the number of tasks changes, the whole process must be recomputed in order to reschedule the tasks into the TDMA (resp. FCFS or Round-Robin) bus slots.

- c) It may happen that after predicting the execution of a critical task in a given multicore platform, the designer concludes that this task is not schedulable when executed in concurrence with other (less-critical) tasks. So, the whole analysis is useless and a new analysis process must restart on the basis of a smaller number of less-critical tasks to running in parallel with the critical one. The final goal is to guarantee schedulability of the critical task. If this is not attained yet, then the whole process is restarted again with an even smaller number of less-critical tasks. This "re-do" work is long and complex. So, time consuming.

- d) Unlike the previous methods, in our approach, the WCET computation for the critical task is computed *independently* of the number of less critical tasks running in any number of cores concurrently with the critical task in the critical core. This renders the system design complexity much lower than in the case of the previous approaches. Furthermore if the number of less critical tasks changes (and the number

of less critical cores as well), the WCET of the critical task does not need to be recomputed.

## 2.4 LEON3 Processor

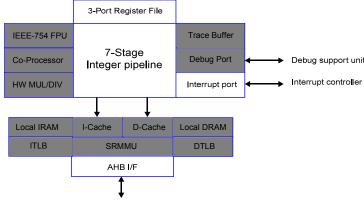

LEON3 is a 32-bit processor core that conforms to the IEEE-1754 (SPARC-V8) (SPARC International INC., 1992) architecture. It is designed for embedded applications and implements a 7-stage pipeline with separate instruction and data caches, memory management unit, hardware multiplier and divider, on-chip debug support and multiprocessor extensions (COBHAM GAISLER AB, 2015).

Figure 6 depicts the block diagram of the LEON3 core, the indicated blocks are optional, the "Interrupt port" is required for multi-processor systems, since it is used to start the cores.

Figure 6 – LEON3 processor core block diagram.

AMBA AHB Master (32-bit)

Reference: Modified from COBHAM GAISLER AB (2015).

## 2.4.1 Instruction Pipeline

The LEON3 integer unit is composed by 7 stages, uses a single instruction issue pipeline, and is depicted below (COBHAM GAISLER AB, 2015):

- 1. FE (Instruction Fetch): The instruction is fetched from the instruction cache if the cache is enabled. Otherwise, the fetch is performed in the AHB bus.

- 2. DE (Decode): The instructions are decoded and the target addresses of the CALL and Branch instructions are generated.

- 3. RA (Register access): Operands are read from the register file or from internal data bypasses.

- 4. EX (Execute): ALU, logical, and shift operations are performed. The address is generated for memory operations (e.g., LD) and for JMPL/RETT instructions.

- 5. ME (Memory): Data cache is read or written at this stage.

- 6. XC (Exception) Traps and interrupts are resolved. The data is aligned as appropriate for cache reads.

- 7. WR (Write): The result of ALU, logical, shift, or cache operations are written back to the register file.

## 2.4.2 Debug Support Unit (DSU)

The Debug support unit is connected to the LEON3 pipeline and allows nonintrusive debugging of applications running the processor. Four watchpoint registers can be enabled, which allows hardware breakpoints to be placed in the application. The trace buffer monitors and stores executed instructions, which can then be read via the debug interface. It consists of a circular buffer that stores executed instructions information. The following information is stored in real-time without performance degradation:

- Instruction address and opcode

- Instruction result

- Load/store data and address

- Trap information

- 30-bit time tag

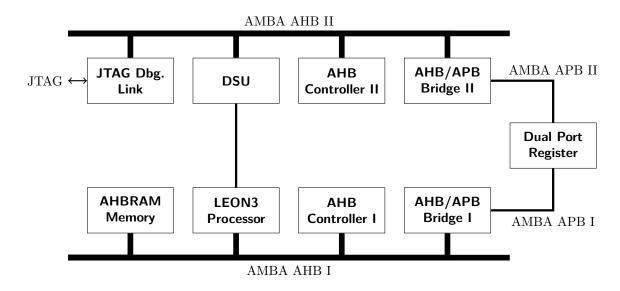

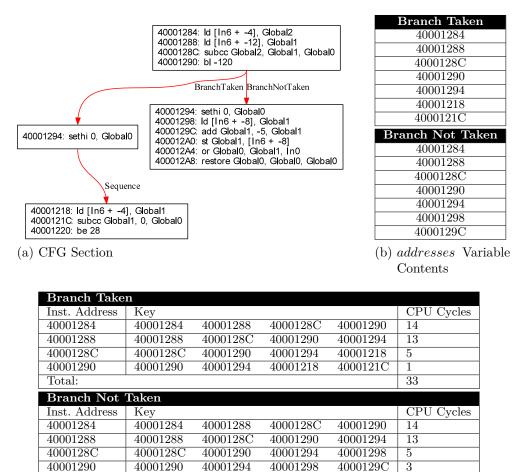

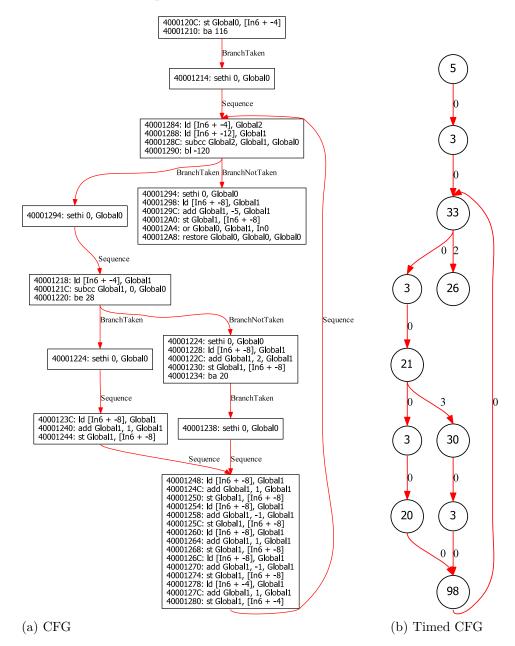

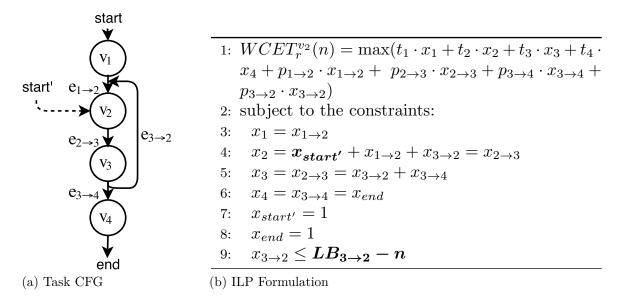

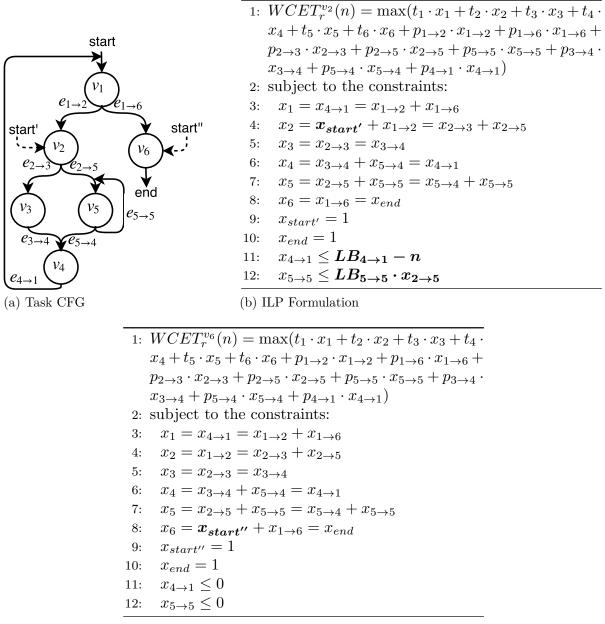

## 2.4.3 AMBA interface