Pontifical Catholic University of Rio Grande do Sul - PUCRS School of Engineering Graduate Program in Electrical Engineering

Guilherme Cardoso Medeiros

## Development of a Test Methodology for FinFET-Based SRAMs

Porto Alegre, Brazil 2017

### Development of a Test Methodology for FinFET-Based SRAMs

Dissertação de mestrado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica da Pontifícia Universidade Católica do Rio Grande do Sul, como parte dos requisitos para a obtenção do título de Mestre em Engenharia Elétrica. Área de concentração: Sinais, Sistemas e Tecnologia da Informação.

Linha de Pesquisa: Sistemas de Computação.

Pontifical Catholic University of Rio Grande do Sul - PUCRS

School of Engineering

Graduate Program in Electrical Engineering

Advisor: Leticia Maria Bolzani Poehls, Ph.D.

Porto Alegre, Brazil 2017

### DEVELOPMENT OF A TEST METHODOLOGY FOR FINFET-BASED SRAMS

#### CANDIDATO: GUILHERME CARDOSO MEDEIROS

Esta Dissertação de Mestrado foi julgada para obtenção do título de MESTRE EM ENGENHARIA ELÉTRICA e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia Elétrica da Pontifícia Universidade Católica do Rio Grande do Sul.

**RIA BOLZANI POEHLS - ORIENTADORA** DRA. LETÍCIA MÁ

**BANCA EXAMINADORA**

DR. VICTOR CHAMPAC VILELA - ELECTRÓNICA - NATIONAL INSTITUTE FOR ASTROPHYSICS, OPTICS AND ELECTRONICS

DR. FABIAN LUIS VARGAS - PPGEE - FENG - PUCRS

Av. lpiranga, 6681 - Predio 30 - Bloco A - Sala 103 | CEP 90619-900 | Porto Alegre, RS - Brasil Fone: (51) 3320-3540 | E-mail: engenharia.pg.eletrica@pucrs.br | www.pucrs.br

## Acknowledgements

Foremost, I wish to express my sincere gratitude to Prof. Letícia Poehls, my adviser. I am extremely thankful and indebted to her for sharing her knowledge, as well as her valuable guidance throughout this entire work. Your advice on both this research as well as subjects related to my future steps have been priceless.

I would like to thank Dr. Fabian Luís Vargas for his insightful comments, hard questions, and the interest he has shown on me.

My deepest gratitude to M.Sc. Thiago Copetti for working alongside with me and the hours spent talking about this work. My sincere thank you.

I am grateful to this university, the Pontifical Catholic University of Rio Grande do Sul, and CAPES, for providing me with all the necessary facilities and financial support for this work.

Finalmente, aos meus pais e amigos, um muito obrigado pela compreensão e apoio que recebi de vocês.

## Abstract

Miniaturization has been the industry's main goal over the last few years, as it brings benefits such as high performance and on-chip integration as well as power consumption reduction. Alongside the constant scale-down of Integrated Circuits (ICs) technology, the increasing need to store more and more information has resulted in the fact that Static Random Access Memories (SRAMs) occupy great part of Systems-on-Chip (SoCs).

The constant evolution of nanotechnology brought many revolutions to semiconductors, making it also necessary to improve the integrated circuit manufacturing process. Therefore, the use of new, complex processing steps, materials, and technology has become necessary.

The technology-shrinking objective adopted by the semiconductor industry promoted research for technologies to replace CMOS transistors. FinFET transistors, due to their superior electrical properties, have emerged as the technology most probably to be adopted by the industry.

However, one of the most critical downsides of technology scaling is related to the non-determinism of device's electrical parameters due to process variation. Miniaturization has led to the development of new types of manufacturing defects that may affect IC reliability and cause yield loss.

With the production of FinFET-based memories, there is a concern regarding embedded memory test and repair, because fault models and test algorithms used for memories based on conventional planar technology may not be sufficient to cover all possible defects in multi-gate memories. New faults that are specific to FinFETs may exist, therefore, current test solutions, which rely on operations executing specific patterns and other stressing conditions, may not stand to be reliable tools for investigating those faults.

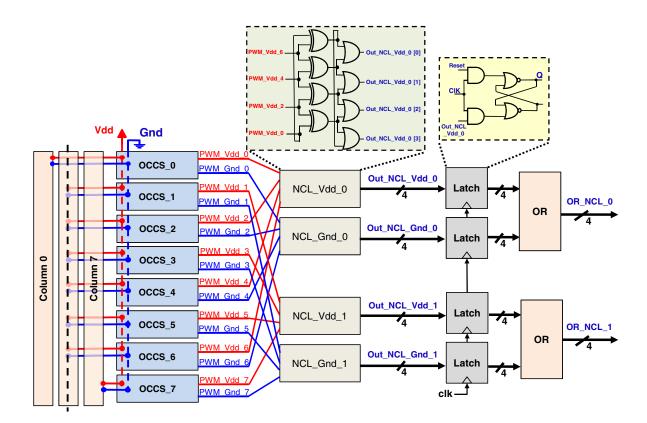

In this context, this work proposes a hardware-based methodology for testing memories implemented using FinFET technology that monitors aspects of the memory array and creates output signals deriving from the behavior of these characteristics. Sensors monitor the circuit's parameters and upon changes from their idle values, create pulses that represent such variations. These pulses are modulated applying the pulse width modulation techniques. As resistive defects alter current consumption and bit line voltages, cells affected by resistive defects present altered modulated signals, validating the proposed methodology and allowing the detection of these defects. This further allows to increase the yield after manufacturing and circuit reliability during its lifetime. Considering how FinFET technology has evolved and the likelihood that ordinary applications will employ FinFET-based circuits in the future, the development of techniques to ensure circuit reliability has become a major concern.

The presented hardware-based methodology, which was implemented using On-Chip Sensors, has been divided in two approaches: monitoring current consumption and monitoring the voltage level of bit lines. Each approach has been validated by injecting a total of 12 resistive defects, and evaluated considering different operation temperatures and the impact of process variation.

Key-words: FinFET. SRAM. Resistive Defects. Process Variation.

## Resumo

Miniaturização tem sido adotada como o principal objetivo da indústria de Circuitos Integrados (CIs) nos últimos anos, uma vez que agrega muitos benefícios tais como desempenho, maior densidade, e baixo consumo de energia. Junto com a miniaturização da tecnologia CMOS, o aumento na quantidade de dados a serem armazenados no chip causaram a ampliação do espaço ocupado por memórias do tipo *Static Random-Access Memory* (SRAM) em *System-on-Chips* (SoCs).

Tal miniaturização e evolução da nanotecnologia proporcionou muitas revoluções na indústria de semicondutores, tornando necessário também a melhoria no processo de fabricação de CIs. Devido a sensibilidade causada pela miniaturização e pelas variabilidades de processo de fabricação, eventuais defeitos introduzidos durante fabricação podem danificar o CI, afetando o nível de confiabilidade do CI e causando perdas no rendimento por *die* fabricado.

A miniaturização adotada pela indústria de semicondutores impulsionou a pesquisa de novas tecnologias visando a substituição de transistores do tipo CMOS. Transistores FinFETs, devido a suas propriedades elétricas superiores, emergiram como a tecnologia a ser adotada pela indústria.

Com a fabricação de memórias utilizando a tecnologia FinFET, surge a preocupação com testes de memória, uma vez que modelos de falhas e metodologias de teste utilizados para tecnologias planares podem não ser suficientes para detectarem todos os defeitos presented em tecnologias *multi-gate*. Uma vez que esta nova tecnologia pode ser afetada por novos tipos de falhas, testes que dependem da execução de operações, métodos de endereçamento, checagem de padrões, e outros tipos de condições de estímulo, podem deixar de serem estratégias confiáveis para o teste dos mesmos.

Neste contexto, este trabalho de mestrado propõe uma metodologia baseada em hardware para testar memórias em FinFET que monitore parâmetros do bloco de memória e gere sinais baseados nessas características. Através do uso de sensores que monitoram os parâmetros do circuito (como consumo de corrente, tensão nas *bit lines*) e detectam mudanças dos padrões monitorados, os sensores criam pulsos que representam essas variações. Esses pulsos são modulados usando técnicas de modulação. Uma vez que defeitos resistivos alteram os parâmetros monitorados, células afetadas por esses defeitos apresentam diferentes sinais modulados, validando a metodologia proposta e permitindo a detecção destes defeitos e consequentemente aumentando o *yield* de fabricação e a confiabilidade do circuito ao longo da sua vida.

A metodologia baseada em hardware proposta neste trabalho foi implementada utilizando sensores integrados no próprio CI, e foi dividida em duas abordagens: monitoramento de consumo de corrente e monitoramento da tensão nas *bit lines*. Cada abordagem foi validada com a injeção de 12 defeitos resistivos de diferentes naturezas e localizações, a após validados considerando diferentes temperaturas de operação e o impacto da variação de processo de fabricação.

**Palavras-chaves**: FinFET. Memórias SRAM. Defeitos Resistivos. Processo de Variação.

# List of Figures

| Figure 1 – Tied-Gate FinFET structure, and its parameters                                | 24 |

|------------------------------------------------------------------------------------------|----|

| Figure 2 – Schematic representations of Tied-Gate and Independent-Gate FinFETs.          | 24 |

| Figure 3 – FinFET Current flow.                                                          | 24 |

| Figure 4 – A five fin FinFET transistor.                                                 | 25 |

| Figure 5 – PV affecting multiple dies                                                    | 26 |

| Figure 6 – FinFET-specific defects.                                                      | 27 |

| Figure 7 – 6T FinFET SRAM Cell Schematic.                                                | 28 |

| Figure 8 – SRAM Block consisting of $(M+1)x(N+1)$ cells                                  | 29 |

| Figure 9 – Difference between Open Defects (MINAYA, 2014)                                | 30 |

| Figure 10 $-A$ bridge defect connecting two independent points (MINAYA, 2014) .          | 31 |

| Figure 11 – Architecture of the hardware-based approach proposed in (GOMEZ et            |    |

| al., 2016)                                                                               | 35 |

| Figure 12 – NMOS DC Analysis for different $V_{GS}$                                      | 39 |

| Figure 13 – NMOS DC analysis for different configurations.                               | 40 |

| Figure 14 – Static Noise Margin.                                                         | 40 |

| Figure 15 $-$ Static Noise Margin for different cell configurations using 2 or 3 fins on |    |

| PU and PD                                                                                | 41 |

| Figure 16 – Read Operations on a 6T SRAM Cell.                                           | 42 |

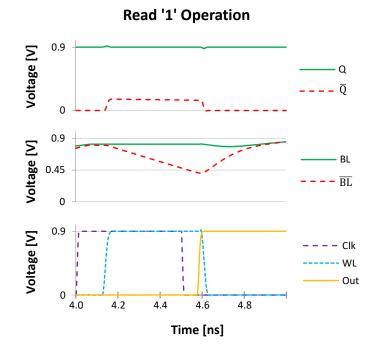

| Figure 17 $-$ Simulation of a Read Operation on the designed memory cell                 | 42 |

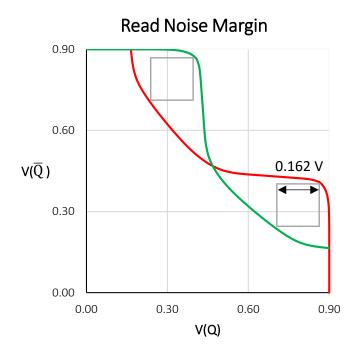

| Figure 18 – Read Noise Margin of the designed memory cell                                | 43 |

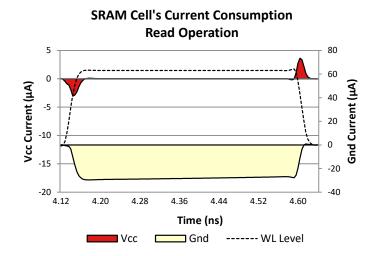

| Figure 19 $-$ SRAM Cell's current consumption on Read Operations                         | 44 |

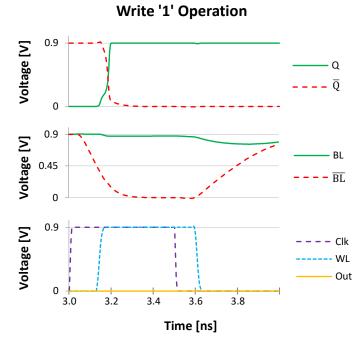

| Figure 20 $-$ Simulation of a Write Operation on the designed memory cell                | 44 |

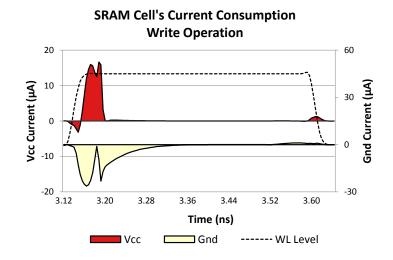

| Figure 21 – SRAM Cell's current consumption on write operations                          | 45 |

| Figure 22 – Precharger Circuit.                                                          | 46 |

| Figure 23 – Write Driver Circuit.                                                        | 46 |

| Figure 24 – Differential Sense Amplifier Circuit.                                        | 47 |

| Figure 25 $-$ Resistive-Open defects injected in the proposed 6T FinFET-based SRAM       |    |

| Cell                                                                                     | 47 |

| Figure 26 – Resistive-Bridge defects injected in the proposed 6T FinFET-based            |    |

| SRAM Cell                                                                                | 48 |

| Figure 27 – Architecture of the hardware-based approach.                                 | 49 |

| Figure 28 – Diagram of both stages of the designed sensor                                | 50 |

| Figure 29 – Diagram of the designed sensor for the current consumption monitoring        |    |

| approach                                                                                 | 51 |

| Figure 30 – Schematic of the designed current consumption sensor.                        | 52 |

| Figure 31 | -Schematic of the designed voltage level sensor                                           | 53 |

|-----------|-------------------------------------------------------------------------------------------|----|

| Figure 32 | –Organization of the SRAM Memory array and its peripherals                                | 55 |

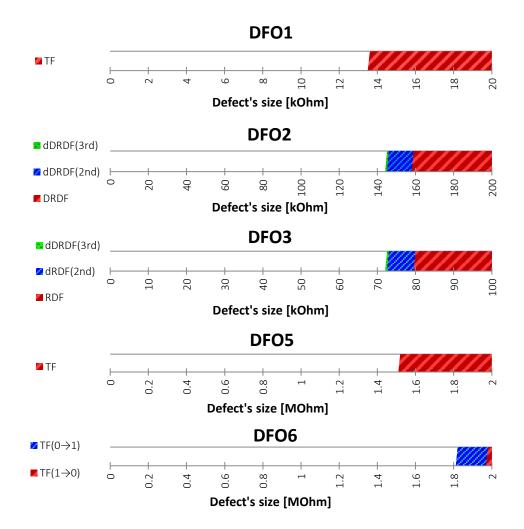

| Figure 33 | –Faults observed on cells affected by Resistive Open defects                              | 56 |

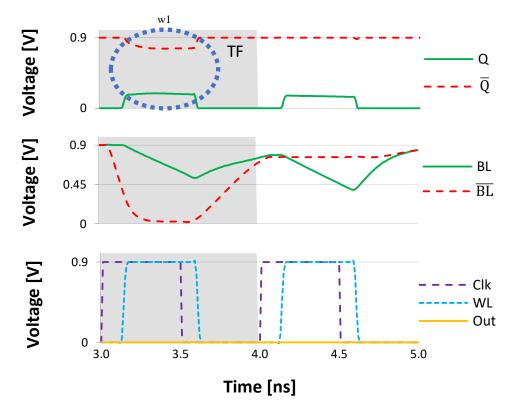

| Figure 34 | – A TF on a cell affected by a DFO1 of 16k $\Omega$                                       | 57 |

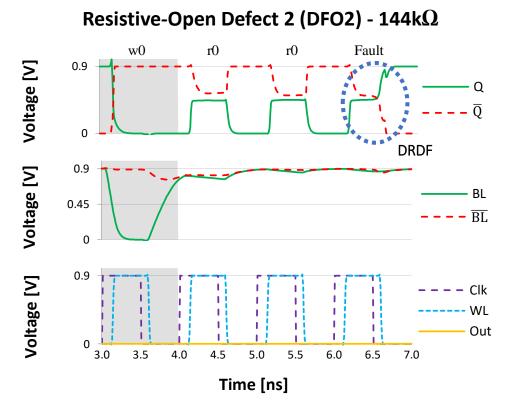

| Figure 35 | –A dDRDF on a cell affected by a DFO2 of 144k $\Omega.$                                   | 58 |

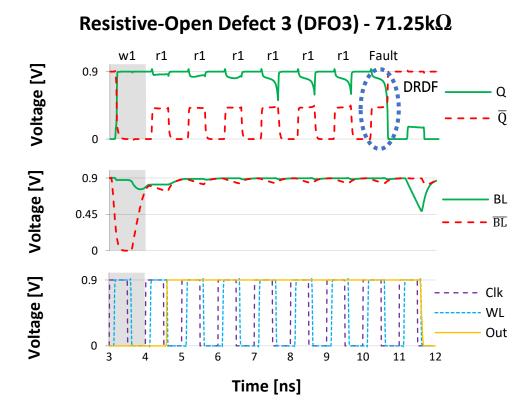

| Figure 36 | –A dDRDF on a cell affected by a DFO3 of 71.25k $\Omega.$                                 | 58 |

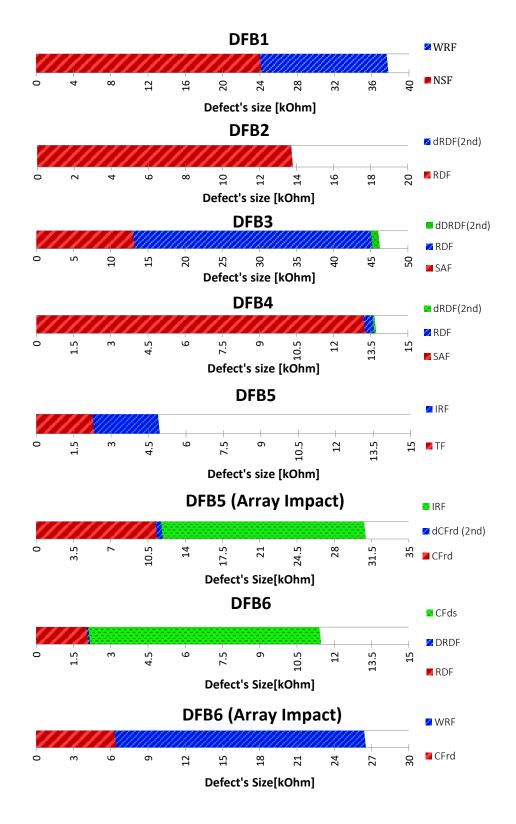

| Figure 37 | –Faults observed on cells affected by Resistive Bridge defects                            | 60 |

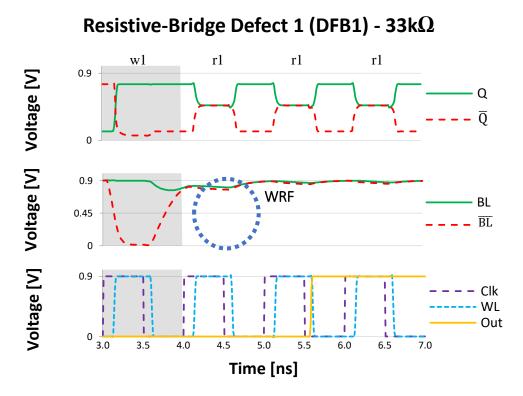

| Figure 38 | – A WRF on a cell affected by a DFB1 of $33k\Omega.$                                      | 61 |

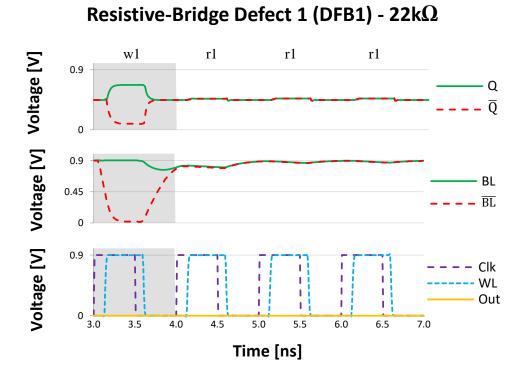

| Figure 39 | – A NSF on a cell affected by a DFB1 of $22k\Omega.$ $\hfill \ldots$                      | 61 |

| Figure 40 | –A dDRDF on a cell affected by a DFB3 of 46.1k $\Omega.$ $~$                              | 62 |

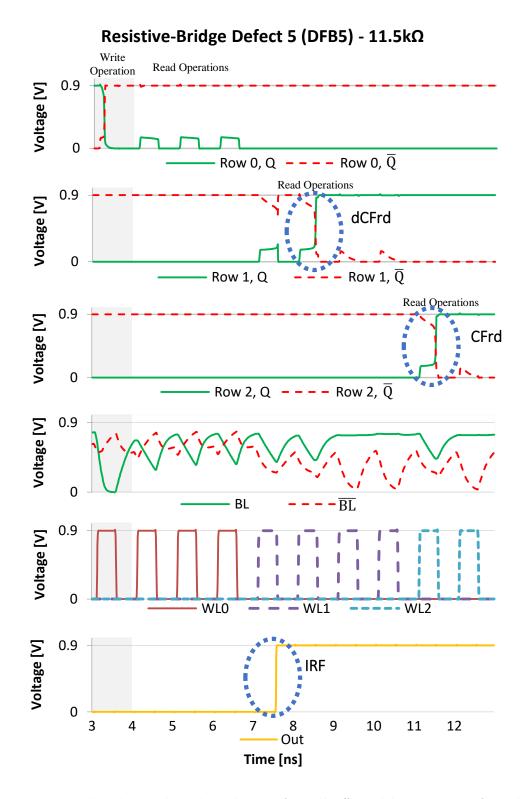

| Figure 41 | –Faults observed in the column of a cell affected by a DFB5 of $11.5 \mathrm{k}\Omega.$ . | 63 |

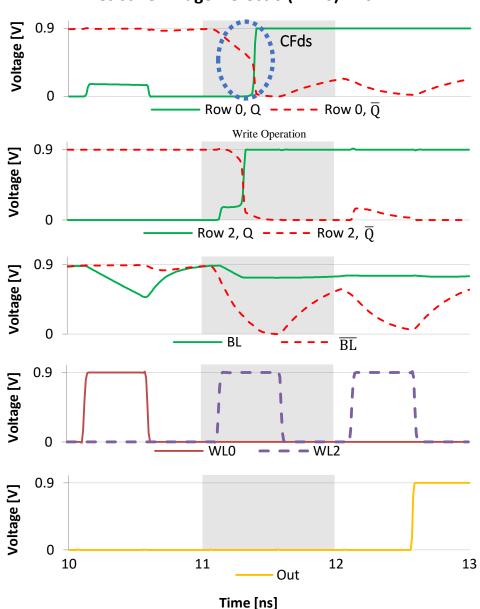

| Figure 42 | –Simulation output of a cell affected by a DFB6 of $10 \mathrm{k}\Omega$ suffering a CFds |    |

|           | fault caused by an operation in a neighbor cell. $\ldots$ $\ldots$ $\ldots$ $\ldots$      | 64 |

| Figure 43 | –Simulation output of a cell affected by a DFB4 of 13k0                                   | 65 |

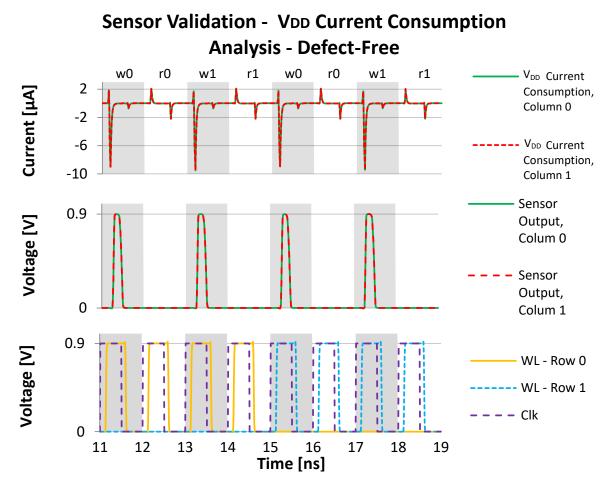

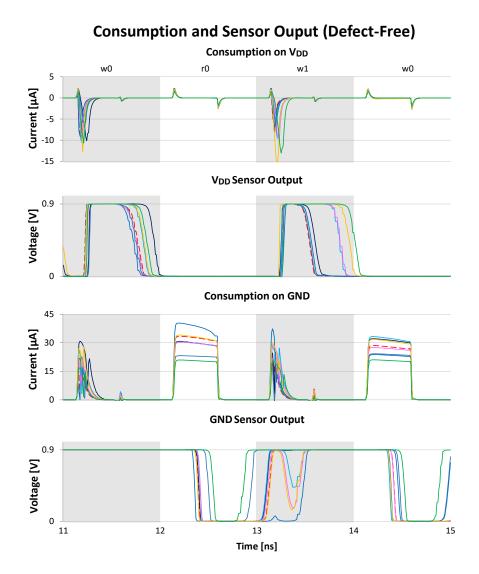

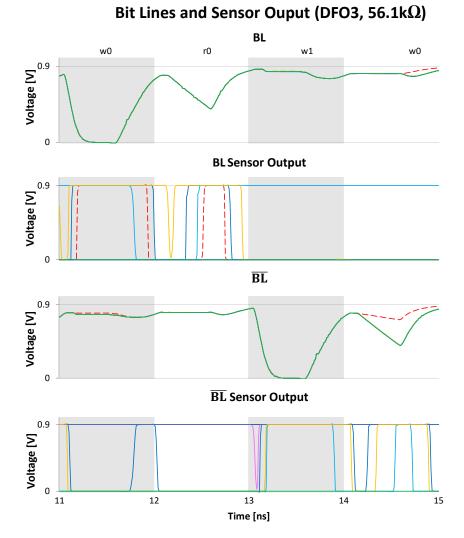

| Figure 44 | –Sensor output when monitoring $V_{DD}$ current consumption on defect-                    |    |

|           | free columns.                                                                             | 66 |

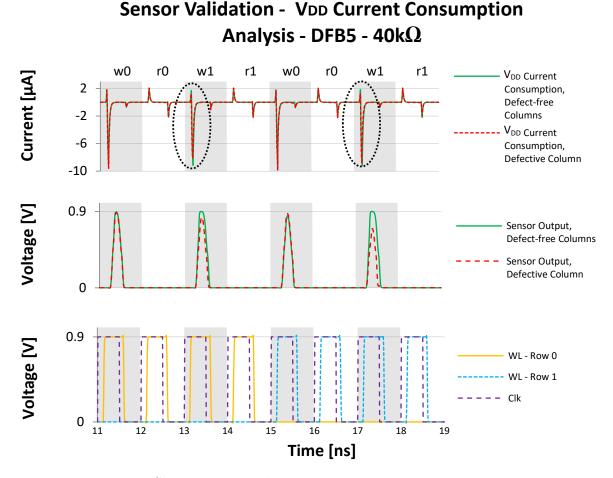

| Figure 45 | -Sensor output when monitoring $V_{DD}$ current consumption                               | 67 |

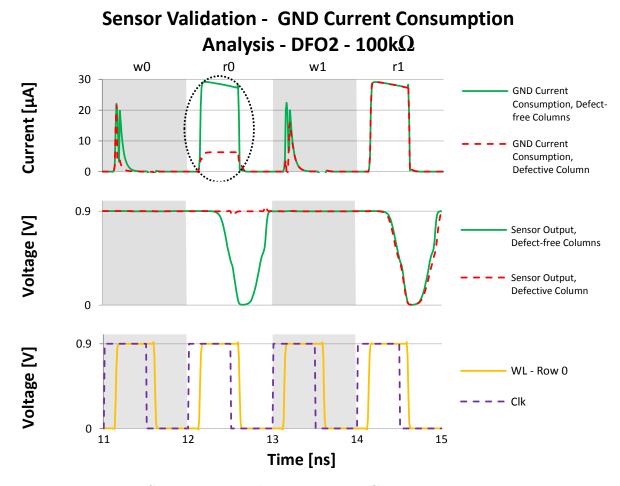

| Figure 46 | –Sensor output when monitoring GND current consumption. $\ldots$ .                        | 68 |

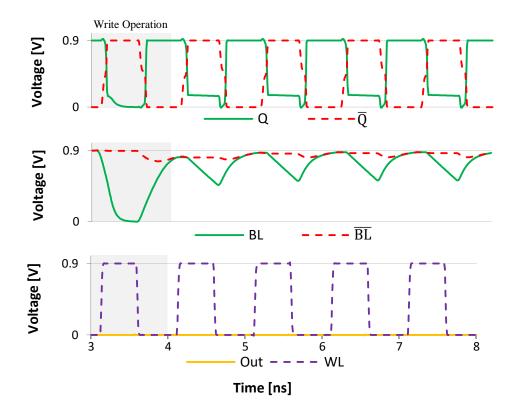

| Figure 47 | –Sensor output when monitoring $BL$ current consumption on defect-free                    |    |

|           | columns                                                                                   | 69 |

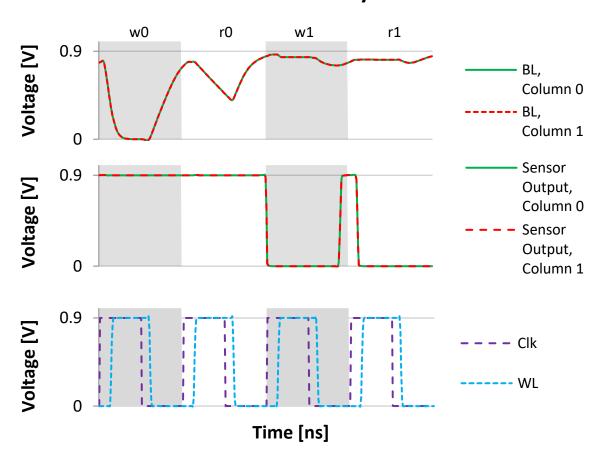

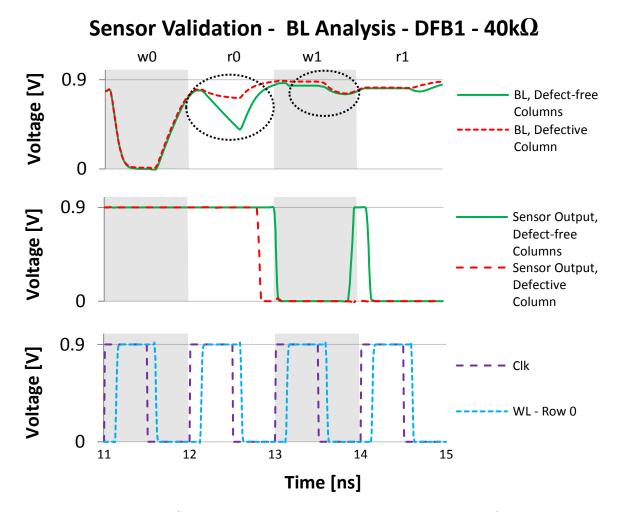

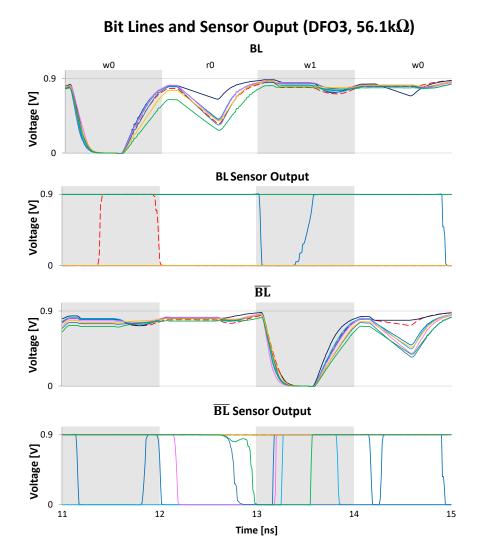

| Figure 48 | –Sensor output when monitoring voltage level of $BL$                                      | 70 |

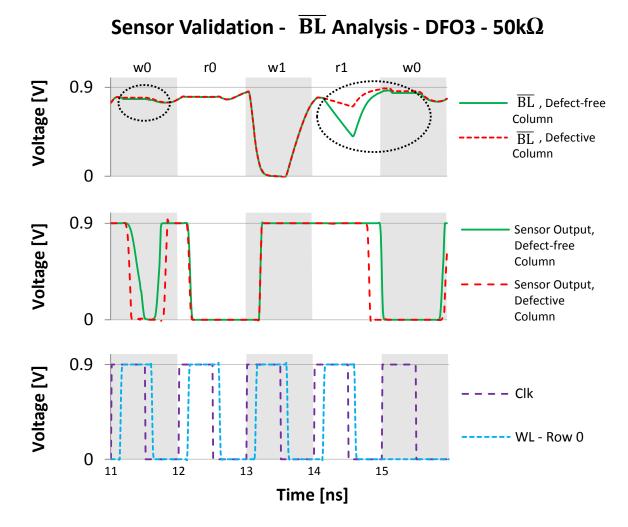

| Figure 49 | –Sensor output when monitoring voltage level of $\overline{BL}$                           | 71 |

| Figure 50 | – Detection mechanism adopted to evaluate the efficiency of the proposed                  |    |

|           | methodology                                                                               | 76 |

| Figure 51 | –Sensor's output in the presence and absence of a detection logic circuit.                | 78 |

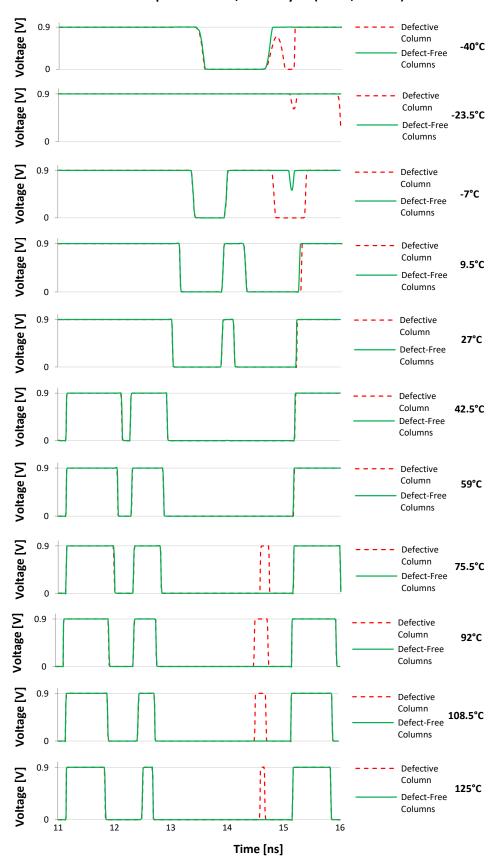

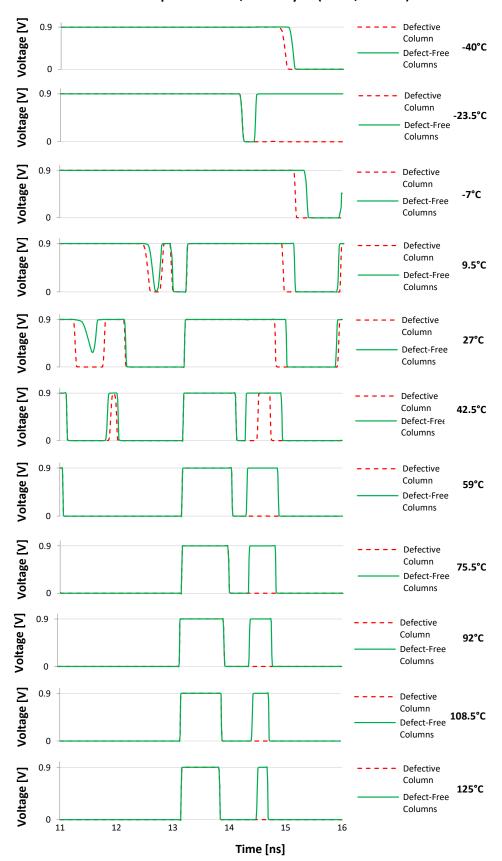

| Figure 52 | -Variation of current consumption on $V_{DD}$ for different temperatures of operation.    | 81 |

| Figure 53 | -Variation of current consumption on GND for different temperatures                       | -  |

| 0         | of operation.                                                                             | 82 |

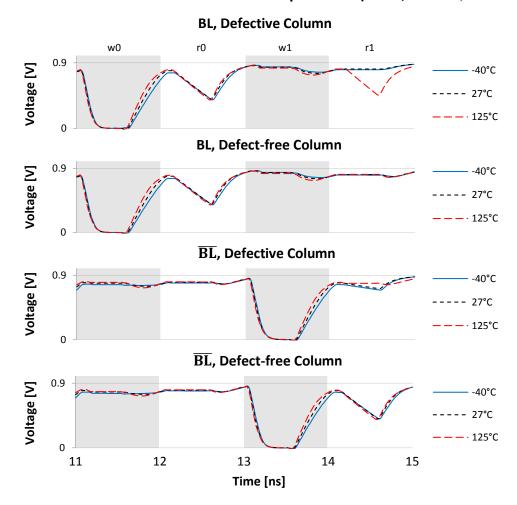

| Figure 54 | -Variation of Voltage Level on Bit Lines considering three different tem-                 |    |

| 0         | perature corners.                                                                         | 87 |

| Figure 55 | -Impact of temperature variation on sensor's output when monitoring                       |    |

| 0         | BL                                                                                        | 88 |

| Figure 56 | -Impact of temperature variation on sensor's output when monitoring $\overline{BL}$ .     | 89 |

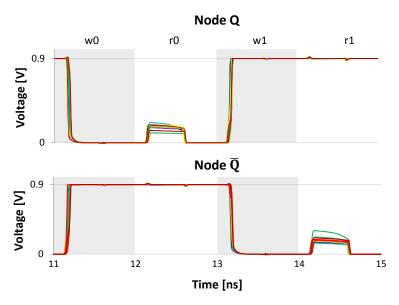

| Figure 57 | –Stored value in a cell in Monte Carlo simulations considering Inter-Die                  |    |

| -         | variations for $H_{FIN}$ , and Intra-Die variations for $PHIG$ , $T_{FIN}$ , and L.       | 96 |

| Figure 58 | -Stored value in a cell affected by a DFO3 in Monte Carlo simulations                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | for Inter-Die Process Variations                                                                                                                       |

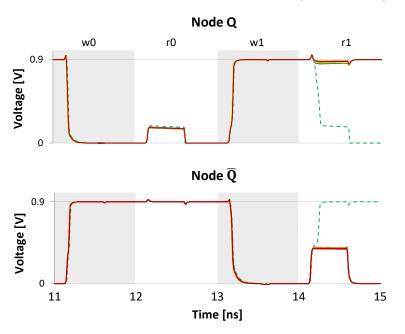

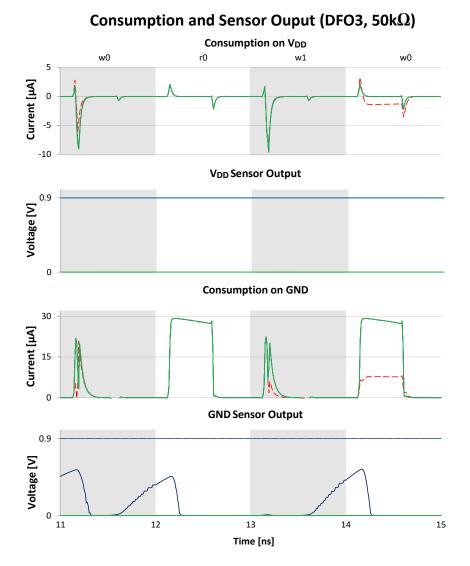

| Figure 59 | -Consumption and Sensor output of an Iteration of the Monte Carlo sim-                                                                                 |

|           | ulations for the Current Consumption approach altering the memory                                                                                      |

|           | block and peripherals                                                                                                                                  |

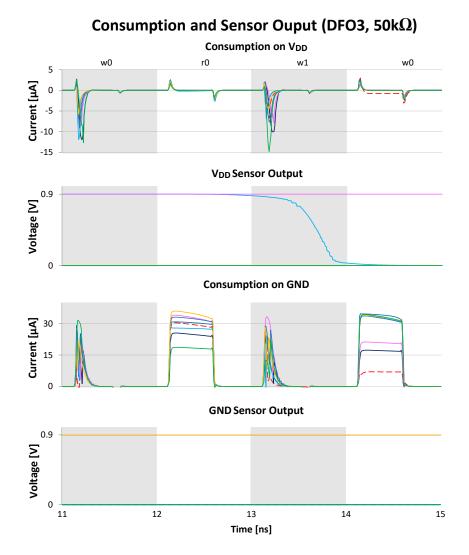

| Figure 60 | –Consumption and Sensor output of an Iteration of the Monte Carlo                                                                                      |

|           | simulations for the Current Consumption approach altering only sensors. $100$                                                                          |

| Figure 61 | $-\operatorname{Consumption}$ and Sensor output of an Iteration of the Monte Carlo sim-                                                                |

|           | ulations for the Current Consumption approach altering all transistor                                                                                  |

|           | in the circuit. $\ldots$                                              |

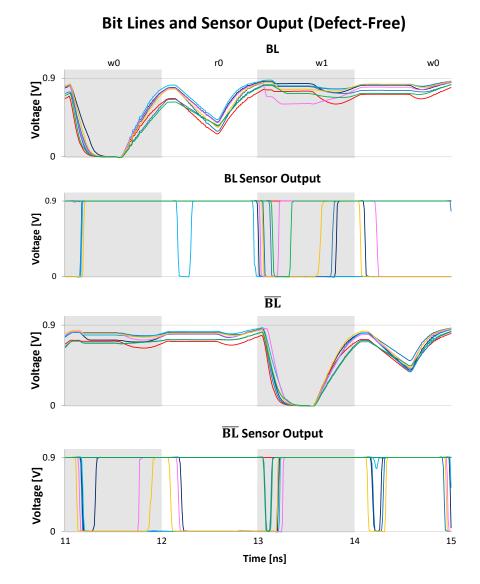

| Figure 62 | –Bit Lines and Sensor output of an Iteration of the Monte Carlo simula-                                                                                |

|           | tions for the Bitline Voltage Level approach altering parameters in the                                                                                |

|           | memory block and peripherals                                                                                                                           |

| Figure 63 | –Consumption and Sensor output of an Iteration of the Monte Carlo                                                                                      |

|           | simulations for the Bitline Voltage Level approach altering only sensors. 103                                                                          |

| Figure 64 | –Consumption and Sensor output of an Iteration of the Monte Carlo                                                                                      |

|           | simulations for the Bitline Voltage Level approach altering all transistor                                                                             |

|           | in the circuit. $\ldots \ldots \ldots$ |

# List of Tables

| Table 1 – | PTM 20nm Model Parameters                                                   | 39 |

|-----------|-----------------------------------------------------------------------------|----|

| Table 2 – | Critical resistance values for different temperatures.                      | 73 |

| Table 3 – | Critical resistances for different temperatures                             | 74 |

| Table 4 – | Comparison of critical resistances of static faults between the three cir-  |    |

|           | cuits addressed in this work.                                               | 75 |

| Table 5 – | Critical Resistances and detection efficiency for both approaches           | 77 |

| Table 6 – | Critical Resistance for each defect in different temperatures for the Cur-  |    |

|           | rent Consumption Approach.                                                  | 83 |

| Table 7 – | Overall results on the evaluation of the impact of temperature on the       |    |

|           | Current Consumption approach.                                               | 84 |

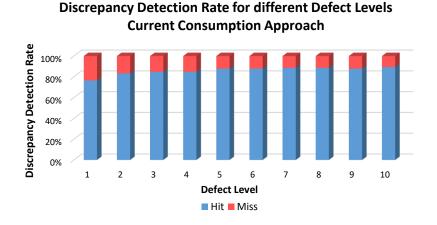

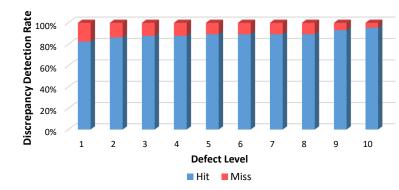

| Table 8 – | Summary of discrepancy detection rate for each of the resistive defects     |    |

|           | for the Current Consumption approach.                                       | 84 |

| Table 9 – | Discrepancy detection rate for different temperatures of operation for      |    |

|           | the Current Consumption approach.                                           | 84 |

| Table 10  | –Summary of discrepancy detection rate for resistive-open and resistive-    |    |

|           | bridge defects for the Current Consumption approach                         | 85 |

| Table 11  | –Summary of discrepancy detection rates on the $V_{DD}$ and GND sensor      |    |

|           | for the Current Consumption approach.                                       | 85 |

| Table 12  | -Hit/Miss rate based on the size of analyzed defect for the Current Con-    |    |

|           | sumption approach.                                                          | 86 |

| Table 13  | -Critical Resistance for each defect in different temperatures for the Bit  |    |

|           | Line Voltage Level Approach                                                 | 90 |

| Table 14  | -Overall results on the evaluation of the impact of temperature on the      |    |

|           | Bit Line Voltage Level approach                                             | 91 |

| Table 15  | –Discrepancy detection rate for each of the resistive defects for the Bit   |    |

|           | Line Voltage Level approach                                                 | 91 |

| Table 16  | –Discrepancy detection rate for different temperatures of operation for     |    |

|           | the Bit Line Voltage Level approach                                         | 91 |

| Table 17  | –Discrepancy detection rate for resistive-open and resistive-bridge defects |    |

|           | for the Bit Line Voltage Level approach                                     | 92 |

| Table 18  | -Hit/Miss rate based on the size of analyzed defect for the Bit Line        |    |

|           | Voltage Level approach                                                      | 92 |

| Table 19  | – Power Overhead of the two approaches                                      | 94 |

| Table 20  | –Fins characterization of the circuits that constitute the sensors designed |    |

|           | in this work.                                                               | 94 |

| Table 21 | -Area Overhead of the two approaches for different memory block con-<br>figurations                           |

|----------|---------------------------------------------------------------------------------------------------------------|

| Table 22 | -Summary of detection rate when altering defect size in temperatures of operation ranging from -40°C to 125°C |

| Table 23 | -Resistance assigned to each level for each defect for the Current Con-<br>sumption Approach                  |

| Table 24 | -Discrepancy detection rate for each of the resistive defects for the Cur-<br>rent Consumption approach       |

| Table 25 | -Discrepancy detection rate for resistive-open defects for the Current                                        |

| Table 26 | Consumption approach                                                                                          |

|          | Consumption approach                                                                                          |

| Table 27 | -Discrepancy detection rate on the $V_{DD}$ sensor for the Current Consumption approach                       |

| Table 28 | -Discrepancy detection rate on the GND sensor for the Current Con-<br>sumption approach                       |

| Table 29 | -Resistance assigned to each level for each defect for the Bit Line Voltage                                   |

| Table 30 | Level Approach                                                                                                |

| Table 50 | Voltage Level approach                                                                                        |

| Table 31 | -Discrepancy detection rate for resistive-bridge defects for the Bit Line<br>Voltage Level approach           |

# List of Algorithms

| 1 | March SS           | 34 |

|---|--------------------|----|

| 2 | March Test Adopted | 66 |

# List of abbreviations and acronyms

| IC                  | Integrated Circuit                                |

|---------------------|---------------------------------------------------|

| MOSFET              | Metal-Oxide Semiconductor Field Effect Transistor |

| CMOS                | Complementary Metal-Oxide Semiconductor           |

| SRAM                | Static Random Access Memory                       |

| SoC                 | System-on-Chip                                    |

| PV                  | Process Variation                                 |

| SOI                 | Silicon-over-Insulator                            |

| L                   | Gate Length                                       |

| $T_{OX}$            | Gate Oxide Thickness                              |

| W                   | Gate Width                                        |

| $V_{TH}$            | Threshold Voltage                                 |

| SCE                 | Short Channel Effects                             |

| $I_{on}$            | On-State Drive Current                            |

| BOX                 | Buried Oxide                                      |

| TG                  | Tied-Gate                                         |

| $\operatorname{SG}$ | Shorted-Gate                                      |

| IG                  | Independent-Gate                                  |

| $H_{FIN}$           | Fin's Height                                      |

| $T_{FIN}$           | Fin's Width                                       |

| $T_{BOX}$           | Buried Oxide Thickness                            |

| $W_{eff}$           | Effective Width                                   |

| $V_{DD}$            | Supply Voltage                                    |

| DIBL                | Drain-Induced Barrier Lowering                    |

- BIST Built-In Self Test

- OCCS On-Chip Current Sensor

- SNM Static Noise Margin

- WL Word Line

- BL Bit Line

- GOS Gate Oxide Shorts

- SOF Stuck-Open Faults

- HP High Performance

- MG Multi-Gate

- RNM Read Noise Margin

- RB Resistive-Bridge

- RO Resistive-Open

- TF Transition Fault

- RDF Read Destructive Fault

- dRDF dynamic Read Destructive Fault

- DRDF Deceptive Read Destructive Fault

- dDRDF dynamic Deceptive Read Destructive Fault

- WRF Weak Read Fault

- NSF No Store Fault

- SAF Stuck-at Fault

- CFds Disturb Coupling Fault

- CFrd Read Disturb Coupling Fault

- dCFrd Dynamic Read Disturb Coupling Fault

- LP Low Power

- PWM Pulse Width Modulation

- w1 Write '1'

- w0 Write '0'

- SEU Single Event Upset

- NBTI Negative Bias Temperature Analysis

- CC Current Consumption

## Contents

| 1 | Intr | oductio           | on                                              | 18 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|---|------|-------------------|-------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|--|--|--|

|   | 1.1  | Motiva            | ation                                           | 19 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.2  | Object            | tives                                           | 19 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.3  | Metho             | odology                                         | 20 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.4  | Organ             | ization                                         | 20 |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 2 | Bac  | kgroun            | d                                               | 22 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.1  | FinFE             | T Technology                                    | 22 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.2  | Proces            | ss Variation                                    | 25 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.3  | Proces            | ss Variation on FinFET based circuits           | 27 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.4  | Static            | Random Access Memories                          | 27 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.5  | Defect            | , Fault, and Error                              | 29 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.6  | Resistive Defects |                                                 |    |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.6.1             | 2.6.1 Resistive-Open Defects                    |    |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.6.2             | Resistive-Bridge Defects                        | 31 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.7  |                   |                                                 |    |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.8  |                   |                                                 |    |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.8.1             | March Test                                      | 33 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.8.2             | $I_{DDQ}$ Test                                  |    |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.8.3             | On-Chip Current Sensor associated to March Test | 34 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.8.4             | Challenges on Defect Detection                  | 35 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.8.5             | Test Methodologies for FinFETs                  | 36 |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 3 | Pro  | posed 7           | Technique                                       | 38 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.1  |                   | T Technology Characterization                   |    |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.2  | FinFE             | T SRAM Cell Characterization                    | 39 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.2.1             | Read Operation                                  | 41 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.2.2             | Write Operation                                 | 43 |  |  |  |  |  |  |  |  |  |  |  |  |  |

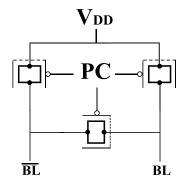

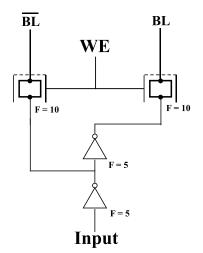

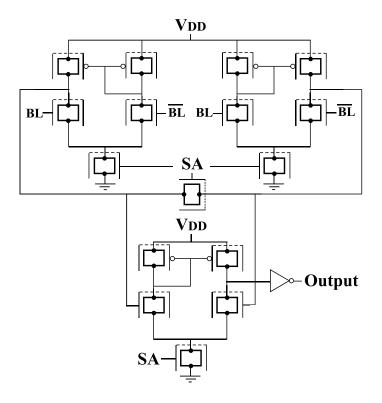

|   | 3.3  | Periph            | erals                                           | 45 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.4  | Defect            | Modeling                                        | 46 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.4.1             | Resistive-Open Defects                          | 46 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.4.2             | Resistive-Bridge Defects                        | 47 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.5  | Specifi           | ication of Hardware-Based Approach              |    |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.6  |                   | mentation                                       |    |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.6.1             | Approach 1: Current Consumption                 |    |  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.6.2             | Approach 2: Bit Line Voltage Level              |    |  |  |  |  |  |  |  |  |  |  |  |  |  |

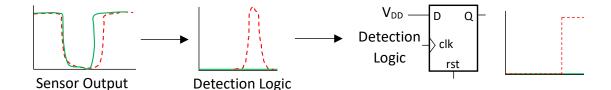

|    | 3.7                | Detect    | ion Logic                                                             |   | . 52  |  |  |  |  |  |  |  |  |  |

|----|--------------------|-----------|-----------------------------------------------------------------------|---|-------|--|--|--|--|--|--|--|--|--|

| 4  | Vali               | dation    |                                                                       |   | . 54  |  |  |  |  |  |  |  |  |  |

|    | 4.1                | Experi    | mental Setup                                                          |   | . 54  |  |  |  |  |  |  |  |  |  |

|    | 4.2                | Fault N   | Mapping on FinFET SRAMs                                               |   | . 54  |  |  |  |  |  |  |  |  |  |

|    |                    | 4.2.1     | Resistive-Open Defects                                                |   | . 55  |  |  |  |  |  |  |  |  |  |

|    |                    | 4.2.2     | Resistive-Bridge Defects                                              |   | . 59  |  |  |  |  |  |  |  |  |  |

|    | 4.3                | Validat   | ion of the proposed methodology                                       |   | . 65  |  |  |  |  |  |  |  |  |  |

|    |                    | 4.3.1     | Approach 1: Current Consumption                                       |   | . 66  |  |  |  |  |  |  |  |  |  |

|    |                    | 4.3.2     | Approach 2: Bit Line Voltage Level                                    |   | . 67  |  |  |  |  |  |  |  |  |  |

| 5  | Res                | ults, Dis | scussions, and Evaluations                                            |   | . 72  |  |  |  |  |  |  |  |  |  |

|    | 5.1                | Impact    | of Temperature on Dynamic Faults                                      |   | . 72  |  |  |  |  |  |  |  |  |  |

|    | 5.2                | Impact    | of Temperature on Faulty Behavior                                     |   | . 73  |  |  |  |  |  |  |  |  |  |

|    | 5.3                | Impact    | of the Sensor on Faulty Behavior                                      |   | . 74  |  |  |  |  |  |  |  |  |  |

|    | 5.4                | Defect    | Fault Detection                                                       |   | . 75  |  |  |  |  |  |  |  |  |  |

|    | 5.5                | Impact    | of Temperature on the Sensor's Output                                 |   | . 77  |  |  |  |  |  |  |  |  |  |

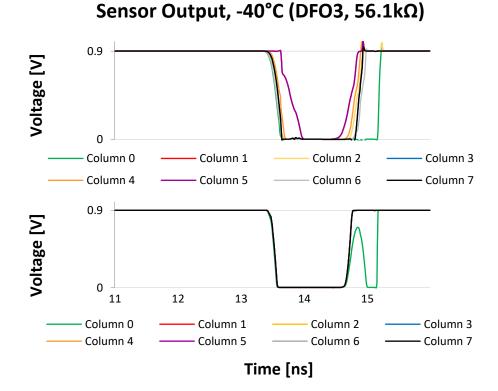

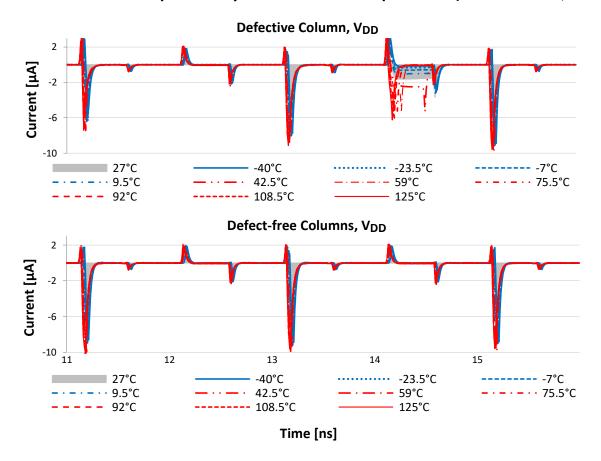

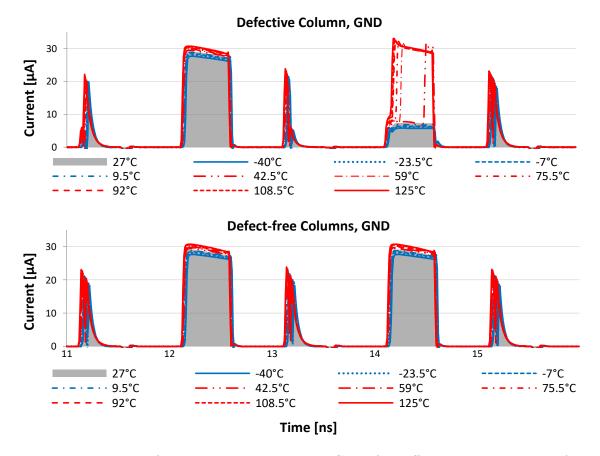

|    |                    | 5.5.1     | Approach 1: Current Consumption                                       |   | . 80  |  |  |  |  |  |  |  |  |  |

|    |                    | 5.5.2     | Approach 2: Bitline Voltage Level                                     |   | . 86  |  |  |  |  |  |  |  |  |  |

|    | 5.6                | 6         |                                                                       |   |       |  |  |  |  |  |  |  |  |  |

|    | 5.7                | Overhe    | ead Analysis                                                          |   | . 93  |  |  |  |  |  |  |  |  |  |

|    |                    | 5.7.1     | Power Consumption                                                     |   | . 93  |  |  |  |  |  |  |  |  |  |

|    |                    | 5.7.2     | Area                                                                  |   | . 94  |  |  |  |  |  |  |  |  |  |

|    | 5.8                | A Preli   | iminary Evaluation on Process Variation                               |   | . 95  |  |  |  |  |  |  |  |  |  |

|    |                    | 5.8.1     | Inter-Die Process Variation                                           |   | . 96  |  |  |  |  |  |  |  |  |  |

|    |                    | 5.8.2     | Intra-Die Process Variation                                           |   | . 97  |  |  |  |  |  |  |  |  |  |

|    |                    |           | 5.8.2.1 Approach 1: Current Consumption $\ldots \ldots \ldots \ldots$ |   | . 98  |  |  |  |  |  |  |  |  |  |

|    |                    |           | 5.8.2.2 Approach 2: Bitline Voltage Level                             |   | . 100 |  |  |  |  |  |  |  |  |  |

|    |                    |           | 5.8.2.3 Discussion                                                    |   | . 103 |  |  |  |  |  |  |  |  |  |

| 6  | <b>Fina</b><br>6.1 |           | derations                                                             |   |       |  |  |  |  |  |  |  |  |  |

| Re | eferer             | ices .    |                                                                       | - | . 108 |  |  |  |  |  |  |  |  |  |

| Aı | nnex               | Ś         |                                                                       |   | 113   |  |  |  |  |  |  |  |  |  |

| A  | NNE)               | ΚАР       | ublished Works                                                        | • | . 114 |  |  |  |  |  |  |  |  |  |

| A  | NNE)               | КВА       | utomated Tool's Report                                                |   | . 115 |  |  |  |  |  |  |  |  |  |

| ANNEX | C   | D  | et   | ect  | ion | ר ו | Го  | ol's | 5 F | Rel | po | rt | •   | •   | •             | • | • | • | • • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 11 | 7 |

|-------|-----|----|------|------|-----|-----|-----|------|-----|-----|----|----|-----|-----|---------------|---|---|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|---|

| ANNEX | D   | C  | et   | aile | ed  | Re  | epo | orts | 5.  |     |    |    |     | •   | •             |   | • |   |     | • |   | • |   |   |   | • |   |   |   |   | • |   |   | - | 11 | 8 |

| D.1   | Imp | ac | t of | Τ    | emj | pe  | rat | ur   | e c | n   | C  | CS | Ser | ıso | $\mathbf{rs}$ | 5 |   |   |     | • |   |   | • |   |   |   |   |   |   |   |   | • |   | • | 11 | 8 |

| D.2   | Imp | ac | t of | Τ    | emj | pe  | rat | ur   | e c | n   | BI | 5  | Sen | ISO | rs            |   |   |   |     | • |   | • | • |   |   |   |   |   |   |   |   | • |   | • | 12 | 0 |

## 1 Introduction

Miniaturization has been the Integrated Circuit (IC) industry's main goal for the last few years, as it brings many benefits such as high performance and on-chip integration as well as power consumption reduction. By focusing on achieving smaller systems, the IC manufacturing process has undergone many improvements. With these improvements, increasing chip density was possible and has allowed more transistors on a single die.

However, this miniaturization also presented many challenges on conventional planar MOSFET transistors, such as the ones based on Complementary Metal-Oxide Semiconductor (CMOS) technology. Because of the growing leakage and short-channels problems of this technology, it is not possible to shrink this technology below 20nm (HARU-TYUNYAN; TSHAGHARYAN; ZORIAN, 2015a) and continue with Moore's Law. Thus, due to its improved short channels and electrostatic characteristics, and design flexibility (VILLACORTA; SEGURA; CHAMPAC, 2016), the FinFET technology has become the most promising approach to continue CMOS scaling and fulfill the requirements of high performance demanded by the shrinking of devices, known as *More Moore* (HEINIG et al., 2014).

FinFETs transistors are studied since 1999, and were first described as non-planar, double-gate transistors (HUANG et al., 1999). According to (WANN et al., 1996), multigate transistors showed great potential when compared to other device structures studied, and thus were considered the most attractive device to succeed the planar CMOS transistors when the latter cannot be scaled any further.

Alongside the constant scale-down of IC technology, the increase of data needed to be stored led to a rise in the space occupied by Static Random Access Memories (SRAMs) in System-on-Chips (SoCs). Around 90% of silicon space is already dedicated to SRAMs (International Technology Roadmap for Semiconductors, 2013), thus making memories the most common element on chips. This brings special attention to identify methodical approaches that optimize them.

Technology scaling forces the manufacturing process to be more and more meticulously detailed, making Process Variation (PV) inevitable. It is impossible to assure that all chips will have exactly the same parameters, even if they are on the same wafer. Even though the vendor may guarantee parameters within certain limits, simple variations are a fact in any manufacturing process (WOLF, 1994). Those variations can affect chip reliability, since they can produce different defects, which can have a long-term impact on IC reliability.

This way, this work presents a study of the impact of resistive defects on SRAM

blocks designed using FinFET transistors. Faults models composed of static and dynamic faults are characterized according to the defect type. A hardware-based methodology that aims to monitor signals and generate distinct outputs in the presence of defects is proposed, validated and evaluated in different aspects, such as performance, impact on faulty behavior, temperature, and PV.

#### 1.1 Motivation

FinFET circuits are a relatively new approach to continue the scaling of ICs and fulfill the performance requirements established by the miniaturization-oriented goals of *More Moore* (HEINIG et al., 2014). Currently, only a few foundries are manufacturing circuits based on FinFET technology. This creates a lack of scientific and technical knowledge about critical aspects of FinFET transistors.

Little is known about the impact of manufacturing defects such as resistive-open and resistive-bridge on FinFET-based SRAM cells. Few studies that address such topics have been published, and a full understanding of the subject is still not possible.

In order to improve the set of information concerning FinFET-Based memories reliability and to explore new concepts and the suitability of already proposed ideas when applied to FinFET technology, this work proposes an investigation of several operation aspects of FinFET-based SRAM arrays and test methodologies to identify discrepancies caused by resistive defects.

Considering how far this technology has evolved and the likelihood that FinFETbased circuits will be more and more used in other applications than just rather state of the art applications in the future, it becomes crucial to have a more in-depth knowledge of this technology.

### 1.2 Objectives

This master's thesis aimed to develop a hardware-based methodology able to identify discrepancies in the behavior of selected parameters of FinFET-based SRAM arrays that may have suffered from manufacture defects. In the current industry's scenario, ICs affected by defects (and specially those defects that do not cause any logical fault) represent one of the main concerns regarding reliability as this issue is becoming more and more common due to miniaturization. Thus, new methodologies that can improve circuit's reliability are essential.

Thus, the following specific objectives have been identified:

• Contextualize the FinFET technology, addressing its main characteristics;

- Analyze the main aspects of a memory array designed with FinFET transistors;

- Establish and characterize a set of resistive defects that may pose reliability issues to FinFET memory cells;

- Perform a fault mapping to identify dynamic fault behaviors and critical resistances for each resistive defect;

- Propose a hardware-based methodology that can be used in manufacturing tests to identify the presence of resistive defects;

- Validate and evaluate the proposed hardware-based methodology regarding impact on faulty behavior, different temperatures of operation, area and power overhead, and PV.

### 1.3 Methodology

Initially, an extensive research was conducted in order to assure full understanding of all aspects that were discussed in this work. Scientific works and publications related to FinFET technologies, SRAMs, fault modeling, manufacturing defects, PV, and test methodologies were analyzed and used as background.

Then, electric models of FinFET-based memory cells and peripherals were designed. Resistive defects were modeled and injected into these cells and simulated in HSPICE 2014 in order to fully understand the impact of each defect on the behavior of the adopted memory array.

On-chip current sensors were then designed with the purpose to generate output signals that could be used to identify the existence of resistive defects. These sensors were embedded in the memory and their behavior was validated.

Finally, an extensive evaluation was carried out. The behavior in different operation temperatures was investigated. Power consumption during operations and area overhead considering the physical characteristics of transistors were analyzed. Monte Carlo simulations were used to analyze the impact of PV on the output of sensors. At last, a comparison was drawn between both approaches presented in this work.

#### 1.4 Organization

This work was divided in 6 Chapters. In Chapter 1, an introduction is presented. Chapter 2 presents a background of the main concepts addressed in this work. FinFET Technology, PV, SRAMs, Resistive defects, fault modeling, and test methodologies are discussed. Chapter 3 presents the proposed technique of this work. A characterization of the designed memory array is presented, and the specification and implementation of the hardware-based approach is laid out.

Chapter 4 presents the validation of the memory array and the sensors implemented. The experimental setup used in all simulations is defined, and first results are introduced. In Chapter 5, evaluations are carried out. Discussions regarding the impact of temperature, overheads, and PV are presented.

In Chapter 6, results obtained during evaluations are summarized and compared. Conclusions regarding mains aspects of the proposed hardware-based approach are drawn. In the end, possible future works within the scope of this thesis are discussed.

## 2 Background

Difficulties emerged due to the constant evolution and miniaturization of CMOS technology were promptly resolved and settled by improving manufacturing capabilities, allowing a substantial improvement in the industry of semiconductors and ICs.

However, miniaturization has become more and more challenging as manufacturing is reaching the materials' physical limitations. For a device length (L) of less than 100nm, saturation velocity and source velocity limit provide limited improvements in performance (LUNDSTROM, 1997). Miniaturization of the thickness of the gate dielectric  $(T_{OX})$  is also a concern. Below 1.2nm, quantum mechanical tunneling current from the gate into the channel becomes significant (MINAYA, 2014), and further reductions in  $T_{OX}$  may result in large static leakage current and large power consumption, even in the case that the device is turned off.

The manufacturing process is also approaching the equipament's limit. Technology scaling forces the manufacturing process to be more and more detailed, making PV inevitable. It is impossible to assure that all chips will have exactly the same parameters, even if they are on the same wafer. Even though the vendor may guarantee parameters within certain limits, simple variations are a fact in any manufacturing process (WOLF, 1994). These fluctuations in the manufacturing process represent variations on many parameters, such as gate length (L), gate width (W), gate oxide thickness ( $T_{OX}$ ), and threshold voltage ( $V_{TH}$ ), and are caused mainly due to sub-wavelength lithography and random dopant fluctuations. As technology shrinks, these variations start to pose a challenge in the manufacturing process' yield and circuit's reliability. Thus, new approaches are needed to allow future technology miniaturization. Multi-gate structures, such as the FinFET technology, are a promising approach.

### 2.1 FinFET Technology

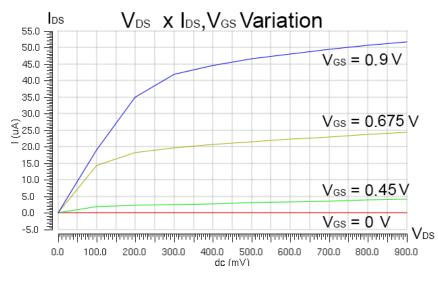

Multi-gate devices have many advantages that have been studied and demonstrated in FinFET technologies for the past decade (Fu-Liang Yang et al., 2002; ARNIM et al., 2007). Of all, the main advantage of this technology is the improved short channel effects (SCE) due to the electrostatic control of the channel made on multiple sides by the gate, which provides a better control than standard transistor structures, such as CMOS. This allows a better leakage current control, opening up the possibility for even smaller transistor and boosting even further technology's miniaturization.

A second advantage of these devices is the improved circuit speed due to a refined

on-state drive current  $(I_{on})$ . By reducing channel doping, the electric field normal to the  $SiO_2$  is minimized, which therefore reduces the surface roughness scattering. The state drive current can be improved even more by the FinFET technology, as it provides a larger channel width with a small footprint area; this raises  $I_{on}$  even more, and proves to be useful for driving large capacitive loads, such as in interconnects (MINAYA, 2014).

Finally, a last advantage of this new technology is the reduced manufacturing variation due to the absence of channel dopants, minimizing the effect of random dopant fluctuation. However, although minimized, PV may still cause reliability issues on the device, as shown by Harutyunyan (HARUTYUNYAN; TSHAGHARYAN; ZORIAN, 2015a).

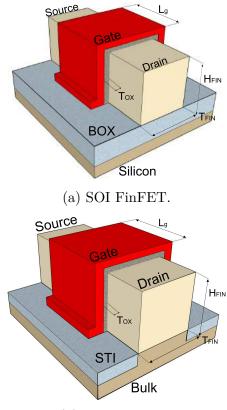

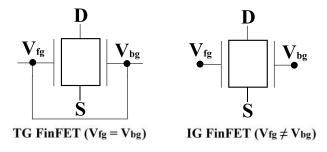

FinFET is the denomination of one of the most feasible multi-gate structures. It consists of thin, vertical slices of silicon – known as fins – that are wrapped around by the gate, and placed on top of oxide. There are many ways to construct a FinFET transistor, and each way results in a different final product (DESHMUKH et al., 2015). In Silicon-over-Insulator (SOI) FinFETs, fins are built over buried oxide (BOX) and are isolated from the substrate. In Bulk FinFETs, the fin is connected directly to the substrate through the oxide layer, and a Shallow Trench Isolation (STI) of oxide is formed on the side. There is also different gate configurations. In Tied-gate (TG) FinFETs, or as it is also called Shorted-Gate (SG) (LIU; XU, 2012), there is only one gate, and it covers the fin from all three sides. Another model is the Independent-gate (IG) FinFET, which has two gates (on front and back sides) that are controlled separately and are independent from each other (HARUTYUNYAN et al., 2014). However, most of the leading IC manufacturing companies, such as Intel and Samsung, produce mainly TG FinFETS as shown in (Samsung Semiconductor, 2013; INTEL, 2011). Consequently, the majority of research done so far focuses mostly on TG FinFETs. Fig. 1 illustrates the differences of SOI and Bulk TG FinFETs and their parameters, while Fig. 2 pictures schematic representations of both TG and IG models.

The most important parameters of a FinFET transistor are its fin's height  $(H_{FIN})$ and width  $(T_{FIN})$ , and its channel length (L) (HARUTYUNYAN; TSHAGHARYAN; ZORIAN, 2015b). Other parameters, such as gate oxide thickness  $(T_{OX})$ , buried oxide thickness  $(T_{BOX})$ , body doping, gate/source doping supply voltage, among others, complete the typical parameters of a FinFET transistor (SIMSIR; BHOJ; JHA, 2010).

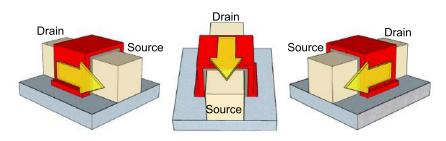

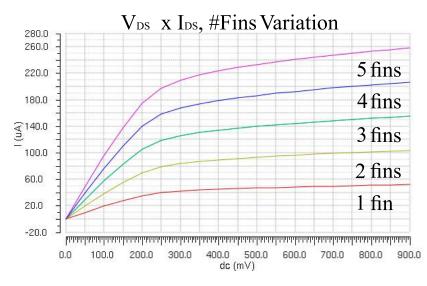

As the gate of a FinFET transistor wraps around the silicon fin, this creates three distinct channel sides – two on the side, and one on the top. Thus, another important feature of this transistor is that current flows along the top and lateral covering of the fin. This way, it is possible to define the effective channel width as  $W_{eff} = (2 \times H_{FIN} + T_{FIN}) \times NFIN$ , where NFIN is the number of fins on the transistor. Fig. 3 shows the current flow on a FinFET, represented by the yellow arrows.

Height and width of fins determine the operation of the device. By increasing

(b) Bulk FinFET.

Figure 1: Tied-Gate FinFET structure, and its parameters.

Figure 2: Schematic representations of Tied-Gate and Independent-Gate FinFETs.

Figure 3: FinFET Current flow.

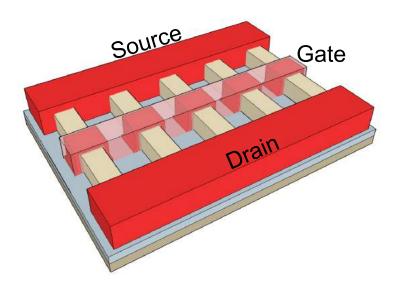

Figure 4: A five fin FinFET transistor.

width, the transistor starts to behave as a planar structure. Shrinking the width is not a problem, as the lateral gates can provide excellent control, not only reducing short channel effects, but also allowing the growing of a thicker layer of gate oxide compared to planar structures, which reduces gate tunneling leakage current and improves the drive current of the FinFET device (MINAYA, 2014). However, once the height and width of a fin are fixed, the only way to change  $W_{eff}$  and increase the channel's current drive capability is by using more fins. Fig. 4 depicts a FinFET transistor composed of five fins.

The manufacturing process of planar structures is not much different from FinFET structures. Conventional lithography and etch processes can be used to pattern and construct transistor's gates. However, fins construction requires specific steps and handling. Traditionally, the industry utilizes a technique denominated Fin-First Process (Yang-Kyu Choi; Tsu-Jae King; Chenming Hu, 2002) where the fin is the first structure built on the wafer. An alternative approach, known as Fin-Last Process (CHANG et al., 2011), can also be utilized. In this process, the fin pattern is transferred to the underlying silicon only at the end of manufacturing, when the dummy gate used during fabrication is removed.

### 2.2 Process Variation

With the consistent miniaturization of technology, the process of manufacturing is working with materials at their physical limit. In such small scale (less than a hundred nanometers), it is impossible to assure perfection. Such imperfections affect transistor's main parameters that will define the behavior of the IC, like gate length (L), gate width (W), gate oxide thickness  $(T_{OX})$ , threshold voltage  $(V_{TH})$ , etc. There are many causes for process variations, but its main sources are Sub-wavelength Lithography, material deposition and planarization, and dopant implantation (MINAYA, 2014).

Figure 5: PV affecting multiple dies.

In older technologies, a process called Photo-lithography was used to draw structures on the wafer, as the size of transistors was not so small. However, in nanometer technologies, where transistors are smaller than the wavelength of light, the lithography process must be able to print such small measures. Thus, a more developed process, called Sub-wavelength Lithography, was created. Even though this process can print smaller patterns, this new process suffers from distortions caused by optical interference and diffraction, and it is expected that as technologies shrink, the variations caused by lithographic deviations will be larger. Line width variation, corner rounding, line-end shortening, and line-edge roughness are the main types of distortions due to lithography.

During manufacturing, there are many stages where materials are deposited on the wafer or removed from it. During these stages, it is not possible to assure that, for example, all areas of the chip will be polished at the same pace. Such inconsistencies are the main cause of dishing and erosion phenomena.

Dopant implantation is the process of inserting dopant atoms into the transistor's substrate. With smaller technologies, fewer atoms are implanted, and the process of implanting it has a random behavior. Thus, such fluctuations may cause variations in transistors'  $V_{TH}$ .

Process Variations are usually divided into two groups: systematic and non-systematic. Variations that are known and can be determined before manufacturing are denominated systematic PV. During the process of back-end, after layout is finished, it is possible to measure and model these variations with fixed values and estimate the impact of these variation on the circuit's performance.

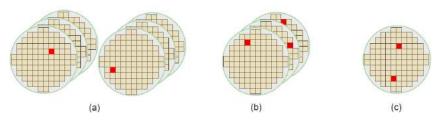

If it is not possible to determine variations before manufacturing, then such variations are denominated non-systematic. They are due to the inaccuracy of the control process. They can be partitioned into Inter-Die Variations, if the variation is perceived equally throughout the entire die, or Intra-Die Variations, if each device or interconnection in a die is affected in a different way. Fig. 5 illustrates the differences between Inter-Die variations. Lot-to-Lot (Fig. 5.a) variations are characterized by inconsistencies between batches of wafers, Wafer-to-Wafer (Fig. 5.b) by variations between wafers of the same lot, and Die-to-Die (Fig. 5.c) between dies in a same wafer.

Figure 6: FinFET-specific defects.

#### 2.3 Process Variation on FinFET based circuits

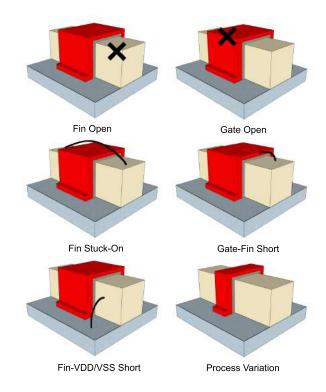

The impact of PV on FinFET transistors is not fully known . However, when compared to planar-based memories, FinFET-based memories proved to be more stable to PV faults. While changes of 20% to 40% in parameters size are enough to sensitize different types of faults in memories based on CMOS technology, for example, changes below 50% in parameters do not lead to any fault in FinFET-based memories (HARUTYUNYAN et al., 2013). It was defined in (HARUTYUNYAN; TSHAGHARYAN; ZORIAN, 2015b; HARUTYUNYAN; TSHAGHARYAN; ZORIAN, 2015a; HARUTYUNYAN et al., 2014) some of the possible altercations on FinFET transistors due to PV, which are illustrated in Fig. 6.

It is important to note that those defects shown in Fig. 6 are specific to FinFET devices. When considering other structures, one should also consider defects that are typical to planar-based structures; in memories structures, there are other defects that may affect reliability, such as resistive-bridges (RBs) between word and bit lines, resistive-opens (ROs) in the peripherals around the memory array, among others.

#### 2.4 Static Random Access Memories

Static Random Access Memories (SRAMs) are composed of cells designed to store logic values that can be retained at any time by using flip-flops. This kind of memory is

Figure 7: 6T FinFET SRAM Cell Schematic.

referred as static because it does not require periodic refresh signals in order to preserve their stored data (WOLF, 1990). There are many types of SRAM cells, and they are designed to be as small as possible to allow a higher density. However, many reliability aspects impose certain sizing restrictions (RABAEY, 1996).

When considering state-of-the-art memories, there are many factors that prevent further scaling down and improvements. One of the main concerns is the power consumption. Lowering the supply voltage  $(V_{DD})$  proves to be the best alternative to save power. Yet, conventional CMOS SRAMs are limited to miniaturization due to the random variations of threshold voltage  $(V_{TH})$  caused by Random Dopant Fluctuation. As high doping is not required in FinFETs owing to their enhanced SCE effects, Random Dopant Fluctuation is expressively reduced, which diminishes  $V_{TH}$  variations and allows  $V_{DD}$  to be scaled down.

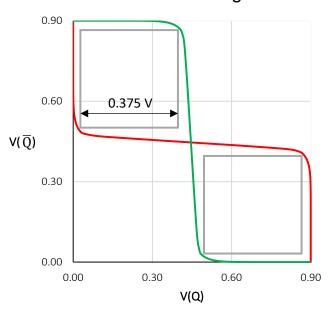

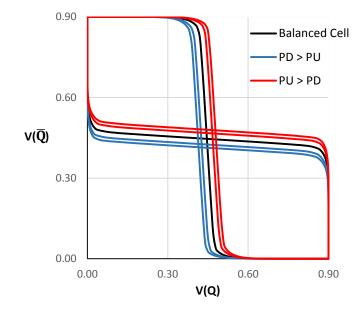

Further, FinFET technology can bring many specific advantages to SRAM memories' performance and stability. Improved sub-threshold swing allows not only lower  $V_{TH}$ for a given off-state leakage current, but also enhances the on-state current per device width. Such improvement shortens the read and write access times on FinFET SRAM cells. Furthermore, the less-relevant drain-induced barrier lowering (DIBL) effects in this technology induces to smaller output conductance  $(\partial I_D / \partial V_{DS})$  in the saturation region, leading to sharper voltage transfer characteristics, improving the read Static Noise Margin (SNM) of FinFET SRAM cells.

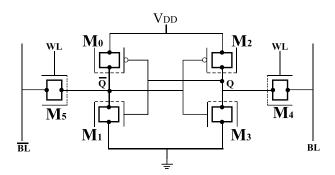

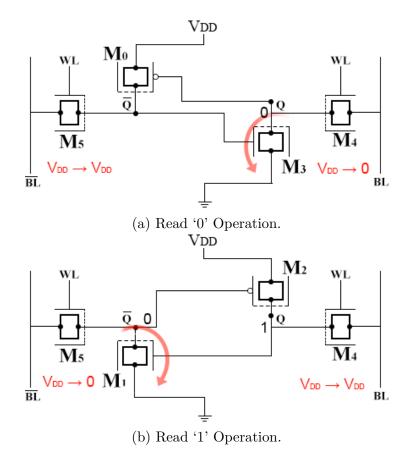

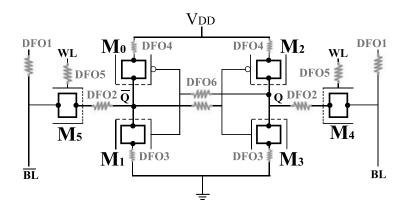

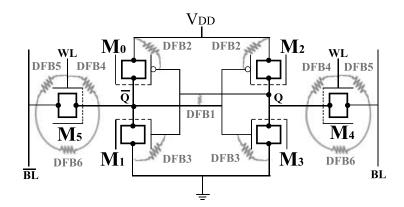

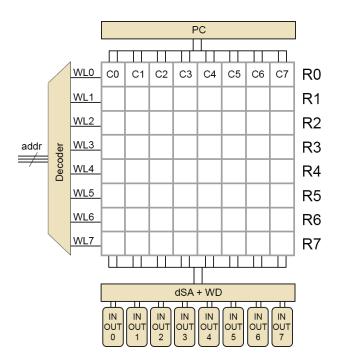

One of the most important models of SRAM cells is the design based on six transistors (6T), which is represented in Fig. 7. The 6T memory cell consists of two pass transistors that are shared between read and write operations, and four other transistors that represent two cross-coupled inverters. The word line (WL) replaces the clock and controls the transistors M5 and M6 (pass transistors) that are connected each to their respective bit line (BL). The value stored in the cell corresponds to the  $\Delta V$  between inverters (M1 & M2, M3 & M4).

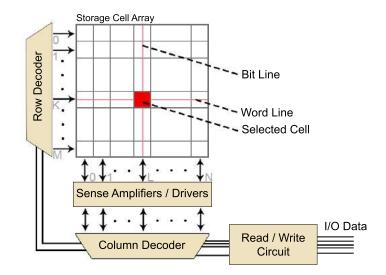

Jointly, a group of SRAM cells forms a matrix structure, allowing data storage in any combination of rows and columns. All cells share electrical connections: vertically,

Figure 8: SRAM Block consisting of (M+1)x(N+1) cells.

through the bit line, and horizontally, through the word line. Each cell has a unique position (address), so it is possible to access each one of them individually by the appropriate selection of word and bit lines.

Around the main array of SRAM cells, other circuits guarantee proper operation. There are two *address decoders*: one for the word line (rows), and the other for the bit line (columns). Another circuit is responsible for read and write operations. It can either receive a value and then work the bit lines to store it; or it can read the value already stored on the cell by estimating the  $\Delta V$  and then output the data retrieved. There are also sense amplifiers for every column; they help by amplifying the signals that are about to be written or were just read. Fig. 8 depicts an example of this architecture.

### 2.5 Defect, Fault, and Error

Models can serve as abstraction of physical events. Through them, it is possible to analyze such events and finalize solutions. In this context, three fundamental terms are used to express these events – defects, errors, and faults. Many definitions co-relate and establish a cause-effect relationship between them.

According to (BUSHNELL; AGRAWAL, 2013), *defect*, *fault*, and *error* are defined as the following:

- **Defect**: A defect in an electronic system is the unintended difference between the implemented hardware and its intended design;

- Fault: A representation of a "defect" at the abstracted function level;

Figure 9: Difference between Open Defects (MINAYA, 2014).

• Error: A wrong output signal produced by a defective system is called an error. An error is an "effect" whose cause is some "defect".

#### 2.6 Resistive Defects

The constant evolution of nanotechnology brought many revolutions to semiconductors, making it also necessary to improve the IC manufacturing process. Therefore, the use of new, complex processing steps and materials are imperative (MINAYA, 2014). Due to the sensitivity caused by the miniaturization of circuits and process variability present during manufacturing, defects introduced throughout the process can impair the chip, affecting IC reliability and causing overall yield loss.

There are many types of defects that can compromise the chip's reliability. In this context, two of them — resistive-open (RO) and resistive-bridge (RB) defects — are described in detail.

#### 2.6.1 Resistive-Open Defects

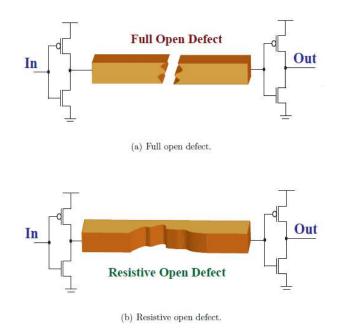

A resistive-open defect is characterized as a discrepancy in the connection between two nodes. Also known as a weak open defect, they happen during the manufacturing process and are primarily due to imperfections or inconsistency in the process. They are characterized by still maintaining connection between nodes, even though it is compromised. Contrasting the first, *full-open* (or simply *open*) defects are characterized as a disruption in the connection between two nodes. Fig. 9 depicts this difference.

Figure 10: A bridge defect connecting two independent points (MINAYA, 2014)

Concerning the standard 6T design of SRAMs, there is a total of 18 spots where resistive-open defects can occur. The position where a defect occurs directly affects which fault behavior will be observed in the cell. However, due to cell's symmetry, a set of only six defects are already enough to analyze the impact of this type of defect on the cell's performance.

#### 2.6.2 Resistive-Bridge Defects

A resistive-bridge defect creates a connection between two nodes that should have no relation. Like a resistive-open defect, its main causes are inconsistencies and imperfections in the manufacturing process. This new connection has a fixed resistance value that depends on its shape and the materials involved.

Resistive-Bridge defects detection may be not trivial. If the resistance of the new connection is sufficiently small, the circuit will be affected by a delay large enough to cause failures, which can be detected by traditional test methods. Nevertheless, if the resistance is not significantly small, the delay induced will not be large, thus causing the defect not to be detected as it will not produce a fault. This may represent an issue in IC reliability (DILILLO et al., 2005). Fig. 10 depicts a new connection in a circuit, illustrating the concept of resistive-bridge defects.

The impact of this type of defect on 6T SRAM cells depends on the location of the defect and the resistance of the new connection as well. High resistance connections usually cause weak read faults, while low resistance connections tends to cause stuck-at faults (FONSECA et al., 2010).

#### 2.7 Fault Modeling

Fault modeling is the representation of faulty behaviors and patterns in a circuit. It is of utmost importance when talking about circuit testing and test effectiveness that fault models accurately reflect the behavior of defects. The impact of those defects on the circuit must be completely understood, as they are responsible for producing the output errors in order for the fault to be detected (STROUD, 2002).

According to (HAMDIOUI et al., 2004), there are two classes of faults. The first, denominated *static faults*, are faults that can be perceived with a single operation; e. g. a single read operation in the cell would be enough to detect a fault in the output. This class was enough to represent all models of fault in old technologies.

However, with miniaturization, another class of faults emerged, denominated dynamic faults. This behavior requires a sequence of at least two operations to be sensitized; e.g., a write operation followed by a sequence of read operations. A write or read operation alone in the cell would not detect any fault; yet, after a write operation immediately followed by n read operations, a faulty behavior is detected.

Concerning memory cells affected by resistive defects, different types of defects and their spot can provoke different faults. The definitions of most faults used in this work are the following, as described by (FONSECA et al., 2010; DILILLO et al., 2005):

- Transition Fault (TF): A cell is said to have a TF when it fails to flip the value stored (0 to 1 or 1 to 0);

- **Read Destructive Fault (RDF)**: A cell is said to have an RDF when a read operation on the cell causes the value stored to flip, outputting the wrong data;

- dynamic Read Destructive Fault (dRDF): A cell is said to have a dRDF when a read operation, after *n* other successful read operations, changes the value stored, outputting the wrong data;

- Deceptive Read Destructive Fault (DRDF): A cell is said to have a DRDF when a read operation on the cell outputs the correct value, but then changes the value stored;

- dynamic Deceptive Read Destructive Fault (dDRDF): The dynamic behavior of DRDF. A cell is said to have a dDRDF when, after *n* successful read operations, the following read operation flips the value in the cell, even though the output data is correct;

- Weak Read Fault (WRF): A cell is said to have a WRF when during a read operation, the  $\Delta V$  between bit lines BL and  $\overline{BL}$  is not enough for the sense amplifier to produce the correct logic output;

- No Store Fault (NSF): A cell is said to have a NSF when it cannot retain a logical value;

- Stuck-at Fault (SAF): A cell is said to have a SAF when it is unable to store both logic values. Stuck-at 1 represents a cell that cannot store logical value '0', while Stuck-at 0 represents the opposite.

- Disturb Coupling Fault (CFds): This fault affects a group of at least two cells, and is sensitized when a read or write operation in one cell affects another cell or group of cells, forcing them to change their value stored.

- Read Disturb Coupling Fault (CFrd): This fault occurs when a read operation performed on a defect-free cell changes the data in the cell and returns the incorrect value on the output if a given value is present in a defective cell.

According to (HARUTYUNYAN; TSHAGHARYAN; ZORIAN, 2015a), Dynamic faults became even more relevant in FinFET-based devices. As technology shrinks, the probability of dynamic faults in FinFET-based devices is much higher when compared to planar-based devices, which proves the necessity of test methodologies and strategies adapted to detect this specific class of faults.

#### 2.8 Test Methodologies

Test methodologies are essential to assure the quality and functionality of manufactured circuits. Different methodologies differ from what is tested, what is monitored, and how it is monitored. This section presents three classic methodologies already adopted by the industry in planar technologies, which are essential to the proposed test methodology that will be presented and discussed in the following chapters.

#### 2.8.1 March Test

March Test is a memory-specific test methodology adopted alongside Built-In Self Test (BIST). It executes access operations algorithms aiming to sensitize functional faults for detection, assuming that by writing a value in a cell, it is expected to read the same value. March Tests are used with embedded controllers that manage the execution of operations and the reconfiguration of the memory when defective rows or columns are detected, when recuperation techniques are present (LI; TSENG; HOU, 2010).

This methodology is very useful in detecting static faults. And as the nature of the test enforces a small number of operations per cell, it becomes a great option for manufacturing test. Several algorithms have already been proposed to detect static memory faults. The algorithm proposed in (HAMDIOUI; GOOR; RODGERS, 2002), known as *March SS* and presented in Algorithm 1, became one of the most used algorithms as it executes only 22 operations per cell and claims to detect all functional faults among individual cells and linked faults (e.g. coupling faults) between maximum two cells. First, the algorithm ensures that the value '0' is written in all the memory's cells, regardless of the direction (increasing or decreasing the address of access) of execution. Then, in decreasing address order, the algorithm evaluates each cell's capabilities regarding the value '0'. The algorithm resets the address, and in the same manner evaluates the cells' capabilities to store the value '1'. The algorithm repeats these two evaluations, but now increasing the address. Finally, the algorithm read all cells, expecting to read the last value of '0' previously written.

#### Algorithm 1 March SS

For the detection of dynamic faults, other algorithms for March Test have been designed, as in (HAMDIOUI et al., 2003; HARUTUNYAN; VARDANIAN; ZORIAN, 2006). However, most of the approaches can only detect dynamic faults within a range of two operations, or need to execute a great number of operations (around 70) in each cell of the array. This way, March Test becomes a poor solution to detect dynamic faults.

#### 2.8.2 $I_{DDQ}$ Test

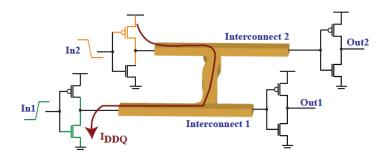

$I_{DDQ}$  Test consists of monitoring current consumption of circuits for diagnosis. Thus, it can be adopted not only in memories, but also in logic circuits. Monitoring happens during the execution of a pre-defined set of inputs, and diagnosis can be achieved through two approaches: first, by comparing the current consumption with defined thresholds; and by comparing current consumption among identical circuits when subjected to same inputs. This approach assumes that the presence of defects or faults will inevitably distort current consumption, thus allowing detection.

However, this test methodology proves to be limited when the complexity of the analysis becomes more realistic. As circuits becomes smaller, PV becomes more and more significant. This way, the distinction between current consumption discrepancies caused by weak defects and the inherent PV present on the monitored circuit becomes problematic.

#### 2.8.3 On-Chip Current Sensor associated to March Test

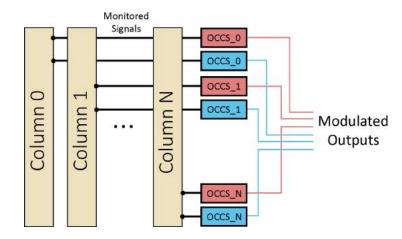

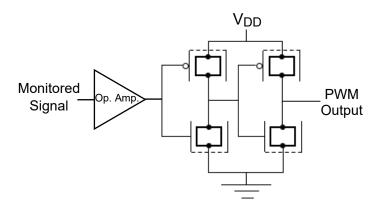

Akin to  $I_{DDQ}$  Test, it is possible to monitor current consumption by using On-Chip Current Sensors (OCCSs).

OCCS are usually composed of two parts: a current to voltage converter, and an operational amplifier. Designing an OCCS may be a difficult task, as challenges in noise

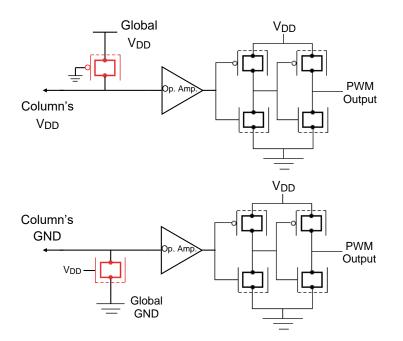

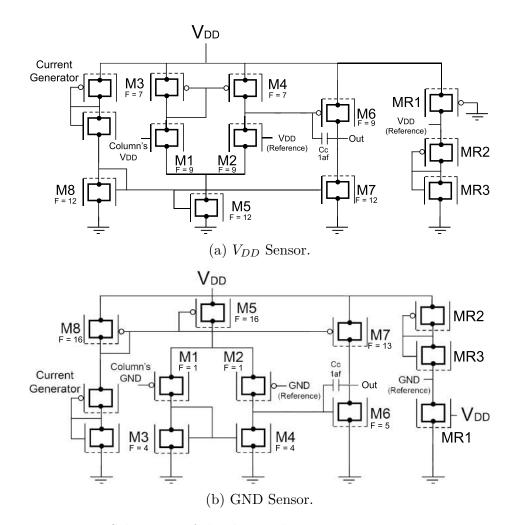

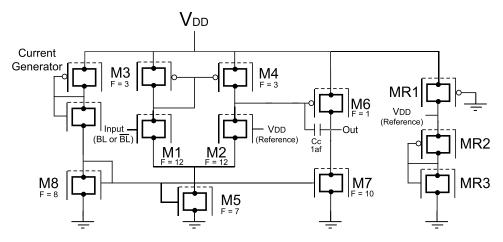

Figure 11: Architecture of the hardware-based approach proposed in (GOMEZ et al., 2016).

aggregation, delay, efficiency, area and power overhead, and PV have a direct "Short Blanket" effect on the sensor efficacy.

OCCSs have been previously adopted to detect defects in CMOS technologies. In (LAVRATTI, 2012; LAVRATTI et al., 2013; LAVRATTI et al., 2015; GOMEZ et al., 2016), the authors proposed the utilization of OCCS alongside a neighborhood comparison logic to detect resistive-open defects in 65nm CMOS technology. The overall architecture of the approach is presented in Fig. 11. The authors used OCCS to compare current consumption of memory cells while performing simultaneous read and write operations. For identical defect-free SRAM cells, the difference between the current consumption waveform should be close to zero. On the other hand, if a defect exist in one of the cells, the difference of its current consumption with respect to a defect-free cell should be different from zero. While the authors successfully proved the use of OCCSs for this matter, a great part of the study was focused on the validation of the detection technique, rather than the evaluation of the efficacy of the sensor to produce valid results.

#### 2.8.4 Challenges on Defect Detection

The challenges presented on previous sections can be enumerated as follow:

1. March Tests are not efficient regarding the detection of dynamic faults that require

more than two operations to sensitize faults;

- 2.  $I_{DDQ}$  Tests, when monitoring the entire circuit current consumption, are not able to distinguish discrepancies caused by PV and discrepancies caused by the presence of resistive defects;

- 3. Current consumption is directly affect by the defect's size, physical position in the cell's layout, operation frequency, and mode of access (read or write access). Thus, methodologies that use fixed thresholds are not a viable option to detect a wide range set of resistive defects.

Thus, proposing a test methodology, one should be aware of these aspects and introduce new techniques that are able to overcome the aforementioned challenges.

### 2.8.5 Test Methodologies for FinFETs

With the production of FinFET-based memories, there is a concern regarding embedded memory test and repair as fault models and test algorithms used for conventional memories (based on planar technology) may not be sufficient to cover all possible defects in multi-gate memories. As there may exist new faults that are specific to FinFETs, existing test solutions that rely on test operations, addressing methods, background patterns, and other stressing conditions may not be reliable tools for investigating those faults (HARUTYUNYAN et al., 2014).

In (LIU; XU, 2012) the authors first showed a study regarding three different types of defects: stuck-on, stuck-open and gate oxide short. To detect defects and faults, they proposed the utilization test vectors for delay comparison, and  $I_{DDQ}$  for current comparison. However, they concluded that these methodologies cannot be directly used, and some extra efforts and new strategies to carefully generate new delay fault vectors are necessary.

$I_{DDQ}$  test was also used on (Chen-Wei Lin; CHAO; Chih-Chieh Hsu, 2013) to investigate Gate Oxide Shorts (GOS) on FinFET-based SRAMs. The authors also emphasized the limitations of this methodology for FinFETs, and proposed two new methodologies (one for TG, another for IG) able to spot the GOS defects that were not detected by  $I_{DDQ}$ . For TG FinFETs, it is proposed the execution of a write operation while both bit lines are floating. If there is a defect on the cell, the voltage difference between bit lines decreases rapidly due to the GOS induced current, and the write operation fails. For IG FinFETs they also consider the testing of decreased saturation current, and change the voltage of one of the bit lines. This way, it is possible to detect both front-gate and back-gate GOS defects.

A fault detection strategy for stuck-open faults (SOF) was shown in (CHAMPAC et al., 2012; VAZQUEZ et al., 2009). To improve the detection of these faults, the authors

proposed a test vector strategy that aims to produce lower values at the transistor drainsource voltages of fan-out gates. This was due to the reduced hold time caused by increased sub-threshold and gate leakages in transistors with SOF, which turns detection less trivial.

In (HARUTYUNYAN et al., 2014), the authors proposed a new methodology for modeling FinFET-specific faults. Based on that, they developed an automated flow for SPICE simulations, injecting defects into memory layouts and memory SPICE netlists. The main results the authors obtained from this methodology is that FinFET-based memories, compared with planar-based memories, are prone to suffer more from dynamic faults, but less from PV.

# 3 Proposed Technique