## FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO MESTRADO EM CIÊNCIA DA COMPUTAÇÃO

MARCELO MELO LINCK

### INCREASING MEMORY ACCESS EFFICIENCY THROUGH A TWO-LEVEL MEMORY CONTROLLER

Porto Alegre

2017

### PÓS-GRADUAÇÃO - *STRICTO SENSU*

Pontifícia Universidade Católica do Rio Grande do Sul

### PONTIFICAL CATHOLIC UNIVERSITY OF RIO GRANDE DO SUL FACULTY OF INFORMATICS GRADUATE PROGRAM IN COMPUTER SCIENCE

# INCREASING MEMORY ACCESS EFFICIENCY THROUGH A TWO-LEVEL MEMORY CONTROLLER

# MARCELO MELO LINCK

Dissertation presented as partial requirement for obtaining the degree of Master in Computer Science at Pontifical Catholic University of Rio Grande do Sul.

Advisor: Prof. Dr. César Augusto Missio Marcon

L736i Linck, Marcelo Melo

Increasing Memory Access Efficiency Through a Two-Level Memory Controller / Marcelo Melo Linck . – 2017. 105 f. Dissertação (Mestrado) – Programa de Pós-Graduação em Ciência da Computação, PUCRS.

Orientador: Prof. Dr. César Augusto Missio Marcon.

1. Memory Controller. 2. DRAM. 3. Memory. 4. DDR4. I. Marcon, César Augusto Missio. II. Título.

Elaborada pelo Sistema de Geração Automática de Ficha Catalográfica da PUCRS com os dados fornecidos pelo(a) autor(a).

Marcelo Melo Linck

### INCREASING MEMORY ACCESS EFFICIENCY THROUGH A TWO-LEVEL MEMORY CONTROLLER

This Dissertation has been submitted in partial fulfillment of the requirements for the degree of Master of Computer Science, of the Graduate Program in Computer Science, School of Computer Science of the Pontifícia Universidade Católica do Rio Grande do Sul.

Sanctioned on March 22<sup>nd</sup>, 2017.

### **COMMITTEE MEMBERS:**

Prof. Dr. Alexandre de Morais Amory (PUCRS)

Prof. Dr. Debora Matos (UERGS)

Prof. Dr. César Augusto Missio Marcon (PPGCC/PUCRS - Advisor)

I dedicate this work to my beloved friend and pet Lyon. Unfortunately he is not among us anymore, but my memories of him will always be the sweetest and most beautiful ones.

"Logic will get you from A to B. Imagination will take you everywhere." (Albert Einstein)

#### ACKNOWLEDGMENTS

To my mother Marli that have always given me strength and support to go on.

To my father Gilberto that is proud of me.

To my girlfriend and best-friend Larissa that always believed in me and supported me through tough times.

To my friends Ricardo Guazzelli, Matheus Gibiluka, Ana Tramontina, Douglas Silva, Augusto Santos, Matheus Soares and Mariana Endler that provided me with the funniest and peaceful moments of my life.

To my advisor César Marcon that guided me throughout these years and had all the patience in the world to advise me.

To my friend and colleague Gabriel Paz that have significantly helped me along the course of this project.

To my colleagues Guilherme Heck and Marcelo Ruaro that always had patience and answered my questions.

To professors Fernando Moraes, Ney Calazans, Alexandre Amory and Fabiano Hessel that provided me with important knowledge for my career.

To everybody, that, directly or not, have contributed to the development of this work.

# INCREASING MEMORY ACCESS EFFICIENCY THROUGH A TWO-LEVEL MEMORY CONTROLLER

#### ABSTRACT

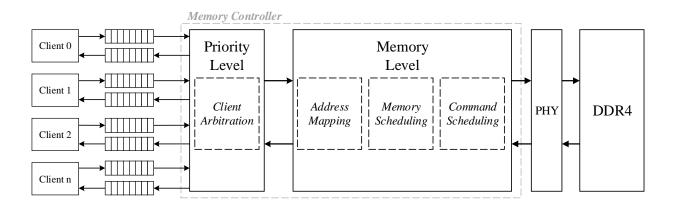

Simultaneous accesses generated by memory clients in a System-on-Chip (SoC) to a single memory device impose challenges that require extra attention due to the performance bottleneck created. When considering these clients as processors, this issue becomes more evident, because the growth rate in speed for processors exceeds the same rate for memory devices, creating a *performance gap*. In this scenario, memory-controlling strategies are necessary to improve system performances. Studies have proven that the main cause of processor execution lagging is the memory communication. Therefore, the main contribution of this work is the implementation of a memory-controlling architecture composed of two levels: priority and memory. The priority level is responsible for interfacing with clients and scheduling memory requests according to a fixed-priority algorithm. The memory level is responsible for reordering requests and guaranteeing memory access isolation to high-priority clients. The main objective of this work is to provide latency reductions to high-priority clients in a scalable system. Experiments in this work have been conducted considering the behavioral simulation of the proposed architecture through a software simulator. The evaluation of the proposed work is divided into four parts: latency evaluation, row-hit evaluation, runtime evaluation and scalability evaluation.

Keywords: Memory, Memory Controller, DRAM, DDR4.

# AUMENTANDO A EFICIÊNCIA DE ACESSO À MEMÓRIA ATRAVÉS DE UM CONTROLADOR DE MEMÓRIA DE DOIS NÍVEIS

#### **RESUMO**

Acessos simultâneos gerados por múltiplos clientes para um único dispositivo de memória em um Sistema-em-Chip (SoC) impõe desafios que requerem atenção extra devido ao gargalo gerado na performance. Considerando estes clientes como processadores, este problema torna-se mais evidente, pois a taxa de crescimento de velocidade para processadores excede a de dispositivos de memória, criando uma lacuna de desempenho. Neste cenário, estratégias de controle de memória são necessárias para aumentar o desempenho do sistema. Estudos provam que a comunicação com a memória é a maior causa de atrasos durante a execução de programas em processadores. Portanto, a maior contribuição deste trabalho é a implementação de uma arquitetura de controlador de memória composta por dois níveis: prioridade e memória. O nível de prioridade é responsável por interagir com os clientes e escalonar requisições de memória de acordo com um algoritmo de prioridade fixa. O nível de memória é responsável por reordenar as requisições e garantir o isolamento de acesso à memória para clientes de alta prioridade. O principal objetivo deste trabalho é apresentar um modelo que reduza as latências de acesso à memória para clientes de alta prioridade em um sistema altamente escalável. Os experimentos neste trabalho foram realizados através de uma simulação comportamental da estrutura proposta utilizando um programa de simulação. A análise dos resultados é dividida em quatro partes: análise de latência, análise de row-hit, análise de tempo de execução e análise de escalabilidade.

Palavras Chave: Memória, Controlador de Memória, DRAM, DDR4.

# LIST OF FIGURES

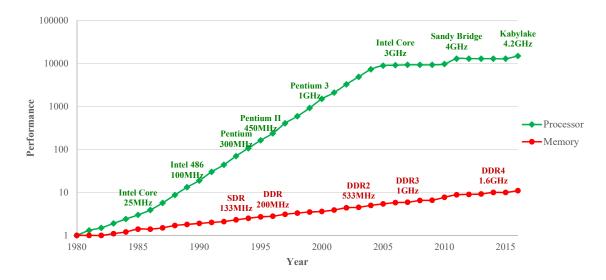

| 1.1  | Performance evolution for processors and DRAMs. The memory frequencies pre-<br>sented in the labels of this plot consider data-bus frequencies. Memory internal<br>clock frequencies are considerably smaller, therefore, explaining the <i>performance gap</i><br>[Jed16b]. Source: data extracted from [Car02][Li16][Mic16c] | 29 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

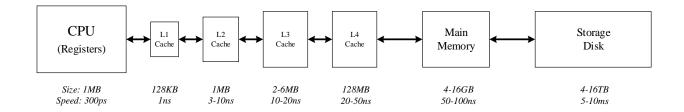

| 2.1  | Simplified diagram of the hierarchical levels that compose the memory subsystem.<br>The main memory and storage disk sizes are considered for a single device. Multiple<br>devices can be added to increase capacity. Source: adapted from [Bon14] and updated<br>with [Int17].                                                | 33 |

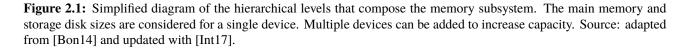

| 2.2  | Bank distribution on a DIMM. Source: created by the author.                                                                                                                                                                                                                                                                    | 36 |

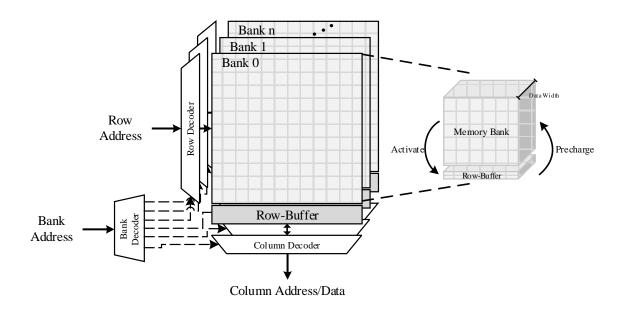

| 2.3  | Internal DRAM structure. Source: created by the author                                                                                                                                                                                                                                                                         | 37 |

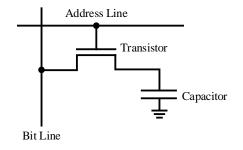

| 2.4  | Internal DRAM cell structure (1T1C). Source: created by the author.                                                                                                                                                                                                                                                            | 37 |

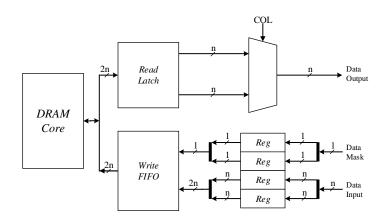

| 2.5  | Input and output of a 2n prefetch architecture. Source: created by the author                                                                                                                                                                                                                                                  | 39 |

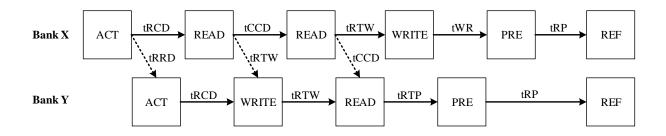

| 2.6  | Timing dependencies between commands and banks. Dashed lines indicate inter-bank dependencies. Source: created by the author.                                                                                                                                                                                                  | 42 |

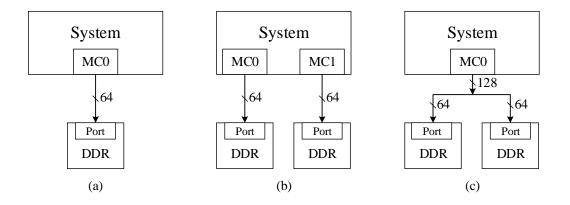

| 3.1  | System configurations: (a) Single-channel (b) Dual-channel and (c) High-bandwidth 128-bit channel. Source: adapted from [Bon14]                                                                                                                                                                                                | 43 |

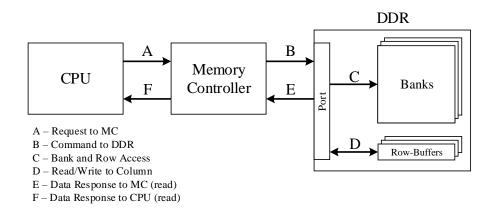

| 3.2  | Data transference steps between CPU and DDR SDRAM. Source: adapted from [Bon14]                                                                                                                                                                                                                                                | 44 |

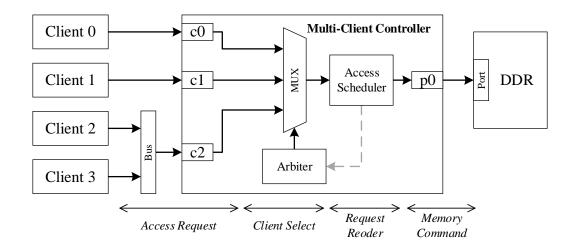

| 3.3  | Illustration of a multi-client architecture with the request steps to memory access.<br>Source: created by the author                                                                                                                                                                                                          | 45 |

| 3.4  | <i>Flat</i> address mapping. The burst index indicates the burst size. Modern SDRAM devices have 8 configured as burst size, in this case, burst index is 3. Source: created                                                                                                                                                   |    |

|      | by the author.                                                                                                                                                                                                                                                                                                                 | 46 |

| 3.5  | Page Interleaving address mapping. Source: created by the author                                                                                                                                                                                                                                                               | 46 |

| 3.6  | Bank Interleaving address mapping. Source: created by the author                                                                                                                                                                                                                                                               | 47 |

| 3.7  | Rank Interleaving address mapping. Source: created by the author                                                                                                                                                                                                                                                               | 47 |

| 3.8  | Address mapping for <i>Cache-block Interleaving</i> . Source: created by the author                                                                                                                                                                                                                                            | 47 |

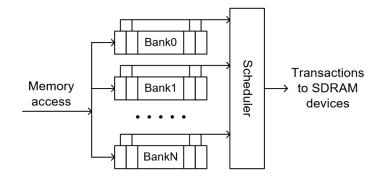

| 3.9  | FCFS (bank-in-order) scheduling mechanism. Source: extracted from [Sha06]                                                                                                                                                                                                                                                      | 48 |

| 3.10 | FR-FCFS (row-hit policy) scheduling mechanism. Source: extracted from [Sha06]                                                                                                                                                                                                                                                  | 49 |

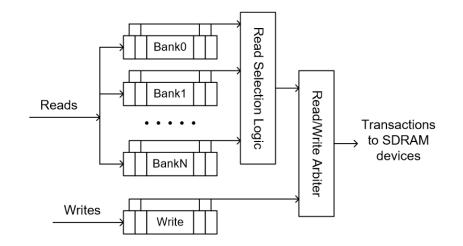

| 3.11 | Burst reordering scheduling mechanism. Source: extracted from [SD07]                                                                                                                                                                                                                                                           | 49 |

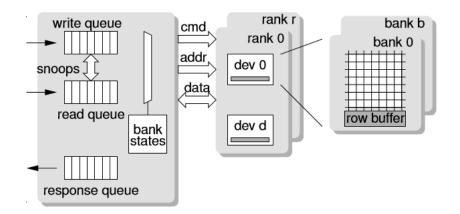

| 3.12 | Hansson's read over write scheduling mechanism. Source: extracted from $[H^+14]$                                                                                                                                                                                                                                               | 50 |

| 3.13 | Intel out of order scheduling structure. Source: extracted from [Sha06]                                                                                                                                                                                                                                                        | 51 |

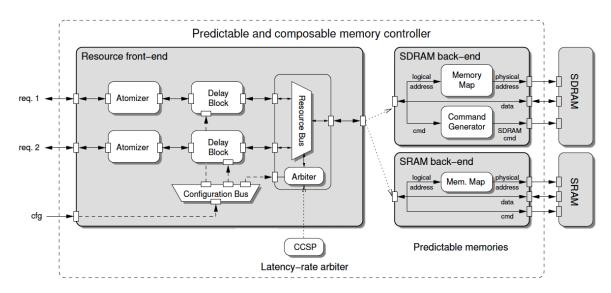

| 3.14 | Predictable and composable memory controller divided into front-end and back-end parts. Source: extracted from [AG11].                                                                                                                                                                                                         | 53 |

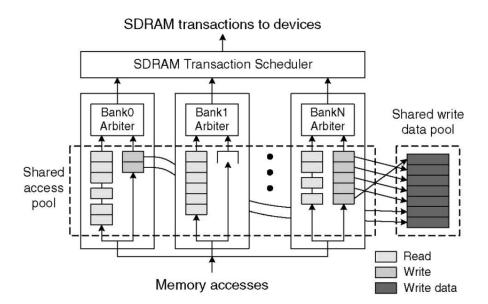

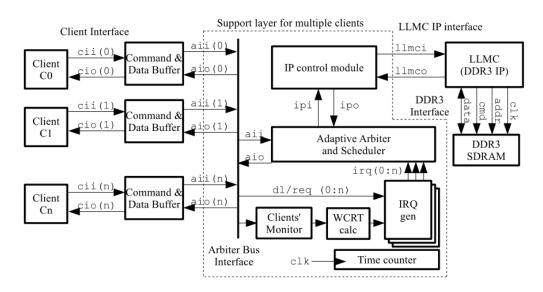

| 3.15  | Block diagram of Bonatto's adaptive memory controller. Source: extracted from [BNP+14].                                                                                                                                                                                                                                                                                                         | 55 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

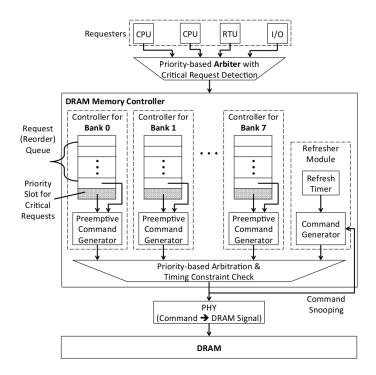

| 3.16  | Structure of the priority-based controller proposed by H. Kim et al. (2015). Source: extracted from [K <sup>+</sup> 15]                                                                                                                                                                                                                                                                         | 58 |

| 4.1   | Proposed structure of the two-level memory controller: Priority Level and Memory<br>Level. Source: created by the author.                                                                                                                                                                                                                                                                       | 61 |

| 4.2   | Proposed address mapping technique. Source: created by the author                                                                                                                                                                                                                                                                                                                               | 63 |

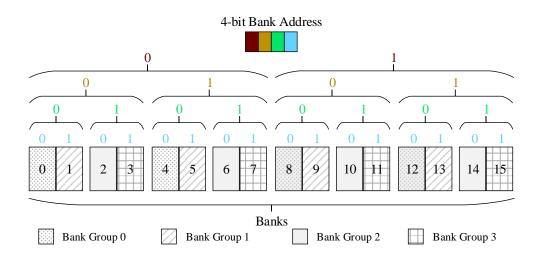

| 4.3   | Mapping position of a 16-bank DDR4 in a 4-bit register considering four bank-groups interleaved. Source: created by the author.                                                                                                                                                                                                                                                                 | 64 |

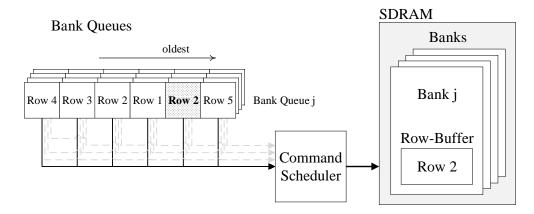

| 4.4   | Request scheduling using the FR-FCFS algorithm. The scheduled request presents a pattern background. Source: created by the author.                                                                                                                                                                                                                                                             | 65 |

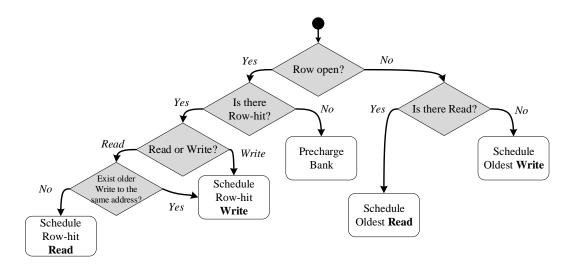

| 4.5   | Request scheduling diagram for low-priority clients.                                                                                                                                                                                                                                                                                                                                            | 66 |

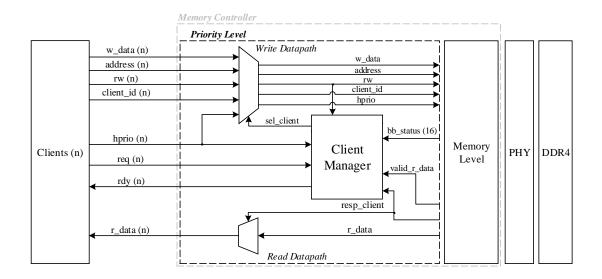

| 4.6   | Block diagram of the <i>priority level</i> . The client manager implements the priority algorithm, the <i>n</i> clients are connected in parallel, and the write and read datapaths transfer data from e to clients, respectively. Source: created by the author                                                                                                                                | 68 |

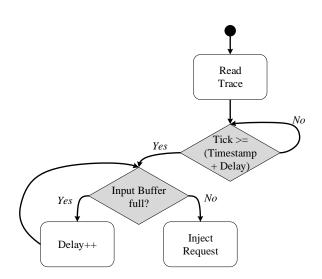

| 4.7   | Diagram for the trace input logic. Source: created by the author                                                                                                                                                                                                                                                                                                                                | 69 |

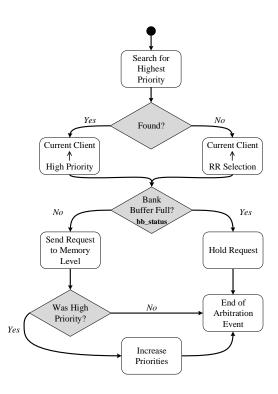

| 4.8   | Client manager logic represented as a flow-chart. Source: created by the author                                                                                                                                                                                                                                                                                                                 | 70 |

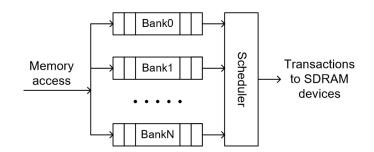

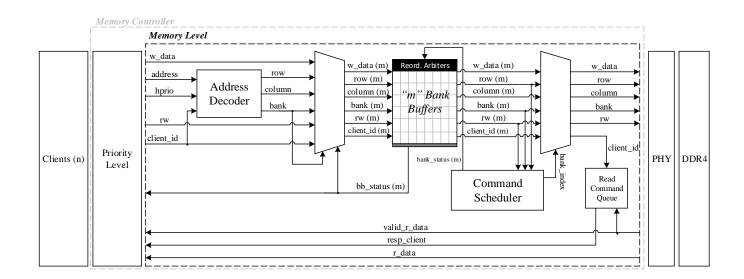

| 4.9   | Block diagram of the <i>memory level</i> . The address decoder holds the mapping table<br>and implements the bank privatization technique. The bank buffers store the memory<br>requests and the reordering arbiters schedule requests using the proposed reordering<br>algorithm. The command scheduler schedule commands considering bank-group<br>constraints. Source: created by the author | 71 |

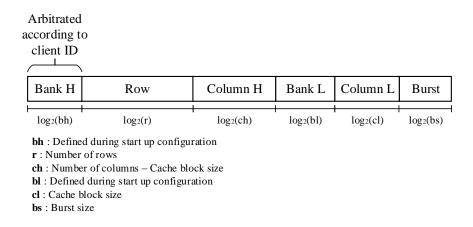

| 4.10  | Proposed address mapping scheme considering a single channel and a single rank.<br>The size in bits of each field is calculated through $log_2(x)$ , being <i>x</i> a variable dependent<br>on controller configurations or memory module characteristics. Source: created by<br>the author.                                                                                                    | 72 |

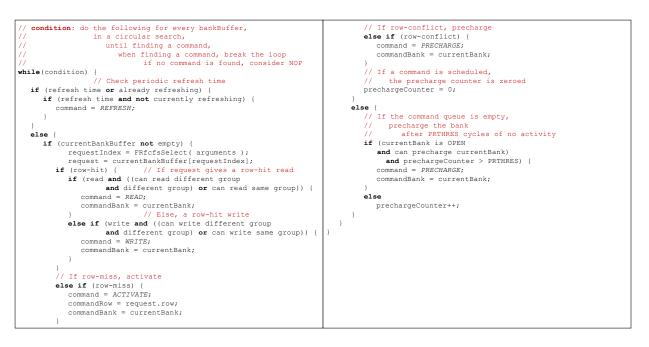

| 4 1 1 | Pseudo-code for the reordering arbiter with FR-FCFS and read/write reordering algo-                                                                                                                                                                                                                                                                                                             |    |

|       | rithms. Source: created by the author.                                                                                                                                                                                                                                                                                                                                                          | 73 |

| 4.12  | Pseudo-code for the command scheduling logic. Source: created by the author                                                                                                                                                                                                                                                                                                                     | 74 |

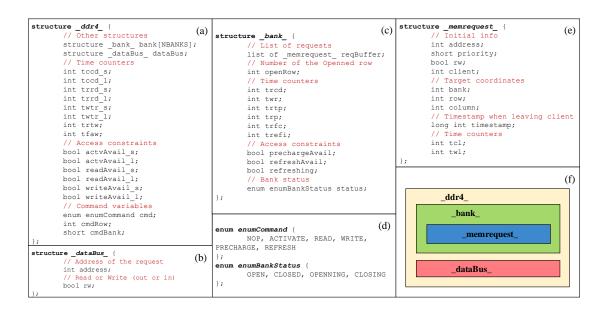

| 4.13  | Data structures used in the memory simulator: (a) Top memory structure; (b) Data structure; (c) Bank structure; (d) Enumeration of custom variables; (e) Request structure; and (f) Relationship between structures. Source: created by the author                                                                                                                                              | 75 |

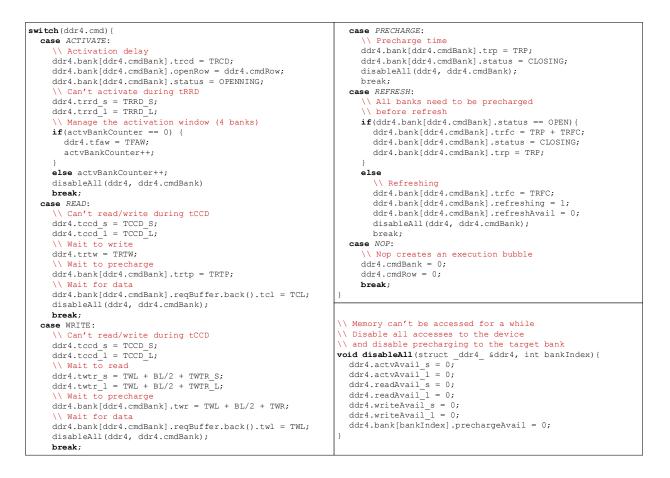

| 4.14  | Pseudo-code for the command decoding logic. Source: created by the author                                                                                                                                                                                                                                                                                                                       | 77 |

| 4.15  | Pseudo-code for the timing control logic. Source: created by the author                                                                                                                                                                                                                                                                                                                         | 78 |

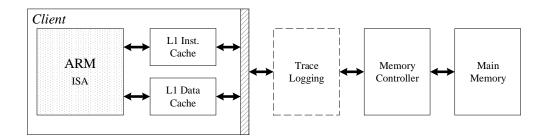

| 5.1   | System architecture as created by Gem5. The dashed outline box represents the trace extraction module. Source: created by the author.                                                                                                                                                                                                                                                           | 84 |

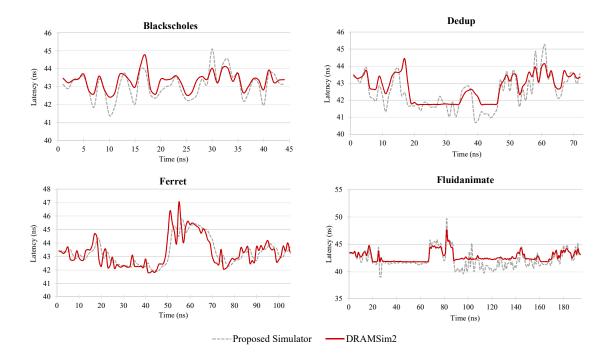

| 5.2 | Memory access latency comparison between the proposed simulator (red) and the           |    |

|-----|-----------------------------------------------------------------------------------------|----|

|     | DRAMSim2 (dashed-grey). Source: created by the author.                                  | 87 |

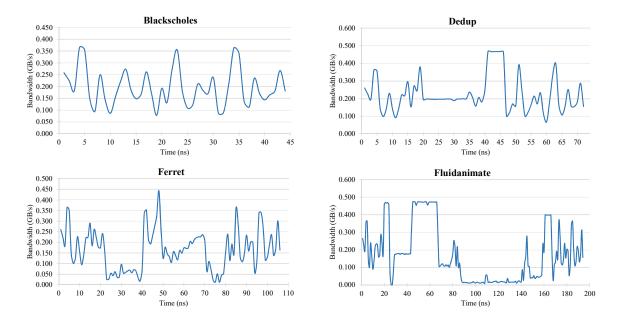

| 5.3 | Memory bandwidth available for each application. Simulations with the proposed          |    |

|     | simulator and DRAMSim2 presented the same results. Source: created by the author        | 88 |

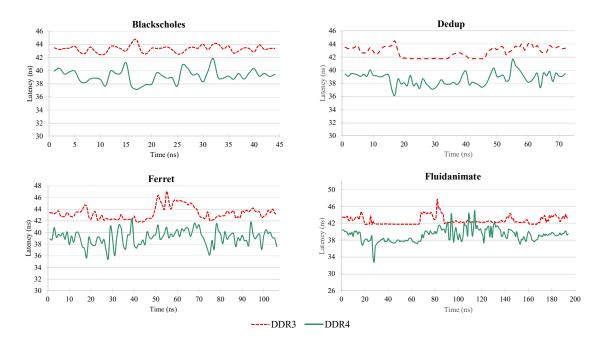

| 5.4 | Latency comparison between DDR3-1333 and DDR4-2400 using 1.5GHz processors              |    |

|     | and the proposed simulator. Source: created by the author                               | 89 |

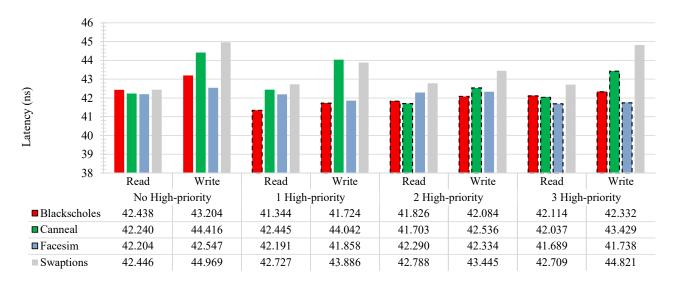

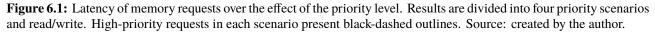

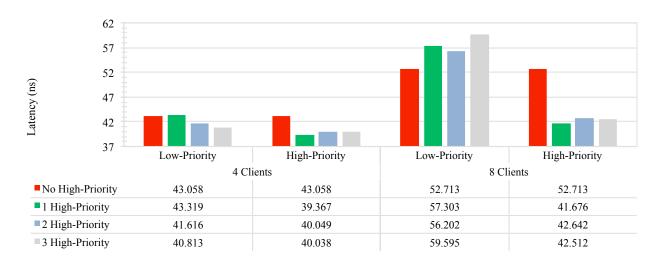

| 6.1 | Latency of memory requests over the effect of the priority level. Results are divided   |    |

|     | into four priority scenarios and read/write. High-priority requests in each scenario    |    |

|     | present black-dashed outlines. Source: created by the author                            | 92 |

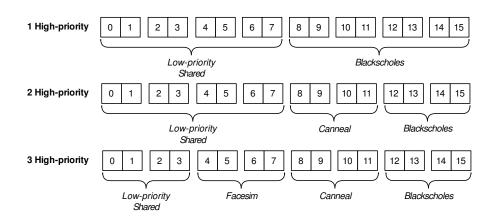

| 6.2 | Bank division for high and low-priority clients in each priority scenario. Source:      |    |

|     | created by the author                                                                   | 94 |

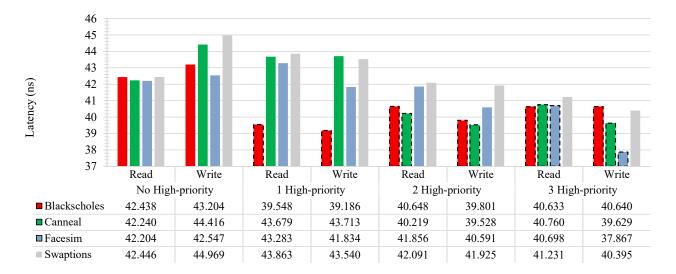

| 6.3 | Latency of memory requests over the effect of the two levels of the memory controller.  |    |

|     | Results are divided into four priority scenarios and read/write. High-priority requests |    |

|     | in each scenario present black-dashed bar outlines. Source: created by the author       | 95 |

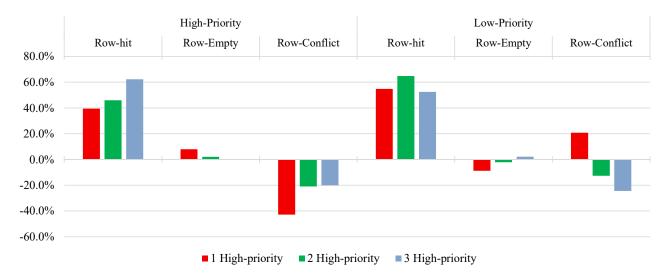

| 6.4 | Row-hit, row-empty and row-conflict variations for the priority scenarios discussed.    |    |

|     | Source: created by the author                                                           | 96 |

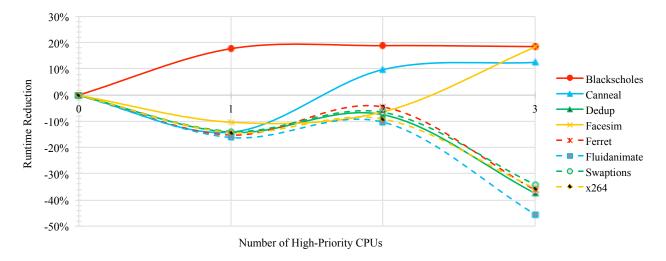

| 6.5 | Runtime reduction percentage for each client. Source: created by the author             | 97 |

| 6.6 | Comparison of the average latency for 4 and 8 clients, which are divided into two       |    |

|     | groups: low and high-priority. Source: created by the author.                           | 98 |

| 6.7 | Runtime reduction percentage for each client on a system with eight inputs. Source:     |    |

|     | created by the author.                                                                  | 99 |

# LIST OF TABLES

| 2.1 | Evolution of DDR SDRAM devices. Source: DDR devices [Mic16c], LPDDR devices                                                                                                         |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | [Mic12][Jed16a] and GDDR devices [Mic12][Nvi16].                                                                                                                                    | 35 |

| 2.2 | Summary of DDR SDRAM time parameters. Source: created by the author                                                                                                                 | 42 |

| 3.1 | Important topics brought from each work presented in this section. Included, a comparison with the memory controller proposed in the next chapter. Source: created by the author.   | 59 |

| 4.1 | Client arbitration representing a system with four clients. Clients 1 and 3 are high-<br>priority, while clients 0 and 2 are low-priority. Tx represents time-slots, and red-bolded |    |

|     | numbers represent selected requests by the arbitration. Source: created by the author                                                                                               | 62 |

| 4.2 | Sample of the trace format. Source: created by the author                                                                                                                           | 68 |

| 5.1 | Summary of PARSEC application characteristics. Source: adapted from [BKSL08]                                                                                                        | 80 |

| 5.2 | Simulation parameters used for the Gem5 simulation for trace extraction. Source: created by the author.                                                                             | 84 |

| 5.3 | Traced applications characteristics for memory access. Source: created by the author.                                                                                               | 85 |

| 5.4 | Available SDRAM simulators. Source: created by the author                                                                                                                           | 86 |

| 5.5 | Simulation parameters used for the proposed simulator and DRAMSim2. Source: created by the author.                                                                                  | 86 |

| 5.6 | DDR3-1333 parameters and timing constraints measured in cycles. Source: data extracted from [Mic16b].                                                                               | 87 |

| 5.7 | Latency variation between the proposed simulator and DRAMSim2 for blackscholes,                                                                                                     |    |

|     | dedup, ferret and fluidanimate applications. Source: created by the author                                                                                                          | 88 |

| 5.8 | DDR4-2400 parameters and timing constraints measured in cycles. Source: data extracted from [Sam16]                                                                                 | 89 |

| 6.1 | Simulation parameters considered for the priority level evaluation. Source: created by the author.                                                                                  | 92 |

| 6.2 | Update of the memory controller parameters considered for the memory level evalua-<br>tion. Source: created by the author.                                                          | 93 |

| 6.3 | Update of the simulation parameters considered for the scalability evaluation. Applications with * indicate that can present higher priority depending on the priority              |    |

|     | scenario. Source: created by the author                                                                                                                                             | 98 |

### LIST OF ACRONYMS

- IoT Internet of Things

- MPSoC Multiprocessor System-on-Chip

- MC Memory Controller

- VLSI Very Large Scale Integration

- RTL Register-Transfer Level

- DDR Double-Data Rate

- SRAM Static Random Access Memory

- DRAM Dynamic Random Access Memory

- eDRAM Embedded Dynamic Random Access Memory

- JEDEC Joint Electron Device Engineering Council

- SDRAM Static Dynamic Random Access Memory

- CRC Cyclic Redundancy Check

- DBI Data-Bus Inversion

- LPDDR Low-Power Double-Data Rate

- GPU Graphic Processing Units

- GDDR Graphics Double-Data Rate

- CoWoS Chip-on-Wafer-on-Substrate

- TSV Through Silicon Vias

- HMC Hybrid Memory Cube

- HBM High-Bandwidth Memory

- DIMM Dual In-line Memory Module

- SIMM Single In-line Memory Module

- 1T1C One Transistor One Capacitor

- BL Burst-Length

- tRCD Row to Column Delay

- tRAS Row Access Strobe

- tRRD Row- to- Row Delay

- tFAW Four-Bank Activation Window

- tCAS Column Access Strobe

- tCL Column Latency

- tBURST Burst Time

- tCCD Column-to-Column Delay

- tRTP Read to Precharge

- tWL Write Latency

- tWR Write Recovery

- tRP-Row Precharge

- tRC Row Cycle time

- tRFC Refresh Cycle

- tREFI Refresh Interval

- FGR Fine-Granularity Refresh

- tRTW Read to Write time

- tWTR Write to Read time

- $^{*}S-Small$

- \*\_L Large

- CPU Central Processing Unit

- NoC Network-on-Chip

- FCFS First Come First Served

- FR-FCFS First-Ready First Come First Served

- WCRT Worst-Case Response Time

- PE Processing Element

- MAG Memory access group

- SA Simulated Annealing

- PARSEC Princeton Application Repository for Shared-Memory Computers

- ISCA International Symposium on Computer Architecture

- ISA Instruction Set Architectures

- TLM Transactional Level Modeling

- SE System-Call Emulation

- FS Full-System

- O3 Out-Of-Order

- RISC Reduced Instruction Set Computer

- MAR Memory Access Rate

# CONTENTS

| 1     | INTRODUCTION                            | 27 |

|-------|-----------------------------------------|----|

| 1.1   | COMPUTER SYSTEM'S PROJECT               | 28 |

| 1.1.1 | ABSTRACTION LEVELS                      | 28 |

| 1.2   | PROCESSOR-MEMORY PERFORMANCE GAP        | 29 |

| 1.3   | MOTIVATION                              | 30 |

| 1.4   | OBJECTIVES                              | 30 |

| 1.5   | CONTRIBUTION AND INNOVATION             | 31 |

| 1.6   | DOCUMENT STRUCTURE                      | 31 |

| 2     | MEMORY SUBSYSTEM                        | 33 |

| 2.1   | DRAM                                    | 34 |

| 2.1.1 | DRAM EVOLUTION                          | 34 |

| 2.1.2 | DRAM DEVICE                             | 36 |

| 2.1.3 | DRAM DATA-BUS TECHNOLOGY                | 38 |

| 2.1.4 | DRAM ACCESS                             | 39 |

| 3     | MEMORY CONTROLLERS                      | 43 |

| 3.1   | CLASSIC MEMORY CONTROLLER               | 43 |

| 3.2   | MULTI-CLIENT CONTROLLER                 | 44 |

| 3.2.1 | ADDRESS MAPPING                         | 45 |

| 3.2.2 | MEMORY ACCESS REORDERING                | 48 |

| 3.3   | COMMAND SCHEDULING                      | 51 |

| 3.3.1 | OLDEST-ACROSS-BANKS-FIRST               | 51 |

| 3.3.2 | ROUND-ROBIN BETWEEN BANKS               | 52 |

| 3.3.3 | FIXED PRIORITY                          | 52 |

| 3.4   | RELATED WORK                            | 52 |

| 3.4.1 | STATIC MEMORY CONTROLLERS               | 52 |

| 3.4.2 | DYNAMIC MEMORY CONTROLLERS              | 55 |

| 3.4.3 | SUMMARY                                 | 58 |

| 4     | PROJECT METHODOLOGY                     | 61 |

| 4.1   | CLIENT ARBITRATION                      | 61 |

| 4.2   | ADDRESS MAPPING WITH BANK PRIVATIZATION | 63 |

| REFERENCES                                     | 103                                            |

|------------------------------------------------|------------------------------------------------|

| CONCLUSION AND FUTURE WORK                     | 101                                            |

| RUNTIME EVALUATION                             | 99                                             |

| LATENCY EVALUATION                             | 98                                             |

| SCALABILITY EVALUATION                         | 97                                             |

| RUNTIME EVALUATION                             | 96                                             |

| ROW-HIT, ROW-CONFLICT AND ROW-EMPTY EVALUATION | 95                                             |

| LATENCY EVALUATION                             | 94                                             |

| MEMORY LEVEL EVALUATION                        | 93                                             |

| LATENCY EVALUATION                             | 92                                             |

| PRIORITY LEVEL EVALUATION                      | 91                                             |

| EXPERIMENTS AND RESULTS                        | 91                                             |

| DDR4 SIMULATOR                                 | 88                                             |

|                                                |                                                |

|                                                |                                                |

|                                                |                                                |

|                                                |                                                |

|                                                |                                                |

|                                                |                                                |

| SIMULATION ENVIRONMENT                         | 79                                             |

| DDR4 SIMULATOR                                 | 74                                             |

|                                                |                                                |

|                                                |                                                |

|                                                |                                                |

|                                                |                                                |

| READ/WRITE BURST REORDERING                    | 65                                             |

| FR-FCFS                                        | 65                                             |

| MEMORY-SCHEDULING ALGORITHM                    | 64                                             |

|                                                | ROW-HIT, ROW-CONFLICT AND ROW-EMPTY EVALUATION |

### **1. INTRODUCTION**

In the last decades, technology has presented to the society an enormous amount of sophisticated devices that integrate and bring comfort to people's lives. Computers have significantly reduced in size and improved in speed, turning into portable devices, and facilitating its use on a daily-basis, incorporating as personal objects, both for work and recreation. At the same time, large servers store a significant amount of information available to users through a single click. Modern society is surrounded by computers, equipments that stopped being simple calculating machines to turn into essential everyday elements. They have turned into faster and more accessible devices, steadily reducing in size and energy consumption. This evolution is accompanied by a crescent innovation, guided by consumers that demand even more versatile products.

Digital communication started transferring data, voice, and image, evolving high-speed connection networks for both desktops and mobile. Computational systems in this era are ubiquitous and participate in daily tasks. These systems are present in domestic, industrial and service equipments, being smart cars, smartphones or even smart cities. They generate numerous interconnected devices that create the Internet of Things (IoT) [AD11]. Each modern device presents multiple cores, memory levels and I/O interfaces that connect each other through a communication architecture and compose a Multiprocessor System-on-Chip (MPSoC).

The extensive connectivity created by significant amounts of exchanged information between digital devices leads to a considerable volume of data constantly being stored and accessed. The storage subsystem of computer systems is composed of a memory hierarchy that comprises multiple levels of memory devices that cooperate with the core processors to achieve desirable performances. This memory subsystem also requires accesses to external memory devices that implement higher storage capacities, but lower response speeds. The interface between such hierarchy levels requires a complex controlling architecture called *Memory Controllers* (MC).

The exploration of various approaches of memory controller architectures requires multiple studies that range from behavioral models to low-level hardware implementations. They need to take into account various limitations of the current project design methods and memory technologies. This master's dissertation aims to present a two-leveled memory controller model capable of improving the performance of particular applications in a multi-processed system based on predefined priorities. The solution presented in this work implements state-of-the-art memory access scheduling algorithms in coordination with bank prioritization techniques. The following sections describe the challenges for the implementation of complex hardware designs and the abstraction levels related to it. Besides, it presents the performance gap that exists between processors and memories, and in the end, it presents the motivation, objectives, and contributions aimed at this work.

#### 1.1 Computer System's Project

The VLSI<sup>1</sup> project is a crescent challenge. As foreseen by G. Moore in 1965, the complexity of integrated systems doubles every two years [Moo06], due to the increase in transistor size in a single chip. This exponential growth in the number of transistors, which is possible by their reduction in size, creates an increase in complexity during circuit integration. The complexity improvement is reached with the advancement of tools and techniques used during project development. Although, the growth in size and speed of transistors do not directly imply in improvement of the system computational capacity.

The difference between the existent number of transistors theoretically available in a chip and the capacity of using them is known to be the *productivity gap*, as presented by Bonatto [Bon14]. Researchers point out that the difference in productivity will only be surpassed if the project methodology were modified. Currently, high-complex circuits are still projected through low-level hardware descriptions, like Register-Transfer Level (RTL) and state machines. Some alternatives to reduce this productivity gap is the implementation of higher-level description methods and the accession of a *system-level design* [Pim16].

According to Keating [Kea11], we are currently in the third VLSI project revolution, characterized by the behavioral analysis of complex applications using high-level hardware and software representations combined. The computer system comprises hardware and software layers that are implemented and validated in various abstraction levels.

### 1.1.1 Abstraction levels

The automation of the VLSI project design is presented as the main solution to reduce the productivity gap. Although, this process requires a simplified presentation of the hardware modules, allowing the description of more complex systems. These automation steps require the use of different abstraction and description levels. As proposed by Suzim [Suz81], the MPSoC description levels create a project flow that starts from a high-level implementation up to the layout of the transistor. Each level comprises the implementation of an algorithm in a hardware or software language.

In many studies, such as [AG11][RLP<sup>+</sup>11][SKKD12], the authors prefer to describe their work in a high-level abstraction language and use hardware simulators implemented as software to study the behavior of their architectures. Such simulators present an advantage over the hardware descriptions for providing a simpler way to represent complex systems with significant lower implementation efforts. These can be considered high-level hardware representations or software programs that simulate the behavior of a certain system; languages like SystemC and/or C++ are commonly used to represent such levels.

<sup>&</sup>lt;sup>1</sup>Stands for Very Large Scale Integration.

#### **1.2 Processor-Memory Performance Gap**

The speed of microprocessors outgrows the speed of memories and data-storing disks, which infers in a *performance gap* created by the latency of data accesses. The chart illustrated in Figure 1.1 presents a comparison between the performance evolution of processors and memories. The image presents examples of desktop processors and SDRAM memory modules released in the past three decades. The performance discrepancy between both technologies is notable, and this variation negatively affects the system efficiency. Despite presenting high bus frequencies, modern Double-Data Rate (DDR) memories still internally operate at lower rates; therefore, several idle clock cycles are necessary between consecutive load or store operations. For example, considering an access of a 3GHz processor to a DDR4-2400 memory that internally operates at 300MHz [Jed16b]. For each single memory access, the processor would use 1 clock for accessing the memory, and would need to stay 10 clock cycles in idle waiting for the response. This difference in performance represents a significant cost to pay.

**Figure 1.1:** Performance evolution for processors and DRAMs. The memory frequencies presented in the labels of this plot consider data-bus frequencies. Memory internal clock frequencies are considerably smaller, therefore, explaining the *performance gap* [Jed16b]. Source: data extracted from [Car02][Li16][Mic16c].

Modern SDRAM devices implement burst techniques and high-bandwidth data-bus connections to compensate for internal low-frequency operations. The independent bank organization of DDR memories allows the parallelization of accesses and the increase of bandwidth. *Cache* memories are used between the processor and the main memory, attempting to improve computational efficiency. In addition, with the introduction of parallel programming, multi-task computer systems can execute multiple tasks simultaneously, reaching a significant computational gain without modifying the target architecture [BNP<sup>+</sup>14].

The implementation of embedded memory controllers allows the exploration of many hardware architectures to improve memory accesses and/or guarantee time requirements. These

MCs implement complex circuitry that comprises multiple request-handling techniques to improve processor-memory communication.

### 1.3 Motivation

According to Shao [Sha06], memory accesses are the main cause of execution lagging for processors. High memory access latencies create unnecessary instruction stalls and severely degrade the performance of applications. Multi-task computer systems that share one or more memory devices face a common issue. According to Moscibroda and Mutlu [MM07], the competition for memory access by multiple clients diminishes application performances and increase overall latencies. The main reason for this behavior is the scheduling of multiple requests to distant memory addresses, requiring a stressful set of memory operations that present latency escalation.

The study conducted by Reineke et al. [RLP<sup>+</sup>11] has proven that the memory device, contrary to most works, can be seen as a multi-resource system that can be shared by multiple applications without needing to face bank interferences. This characteristic creates a memory controlling system that provides client access isolation and relies directly on the behavior of the application. The distribution of the memory device into resources presents restrictions and scalability limitations, which are imposed by device characteristics, such as the number of banks. Therefore, a client arbitration technique may be required to create a higher level scheduling system.

### 1.4 Objectives

The main purpose of this master's dissertation is the proposal of a two-level memory controller model that reduces memory access latencies by guaranteeing bank access isolation for predefined clients. To help on the achievement of this goal, this project focuses on the accomplishment of the following items:

- To compile a solid and objective document about state-of-the-art DRAM technologies and memory controllers.

- To implement a front-end arbitration algorithm that divides clients into priority levels.

- To implement a back-end scheduling technique that guarantees memory isolation to predefined clients.

- To propose a scheduling technique to support modern DDR4 technologies.

- To evaluate controlling levels and guarantee latency reductions.

- To evaluate system scalability.

#### **1.5** Contribution and Innovation

The main contribution of this work is the implementation of a memory controller that allows performance improvements of clients based on priorities predefined by higher levels (i.e., kernel). The client selection is performed through a fixed-priority arbitration, implemented in coordination with a starvation-aware module. Aiming to ensure high performances throughout lower memory access latencies, the proposed memory controller implements a bank privatization technique that allows high-priority clients to acquire exclusive access to a determined number of memory banks, increasing row-hits and diminishing row-conflicts.

The major innovation of this work is the utilization of the proposed memory controller alongside the emerging DDR4 SDRAM. Few works in the literature focus on using this memory technology, mainly because it presents significant architectural changes when compared to its predecessors, i.e., DDR3 SDRAM. These changes introduce additional time restrictions that increase the complexity of memory controllers and require more sophisticated access algorithms.

The implementation of a memory controller that ensures low latencies for high-performance clients can be used in coordination with a scheduling subsystem that implements priority levels on a kernel. General-purpose systems normally do not implement such priority levels on hardware; therefore, establishing a reliable connection between both layers may lead to the exploration of high-performance architectures.

### **1.6 Document Structure**

This work is organized as follows. Chapter 2 presents the main concepts of memory subsystems, memory hierarchies and a detailed description about the state-of-the-art DRAM technologies and functionalities. Chapter 3 introduces memory controller techniques available in the literature and discusses related works. Chapter 4 presents the arbitration techniques used in the proposed memory controller and discusses the implementation methods. Chapter 5 presents the simulation environment used for the evaluation of the memory controller, including the benchmark selection and simulator validation. Chapter 6 evaluates the results of the proposed architecture under many simulation scenarios. Finally, Chapter 7 presents the conclusions and directions for future works.

### 2. MEMORY SUBSYSTEM

The memory is one of the essential elements for the proper functionality of a computer system. The memory hierarchy is a fundamental part of an MPSoC project, and allows the exploration of high-performance circuits. Conveniently, this hierarchy is designed considering the following structure: *cache* (SRAM<sup>1</sup> or eDRAM<sup>2</sup>), *main memory* (DRAM) and disk. Despite being the most used hierarchy in computer projects, it still does not follow the evolution of processors.

Computational systems are migrating to complex platforms with a considerable amount of processing elements. An MPSoC comprises multiple separate subsystems that interact with each other through predefined communication protocols, and use a memory hierarchy to manage the information. An efficient memory subsystem must consider access competition, data buffering, scheduling algorithms, access granularity, and scalability when integrating different kinds of memory technologies [BNP<sup>+</sup>14]. There are three kinds of CMOS memories: SRAM, DRAM and Flash. These technologies are fabricated through different processes and present different characteristics. Therefore, they present different aspects of volatility, speed, area, power consumption and other costs. The main reason to create a memory hierarchy is the *locality reference* [Bon14], meaning that it allows the storage of the same data in different memory levels with different capacities and access latencies.

Considering the crescent complexity of modern systems, VLSI projects need to be divided into isolated subsystem projects. Therefore, it is possible to define a *memory subsystem* that comprises a memory hierarchy. Although, the memory subsystem is not solely composed of different memory modules, it requires the implementation of mechanisms that support protocol conversions and multiple clock domains. The memory subsystem consists of a set of on-chip and off-chip memories, distributed along the system elements as local or shared devices. Figure 2.1 depicts a simplified diagram of a modern memory subsystem with four cache levels, main memory and storage disk.

The memory subsystem is defined as the set of heterogeneous elements that creates a redundant data-storage structure [Bon14]. The memory closer to the core is more frequently accessed, requiring to present lower area and higher speeds. The memory further from the core presents higher

<sup>&</sup>lt;sup>1</sup>SRAM stands for Static Random Access Memory

<sup>&</sup>lt;sup>2</sup>eDRAM stands for embedded DRAM, a closer-to-core SDRAM structure currently used by the new generation of Intel processors (Haswell) [Int17].

capacity, but it is slower, presenting lower access rates during the system execution. Between these two memory types there can be other hierarchy levels, projected to supply the needs of the target system.

### 2.1 DRAM

This section introduces the key features and functionalities of the DRAM technology, presenting the basic concepts and internal structure.

### 2.1.1 DRAM Evolution

The Dynamic Random Access Memory (DRAM) have been continuously evolving in the past decade, creating a series of generations that present a meaningful improvement in storage capacity and data-bus speeds. Its first appearance was in 1965 when it was patented by Dennard [Com16]. Years later, in 1993, the Joint Electron Device Engineering Council (JEDEC) introduced a new specification of the memory including a clock sign. From this moment on, it was known as the Synchronous DRAM (SDRAM). Until today, the JEDEC is responsible for creating the specification of new memory technologies arising from the research industry.

In 1996, it was presented the first Double-Data Rate (DDR) device, using both rising and falling edges of the clock signal to transfer data. This technology introduced the data prefetch architecture that allowed the load of consecutive data positions in a burst manner. For this model, the prefetch buffer size is 2n, meaning that one access returned two data-words [Mic16a]. The following DDR specifications were DDR2 (2003) and DDR3 (2007), implementing the prefetch 4n and 8n, respectively.

Later in 2012, JEDEC announced the DDR4 specification, presenting high-bandwidth bus and high data transfer rates. While the DDR3 can achieve data transfers between 800 to 2400 megatransfers per second (MT/s), DDR4 modules allow transfers ranging from 1600 to 3200 MT/s [Jed16b]. Past DDR modules presented up to eight banks, while the DDR4 introduces the 16-bank architecture with bank-groups. The bank-group technique allows DDR4 memories to access banks physically located far from each other, in a parallel manner, without any noise interference. It compensates for the prefetch technique that is maintained as 8n, like DDR3. Other important changes on the DDR4 generation are the supply voltage reduction<sup>3</sup>, command-address parity, Cyclic Redundancy Check (CRC), Data-Bus Inversion (DBI), new refresh modes, temperature awareness, and more [S<sup>+</sup>13].

The semiconductor manufacturers Hynix, Micron and Samsung were the first to start production of DDR4 devices. Samsung announced the fabrication of 4Gb DDR4 devices with 1.2V in August 2013, using 20nm technology. Micron started the fabrication of 4Gb and 8Gb DDR4 1.2V

<sup>&</sup>lt;sup>3</sup>Power supply ranges from 1.05 to 1.2 volts. The DDR3 was between 1.2 and 1.65 volts.

devices using the TwinDie technology in 2014 [Mic16d]. Currently, DDR4 is being mass produced by many manufacturing companies and is presented as in *early adoption phase*. The market trends presented by Xilinx [Sch15] foresee that DDR4 devices will reach other memory technologies in just a few years.

Other than that, DDR memories contemplate other branches aside desktop and servers, such as low-power DDR (LPDDR) and graphics DDR (GDDR). The LPDDR presents low-power and low-heat DDR implementations and is targeted to portable devices, such as smartphones. It has presented four generations within the past few years: LPDDR (2009), LPDDR2 (2011), LPDDR3 (2013) and LPDDR4 (2014). Meanwhile, the GDDR memories are targeted to graphic processing units (GPUs). Its latest release is the GDDR5X, which holds the record for fastest DDR device available on the market, reaching to 96GB/s.

Another promising DRAM trend is 3D stacking. These memories use the Chip-on-Waferon-Substrate (CoWoS) techniques that use the Through Silicon Vias (TSV) technology to integrate and stack multiple chips into a single substrate, containing inter-chip and pin connections. This architecture allows a higher interconnection density, reducing the global connection distance and the associated RC charge. It results in better performances and lower energy consumptions. Among the architectures that present this technology are the HMC (Hybrid Memory Cube) [Sch15], HBM (High-Bandwidth Memory) [Jed15] and WideI/O (v1 and v2) [Jed14].

Table 2.1 wraps up the DDR memory technologies presented in this section, highlighting some important parameters such as release date, frequency, and transfer data rate. The table considers a 64-bit data-bus size interface for the calculation of data rates.

| Technology  | Voltage (V) | Bus Width        | Density       | Bus Frequency (MHz) | Transfer Rate (MT/s) | Data Rate (GB/s) | Year |

|-------------|-------------|------------------|---------------|---------------------|----------------------|------------------|------|

| Desktop and | Server SDRA | М                |               |                     |                      |                  |      |

| SDR         | 3.3         | x4, x8, x16, x32 | 64MB to 512MB | 66.7 to 133         | 66.7 to 133          | 0.5 to 1         | 1993 |

| DDR         | 2.5 to 2.6  | x4, x8, x16      | 256MB to 1GB  | 100 to 200          | 200 to 400           | 1.6 to 3.2       | 1996 |

| DDR2        | 1.55 to 1.8 | x4, x8, x16      | 512MB to 4GB  | 333 to 533          | 667 to 1,066         | 5.3 to 8.5       | 2003 |

| DDR3        | 1.35 to 1.5 | x4, x8, x16      | 1GB to 16GB   | 667 to 1,066        | 800 to 2,400         | 6.4 to 19.2      | 2007 |

| DDR4        | 1.05 to 1.2 | x4, x8, x16      | 4GB to 16GB   | 1,067 to 1,600      | 1,600 to 3,200       | 12.8 to 25.6     | 2014 |

| Low-Power S | DRAM        |                  |               |                     |                      |                  |      |

| LPDDR       | 1.2 to 1.8  | x16, x32, x64    | 512MB to 8GB  | 133 to 200          | 333 to 400           | 2.6 to 3.2       | 2009 |

| LPDDR2      | 1.1 to 1.8  | x16, x32, x64    | 512MB to 16GB | 208 to 533          | 800 to 1,066         | 6.4 to 8.5       | 2011 |

| LPDDR3      | 1.2         | x32, x64, x128   | 8GB to 32GB   | 800 to 933          | 1,600 to 1,866       | 12.8 to 14.9     | 2013 |

| LPDDR4      | 1.1         | x32              | 8GB to 16GB   | 1,600               | 3,200                | 25.6             | 2014 |

| Graphics SD | RAM         |                  |               |                     |                      |                  |      |

| GDDR2       | 2.5         | x4               | 1GB           | 400 to 500          | 800 to 1,000         | 6.4 to 8         | 2003 |

| GDDR3       | 2.0         | x4               | 4GB           | 500 to 800          | 1,000 to 1,600       | 8 to 12.8        | 2004 |

| GDDR4       | 1.5         | x4, x8           | 4GB           | 800 to 1,484        | 1600 to 3,200        | 12.8 to 23.2     | 2005 |

| GDDR5       | 1.35 to 1.6 | x32              | 2GB to 8GB    | 900 to 1,375        | 5,000 to 8,000       | 40 to 80         | 2013 |

| GDDR5X      | 1.35 to 1.5 | x32              | 8GB           | 1,067 to 1,500      | 10,000 to 12,000     | 80 to 96         | 2016 |

**Table 2.1:** Evolution of DDR SDRAM devices. Source: DDR devices [Mic16c], LPDDR devices [Mic12][Jed16a] and GDDR devices [Mic12][Nvi16].

#### 2.1.2 DRAM Device

The DRAM device is composed of a set of banks, which are indexed by a set of rows and columns. This way, to access a data-word<sup>4</sup>, it is necessary to translate the processor physical address into bank, row and column coordinates. Many chips are combined to form a Dual In-line Memory Module (DIMM). DIMMs comprise multiple DRAM chips and make the memory product that we see available on stores; it is characterized by the existence of pin connections on both sides of the device, different from old technologies such as the SIMMs (Single In-line Memory Module), which presented bus connections on only one side of the device. SDRAM devices allow bank parallelization to compensate for reduced internal frequencies. Figure 2.2 presents the bank distribution considering multiple chips on a DIMM. During a memory access, multiple chips can be triggered to return the requested data. It depends on the burst configuration and the memory technology. In modern DRAM devices, each side of the DIMM is called *rank*. Ranks are seen as independent DRAM structures that share the same DIMM and can be accessed in parallel presenting minimal access restrictions when compared to the parallelization of internal banks.

Figure 2.2: Bank distribution on a DIMM. Source: created by the author.

Memory accesses are made in a particular way, following a sequence of commands respecting predefined time intervals. Initially, the target bank and row are selected, following, the column of the respective row. During the access, the target row is copied into an internal buffer known as the *row-buffer*, or sense-amplifier. This row-buffer is accessible by a multiplexing module that implements the prefetch technique previously discussed. When the row-buffer contains the information of a row, we may say that it is *active*. The operation of copying the information into the row-buffer is known as *activate*. An active row-buffer is available to receive *read* or *write* operations.

Each bank contains its row-buffer; separate bank accesses are independent of each other and can be performed simultaneously. Upon receiving a closing command, the row is removed from the row-buffer and reallocated back to the bank. This closing operation is known as *precharge*. The internal structure of the DRAM, as well as an illustrative representation of its main operations, is presented in Figure 2.3. It comprises two address decoders: row and column. The *row decoder* selects a line from the target bank, transferring its data to the row-buffer. This bank is classified as *open*. The *column decoder* selects the target column to connect with the data in/out bus. In addition, the internal

<sup>&</sup>lt;sup>4</sup>Data-word is a set of bits of the same size as the width of the data-bus.

structure of DRAMs supports the activation of multiple banks. In practice, the DRAM memory can operate with all banks in open state [Bon14].

Figure 2.3: Internal DRAM structure. Source: created by the author.

The DRAM also implements the *refresh* command, which is used for updating the information contained in each cell of each bank in the memory structure. The DRAM cell is composed of a 1T1C structure that comprises a capacitor and a transistor, as seen in Figure 2.4. As a physical characteristic of capacitors, continuous discharge creates the possibility of losing information along time. The refresh command solves this problem by updating the data contained in each memory capacitor periodically. Each memory device presents a characteristic refresh cycle, but is a basic feature of all DDR generations the full memory refresh in a period of 64ms [ $M^+13$ ].

Figure 2.4: Internal DRAM cell structure (1T1C). Source: created by the author.

#### 2.1.2.1 Page Policy

The term *Page* refers to the information contained in the row-buffer. In most devices, the size of a page is the same of a row. The *page policy* states whether to close or maintain a page open in the DRAM. An effective memory controller page policy is important to minimize power consumption and increase system performance [Bla13].

Page policies are directly linked to the concept of row-hit, row-empty and row-conflict. A *row-hit* occurs when the request address is contained within the current open page in the row-buffer. Row-hits provide the lowest access latency possible for the memory module. Meanwhile, *row-empty* occurs when the request address aims a bank with closed row-buffer, and when the address aims a row-buffer that is currently holding a page different from the target row, it is called *row-conflict*.

The most common page policies used by memory controllers are *closed-page*, *fixed open-page* and *adaptive open-page*. The closed-page policy ensures that the memory controller will close the row-buffer page after every access. They guarantee a fixed execution time for every memory access and are commonly used to provide real-time guarantees.

The fixed open-page policy leaves the row-buffer page open for a fixed amount of cycles after the last read or write operation. This timeout interval can be predefined during design time or an initial configuration. The adaptive open-page policy leaves the row-buffer page open for a flexible amount of time, depending on certain parameters (e.g., access rate, power consumption, etc). These last two page policies are commonly used by high-performance memory controllers that do not seek real-time guarantees. Only open-page policies are capable of exploring row-hits.

### 2.1.2.2 Bank-Groups

The *bank-group* was first introduced by the GDDR5, and was borrowed by DDR4 and GDDR5X technologies. In these architectures, a set of banks is physically isolated from each other, composing bank-groups. Accesses to one bank-group does not corrupt or create noise interference in another. More specifically, the activation of one set of row-buffers associated to a bank-group does not corrupt the others. The inclusion of this technology in DDR devices allowed simultaneous accesses to high number of banks using higher frequencies, although, it increased the complexity of the memory controller, since additional time restrictions were added. Two main bank-group modes exist: two and four bank-groups. For DDR4 devices with x16 bus-width, banks are organized into two bank groups of eight banks each, meanwhile, for x8 and x4 DDR4 bus-width, the banks are divided into four bank-groups of four banks each [GCAG16].

### 2.1.3 DRAM Data-bus Technology

In a DRAM, the read and write commands are used to transfer data blocks with configurable sizes defined by the *burst-length* (BL) parameter. The burst access is triggered by a single command

and BL is previously configured during the initialization of the device. The data sequence considered is given by the address of the request, which indicates the initial data of the burst. For example, in case of accessing column 5, to a memory configured with BL=4, the address sequence returning is 5-6-7-8. If the same memory device is configured with BL=8, the address sequence would be 5-6-7-8-1-2-3-4. The burst always accesses a predefined number of elements, which are always contained within the open row in the row-buffer.

This architecture is called *n*-bit prefetch. For every bit accessed there are *n* correspondent bits that will follow. This way, DRAM generations allow data transfers to be *n* times faster than its internal frequencies. This technology was developed so memory interfaces could evolve in access speed and bandwidth, when compared to the internal memory core. Figure 2.5 presents a block diagram of a 2n prefetch.

Figure 2.5: Input and output of a 2n prefetch architecture. Source: created by the author.

The introduction of the prefetch technology allowed the internal memory circuitry to remain unchanged over many DDR generations. The main modifications are focused on the in/out interface parallelization, capacity and differential amplifiers [BNP<sup>+</sup>14]. The main advantage of this technique is the increase in data-bus speed that allows the improvement of memory access bandwidth.

### 2.1.4 DRAM Access

DRAM accesses are performed through a combination of commands sent to the memory in coordination to the address bus. A set of commands respecting certain time restrictions is required to execute read or write operations. These time restrictions are imposed by the internal memory architecture that operates at lower frequencies when compared to the external interface. The memory efficiency relies on well-defined time intervals that dictate the limitations of the device. As previously stated, five commands compose the set of available operations of DRAMs. These commands are activate, read, write, precharge and refresh.

#### 2.1.4.1 Activate Command

The activate command copies the target line into the row-buffer, which has enough space to accommodate one full line per activation. Two parameters are used to define the time intervals associated with the activate command: *tRCD* and *tRAS*. The minimum delay time required to perform a read or write operation is called *row to column delay* (tRCD). After this delay, the row-buffer data is available to read and write operations through the data-bus. The other timing parameter is the *row access strobe* time (tRAS), which represents the minimum time the row must stay activated before closing it. No operation on the DRAM device can take less than tRAS.

A set of activate commands can be issued to different banks, improving the memory performance by parallelizing banks. Although, consecutive active parameters must respect the *row-to-row delay* (tRRD). In modern DDR SDRAM devices, all memory banks are allowed to stay open simultaneously, although there is a time limitation during their activation, which is called *four-bank activation window* (tFAW). The tFAW parameter indicates a time window that allows the activation of only four banks. If more banks need to be activated, this time window must be respected. For example, if one bank is activated at clock cycle T1, tRRD later another bank can be activated, although, the fifth bank can only be activated at cycle T1+tFAW, which is greater than T1+4xtRRD.

### 2.1.4.2 Read Command

The read command is used to move a data segment from the row-buffer to the in/out data-bus. This command is associated with three timing parameters: *tCAS*, *tCCD* and *tBURST*. The *column access strobe* (tCAS) parameter, also known as *column latency* (*tCL*), is the required time for the memory module to transfer the response data from the row-buffer to the data-bus after receiving the read command. The *burst time* (tBURST) is associated with the prefetch technique, corresponding to the number of cycles necessary to transmit the complete data burst. Commonly, tBL is half of the configured burst length. Finally, the *column-to-column delay* (tCCD) determines the minimum delay time between consecutive read or write<sup>5</sup> commands. The complete read operation is composed of tCAS + tBURST. After a read operation, a precharge command can be issued to close the respective row-buffer after *tRTP* (*read to precharge*) cycles.

## 2.1.4.3 Write Command

The write command transfers the data information from the data-bus into the row-buffer, and consequently, into the memory matrix after a precharge. The write data-burst must be placed on the data-bus *tWL* (write latency) cycles after the write command is performed. In modern DDR SDRAM devices tWL=tCL-1. The data placed on the data-bus are stored in the memory matrix after a precharge command. To perform this command, the *write recovery delay* (tWR) must be respected. Therefore, the complete write operation takes tWL + tBURST + tWR cycles to be completed.

<sup>&</sup>lt;sup>5</sup>The tCCD is only applied to consecutive access of the same kind (read or write). Accesses of different kinds present extra penalties.

#### 2.1.4.4 Precharge Command

The precharge command marks the end of the row-access cycle. To access a new row, the precharge command must be executed. It transfers the information contained in the row-buffer, back to the memory matrix. This operation restarts the sense-amplifiers that compose the row-buffer, and prepares memory rows to a new activation. The *row precharge* delay (tRP) denotes the duration time of a precharge comman; during this interval, no other operation can be issued to the bank. The time parameters tRAS and tRP compose the *row cycle time* (tRC), which represents the minimum time interval between the memory activation and its closure.

## 2.1.4.5 Refresh Command

The characteristic leakage of capacitors is compensated by the periodical refresh operation controlled by the memory controller. The *refresh cycle time* (tRFC) parameters determine the required time for the memory to refresh one complete row. Higher the number rows, more refresh commands are necessary to update all the banks. Modern DRAM memories require the complete memory refresh in an interval of 64ms, therefore, for a module with 32,768 rows, 512 refresh commands need to be issued within this time. Another important parameter for the refresh command is the *refresh interval* (tREFI). This parameter indicates the minimum interval between refresh commands.

Low-power DDR devices present flexible refresh policies that allow the memory controller to refresh separate banks in separate times, improving bank parallelism. Up to DDR3, memory modules executed refreshes in parallel, disabling commands for all the banks during tRFC cycles. With the release of DDR4, a larger flexibility was integrated. These devices introduced the Fine-Granularity Refresh (FGR). A mechanism that allows the memory to select between three refresh modes during the initialization sequence; these are 1x, 2x and 4x. The 1x mode is equal to the one in use by past DDR generations. Meanwhile, the 2x and 4x modes allow the refresh of only 1/2 and 1/4 of the the row at each command, respectively. These new modes infer in lower tRFC delays, but the frequency of refresh commands is increased. The work presented by Mukundan [M<sup>+</sup>13] proved that, overall performance-wise, the 1x mode is still better.

#### 2.1.4.6 Command Dependencies

The interaction between commands is formed by the command sequence issued to the memory, respecting time limitations to guarantee a reliable manipulation of information. After an active command, consecutive operations can be executed on the same open row. Within these operations there are read after read, write after write, read after write and write after read. No precharge command is necessary. Although, the exchange of command types result in delay penalties. The memory device requires a minimum time to change the direction of the data-bus for different command types. Therefore, between a read and a write there must be *read to write delay* (tRTW) cycles, and between a write and a read there must be *write to read delay* (tWTR) cycles.

Figure 2.6 presents the relationships between these commands. Dependencies that affect only the target bank are called *intra-bank dependencies*, while those that can affect other banks are called *inter-bank dependencies*. Some time parameters do not necessarily create dependencies. Table 2.2 recaps all time parameters presented in this chapter.

Figure 2.6: Timing dependencies between commands and banks. Dashed lines indicate inter-bank dependencies. Source: created by the author.

Table 2.2: Summary of DDR SDRAM time parameters. Source: created by the author.

|                                | Time Parameters              |       |                         |  |  |  |  |  |

|--------------------------------|------------------------------|-------|-------------------------|--|--|--|--|--|

| tRCD                           | Row to Column Delay          | tWR   | Write Recovery          |  |  |  |  |  |

| tRAS                           | Row Access Strobe            | tRP   | Row Precharge           |  |  |  |  |  |

| tRRD                           | Row to Row Delay             | tRC   | Row Cycle time          |  |  |  |  |  |

| tFAW                           | Four-bank Activate Window    | tRFC  | Refresh Cycle           |  |  |  |  |  |

| tCL/tCAS                       | Column Access Strobe Latency | tREFI | <b>Refresh Interval</b> |  |  |  |  |  |

| tCCD                           | Column to Column Delay       | tRTW  | Read to Write time      |  |  |  |  |  |

| tBURST Burst transference time |                              | tRTW  | Write to Read time      |  |  |  |  |  |

| tWL                            | Write Latency                |       |                         |  |  |  |  |  |

### 2.1.4.7 DDR4 Command Dependencies

The presentation of the DDR4 technology brought considerable advances to the SDRAM area. The introduction of bank-groups allowed burst accesses to 16-bank devices in parallel and presenting reduced interference. Although, this new technology also presented new time parameters, which increased the project complexity of memory controllers targeting this device. These new time parameters define that different bank-group accesses must be prioritized to achieve high bandwidths.

The new time parameters present a \_*S* and \_*L* suffix that stand for *Small* and *Large*, respectively. Consecutive memory requests targeting different bank-groups consider parameters with \_S. Meanwhile, requests to the same bank-group consider parameters \_L. All \_L parameters are higher than \_S. Among the DDR4 new parameters are tCCD\_S, tCCD\_L, tRRD\_S, tRRD\_L, tWTR\_S and tWTR\_L.

# **3. MEMORY CONTROLLERS**

This chapter presents the role and functionality of memory controllers in the memory subsystem. In the end, it presents some state-of-the-art controllers and their main characteristics.

## 3.1 Classic Memory Controller

The Memory Controller (MC) serves as the interface between the Central Processing Unit (CPU), or the last cache level, and main memory. It translates read and write commands, generated by the system, into memory-friendly operations. Its main objective is to provide a reliable communication, aiming to optimize the system performance by guaranteeing low-latency and high-bandwidth memory accesses. A sound implementation of a memory controller demands to understand the system requirements and the memory limitations [Inp14].

In a memory controller, CPU addresses (linear address) are translated into physical DRAM addresses, composed of rank, bank, row, and column. Also, it is responsible for handling write and read data to correctly transmit it from and to the requesting CPU, respectively. This communication is established via a *channel*, which is connected to the memory *port*. For modern general purpose CPUs, each channel has a width of 64 bits, whereas, for embedded systems, this value may vary [Bon14]. As described in Chapter 2, a memory DIMM is composed of multiple 4, 8 or 16-bit width memory devices, which are accessed in parallel to supply the CPU demand. Most commonly, each memory controller is attached to a single channel, but it can also access multiple memory devices in parallel to supply a higher width channel (i.e., 128 bits). Figure 3.1 considers three different system configuration.

**Figure 3.1:** System configurations: (a) Single-channel (b) Dual-channel and (c) High-bandwidth 128-bit channel. Source: adapted from [Bon14].

Requesting a read or write access to an external memory takes greater time when compared to local memories (i.e., caches). Figure 3.2 presents the request path from and back to the CPU. Initially, the CPU performs the read/write request (step A), following, the memory controller translates the