# ESCOLA POLITÉCNICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO MESTRADO EM CIÊNCIA DA COMPUTAÇÃO

MARCOS LUIGGI LEMOS SARTORI

**PULSAR: TOWARDS A SYNTHESIS FLOW FOR QDI CIRCUITS**

Porto Alegre 2019

PÓS-GRADUAÇÃO *- STRICTO SENSU*

Pontifícia Universidade Católica do Rio Grande do Sul

## PONTIFICAL CATHOLIC UNIVERSITY OF RIO GRANDE DO SUL SCHOOL OF TECHNOLOGY COMPUTER SCIENCE GRADUATE PROGRAM

## PULSAR: TOWARDS A SYNTHESIS FLOW FOR QDI CIRCUITS

## MARCOS LUIGGI LEMOS SARTORI

Dissertation submitted to the Pontifical Catholic University of Rio Grande do Sul in partial fullfillment of the requirements for the degree of Master in Computer Science.

Advisor: Prof. Dr. Ney Laert Vilar Calazans Co-Advisor: Dr. Matheus Trevisan Moreira

## Ficha Catalográfica

## S251p Sartori, Marcos Luiggi Lemos

Pulsar: Towards a Synthesis Flow for QDI Circuits / Marcos Luiggi Lemos Sartori. – 2019.

195.

Dissertação (Mestrado) – Programa de Pós-Graduação em Ciência da Computação, PUCRS.

Orientador: Prof. Dr. Ney Laert Vilar Calazans. Co-orientador: Prof. Dr. Matheus Trevisan Moreira.

1. Asynchronous circuits. 2. QDI. 3. EDA. 4. Modelling. 5. Synthesis. I. Calazans, Ney Laert Vilar. II. Moreira, Matheus Trevisan. III. Título.

Elaborada pelo Sistema de Geração Automática de Ficha Catalográfica da PUCRS com os dados fornecidos pelo(a) autor(a).

Bibliotecária responsável: Clarissa Jesinska Selbach CRB-10/2051

## Marcos Luiggi Lemos Sartori

## **Pulsar: Towards a Synthesis Flow for QDI Circuits**

This Master Thesis has been submitted in partial fulfillment of the requirements for the degree of Doctor/Master of Computer Science, of the Graduate Program in Computer Science, School of Technology of the Pontifícia Universidade Católica do Rio Grande do Sul.

Sanctioned on the 22nd of August 2019.

#### **COMMITTEE MEMBERS:**

Prof. Dr. Renato Perez Ribas (PGMicro/UFRGS)

Prof. Dr. Fernando Gehm Moraes (PPGCC/PUCRS)

Dr. Matheus Trevisan Moreira (Chronos Tech – Co-advisor)

Prof. Dr. Ney Laert Vilar Calazans (PPGCC/PUCRS - Advisor)

To those I love,

## PULSAR: EM DIREÇÃO A UM FLUXO DE SÍNTESE PARA CIRCUITOS QDI

#### **RESUMO**

Circuitos assíncronos guase-insensíveis a atrasos ou QDI são conhecidos pela robustez a variações de PVT. Isso os torna bons candidatos para uso de técnicas de projeto agressivas de redução da tensão de alimentação. No entanto, a adoção do projeto QDI em escala industrial é dificultada: (i) pela dependência de ferramentas de projeto especializadas para circuitos QDI; (ii) pela falta de integração com fluxos de projeto ASIC tradicionais. Esta Dissertação propõe Pulsar, um novo fluxo de síntese para o projeto QDI. Pulsar emprega ferramentas comerciais de automação de projeto eletrônico (EDA) para capturar o projeto, expandir descrições para uso de códigos insensíveis a atrasos, e realizar o mapeamento tecnológico e a otimização de circuitos QDI. Ferramentas EDA comerciais habilitam projetistas a definir objetivos de desempenho e equilibrar características de energia e área. Esta Dissertação traz seis contribuições originais: (i) um fluxo pseudo-síncrono estendido, que agrega novos modelos de registradores; (ii) o fluxo SDDS-NCL seguencial, para lidar com descrições de projeto genéricas (combinacionais e/ou sequenciais); (iii) o modelo rede de canais meio-buffer ou HBCN, que viabiliza a análise de temporização de circuitos assíncronos QDI meio-buffer; (iv) uma formulação de programação linear para restringir projetos a operar com um tempo de ciclo assíncrono alvo. (v) uma técnica de captura de projeto similar à RTL para circuitos síncronos e uma técnica associada para a expansão de descrições de circuitos para versões em trilha dupla; (vi) uma ferramenta de cálculo automatizado de restrições de síntese para circuitos QDI. Experimentos mostram que Pulsar permite o projeto de circuitos assíncronos a partir de descrições similares a RTL sujeitas a restrições de tempos de ciclo. Pulsar permite designar tempos de ciclo alvo para circuitos QDI usando ferramentas comerciais, o que constitui um avanço para projetistas QDI, que agora podem vincular com segurança métricas de desempenho de pior caso a projetos. Além disso, Pulsar permite que projetistas definam o desempenho para otimização de energia ou de área, capitalizando nas folgas dos orçamentos temporais do circuito.

Palavras-Chave: Circuitos assíncronos, QDI, EDA, NCL, modelagem, síntese, projeto.

## PULSAR: TOWARDS A SYNTHESIS FLOW FOR QDI CIRCUITS

#### **ABSTRACT**

Asynchronous quasi-delay-insensitive (QDI) circuits are known for their robustness against PVT variations. This makes them good candidates for enabling aggressive voltage scaling design techniques. However, the adoption of QDI design by industries is hindered by: (i) the dependency on specialised design tools for QDI circuits; (ii) the lack of integration with traditional ASIC design flows. This Dissertation presents Pulsar, a new synthesis flow for QDI circuit design. Pulsar leverages commercial EDA tools for design capture, dual-rail expansion, technology mapping and optimisation of QDI circuits. Commercial EDA tools enable designers to define performance targets and naturally balance power and area optimisation. The Dissertation brings six main original contributions: (i) an extended pseudosynchronous flow, with new register models; (ii) a generalised SDDS-NCL flow to deal with both combinational and sequential circuits; (iii) the proposition of half-buffer channel network (HBCN), a new model for timing analysis of half-buffer asynchronous circuits; (iv) a linear programming formulation to constrain a design to a target asynchronous cycle time. (v) an RTL-like design capture technique and an associated dual-rail expansion technique; (vi) a tool that automatically extracts the HBCN model of a circuit and computes its synthesis constraints. Results show that Pulsar enables the design of asynchronous circuits from an RTL-like description under cycle-time constraints. Pulsar enables the sign-off of target cycle times for QDI circuits using commercial EDA tools. This is a breakthrough for QDI designers, as they can now safely bound worst case performance metrics for applications. Moreover, Pulsar enables designers to naturally trade performance for power or area optimisations, whenever there is slack in timing budgets.

**Keywords:** Asynchronous circuits, QDI, EDA, NCL, modelling, synthesis, design.

## **LIST OF FIGURES**

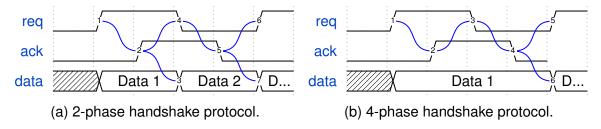

| 2.1  | Examples of handshake protocols: (a) 2-phase; (b) 4-phase                                                                                                | 31 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

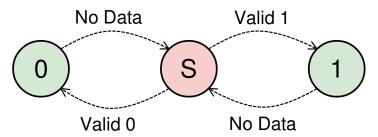

| 2.2  | The basic transition diagram for transmitting binary data in a QDI channel, where S stands for the spacer. Adapted from [MBSC18]                         | 33 |

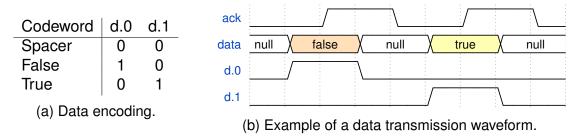

| 2.3  | RTZ dual-rail channel operation: (a) encoding; (b) example waveforms.  Adapted from [MBSC18]                                                             | 34 |

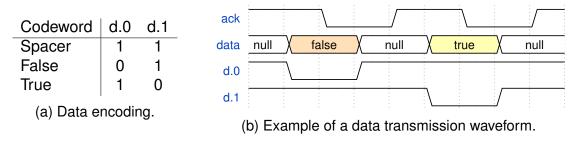

| 2.4  | RTO dual-rail channel operation: (a) encoding; (b) example waveforms.  Adapted from [MBSC18]                                                             | 35 |

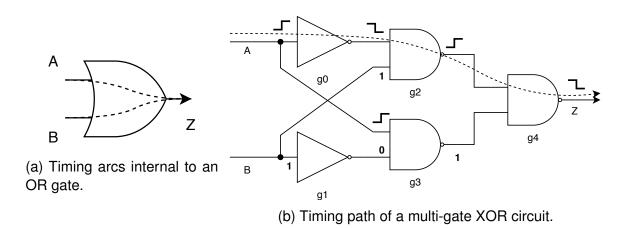

| 2.5  | Timing models used by the STA engine: (a) gate timing arcs; (b) timing paths.                                                                            | 36 |

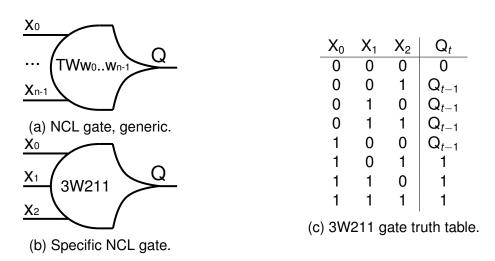

| 3.1  | Characteristics of NCL gates: (a) generic symbol; (a) generic symbol; (b) specific symbol example; (c) example truth table behaviour                     | 41 |

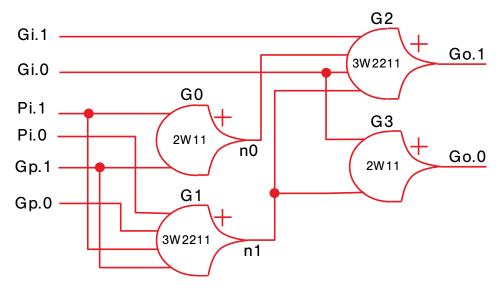

| 3.2  | Example of an NCL implementation: the generate path of part of a Kogge-Stone adder. Adapted from [MTMC14]                                                | 42 |

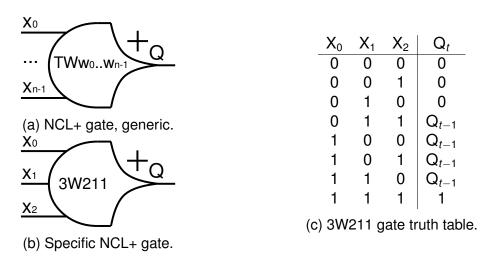

| 3.3  | Characteristics of NCL+ gates: (a) generic symbol; (a) generic symbol; (b) specific symbol example; (c) example truth table behaviour                    | 43 |

| 3.4  | Example of an NCL+ implementation: the generate path of part of a Kogge-Stone adder. Adapted from [MTMC14]                                               | 43 |

| 3.5  | Example of an SDDS-NCL circuit: the generate path for a Kogge-Stone adder. Adapted from [MTMC14]                                                         | 45 |

| 3.6  | Two arc models for a resetable C-element: (a) conventional description; (b) pseudo-synchronous description [TBV12]                                       | 48 |

| 3.7  | Simplified view of a 1-bit data channel WCHB pipeline, showing the inner cycles controlled by the pseudo-clock                                           | 49 |

| 3.8  | Proposed characterisation models for a resetable C-element with a dummy clock pin, G: (a) pseudo-flop; (2) pseudo-latch                                  | 50 |

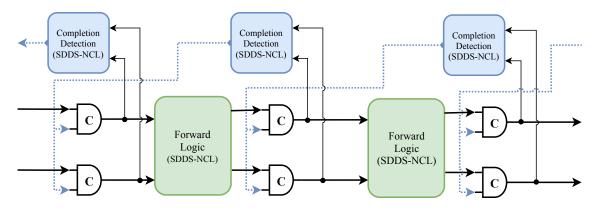

| 3.9  | Structure of a sequential SDDS-NCL pipeline                                                                                                              | 51 |

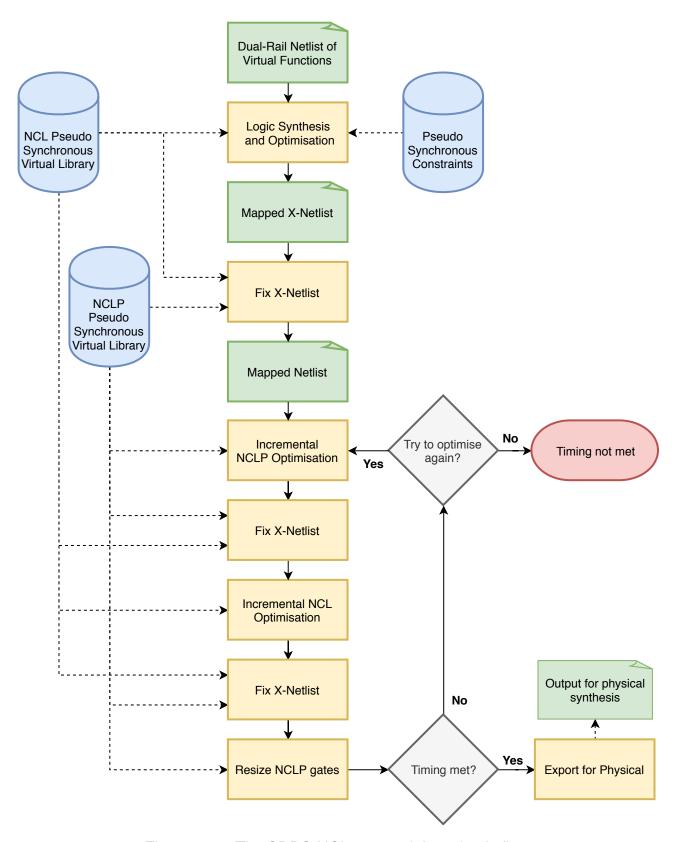

| 3.10 | The SDDS-NCL sequential synthesis flow                                                                                                                   | 52 |

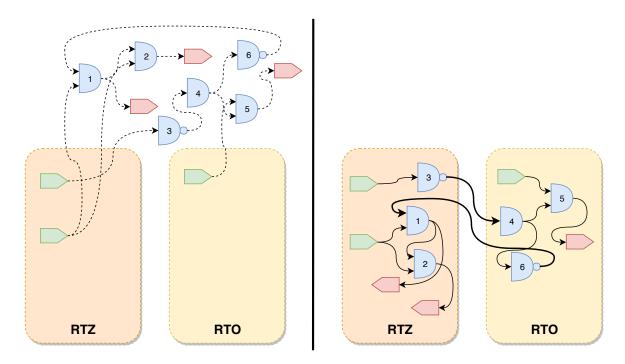

| 3.11 | Illustration of the RTO and RTZ gate classification process                                                                                              | 53 |

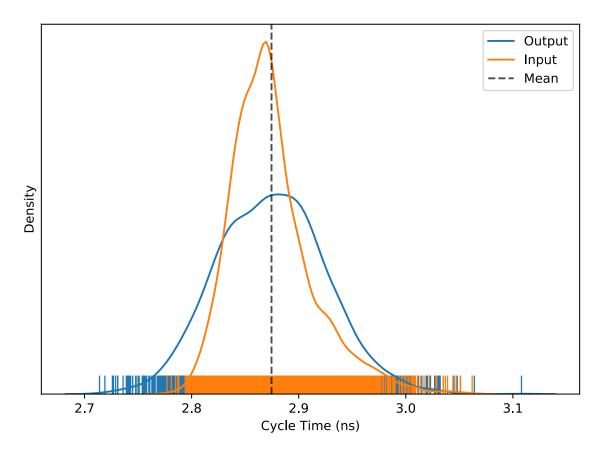

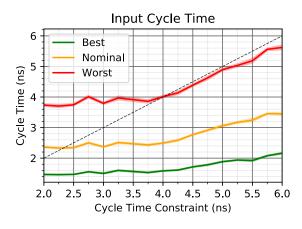

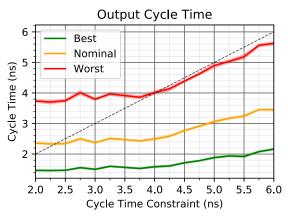

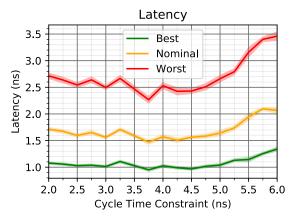

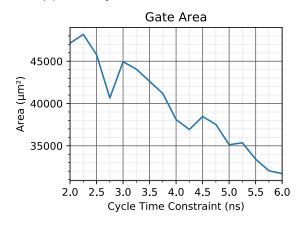

| 4.1  | Observed cycle time distribution at the input and output of an integer, 6-stage, multiply-and-accumulate circuit                                         | 59 |

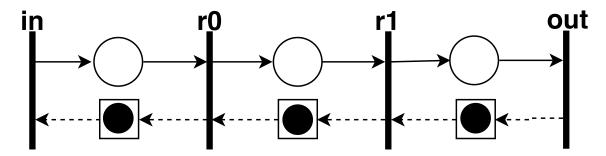

| 4.2  | FBCN modelling a 2-phase, half-buffer pipeline. Vertical lines are transitions, circles are forward-propagation places, squares are backward-propagation |    |

|      | places and black dots are tokens                                                                                                                         | 60 |

| 4.3  | A 2-stage dual-rail linear buffer, implemented using a WCHB half-buffer 4-stage RTZ pipeline                                                             | 63 |

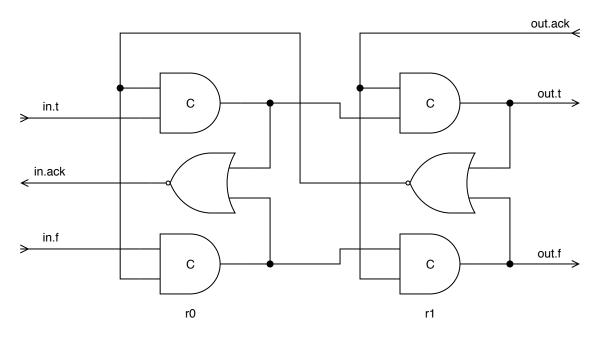

| 4.4 | Example HBCN modelling a 4-phase, half-buffer circuit. Blue lines are valid data transitions; red lines are spacer transitions; squares are backward                                    |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | propagation places; circles are forward propagation places                                                                                                                              | 64  |

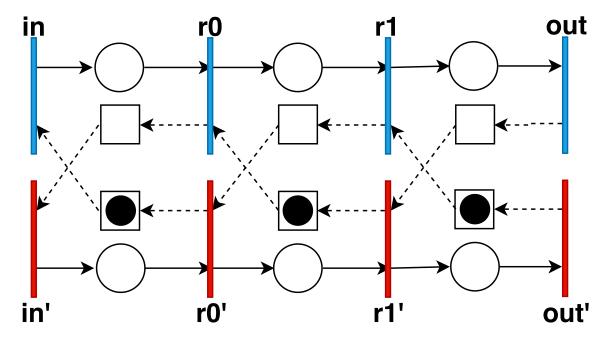

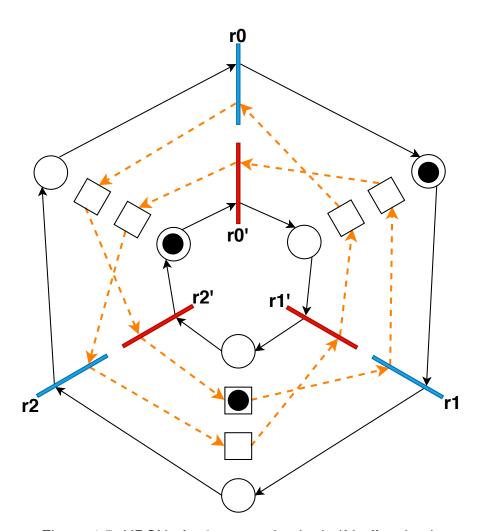

| 4.5 | HBCN of a 3-stage, circular half-buffer circuit                                                                                                                                         | 67  |

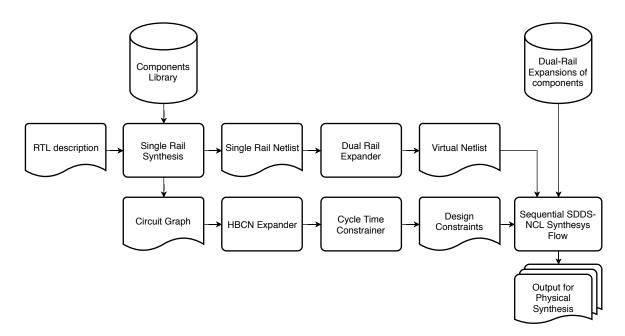

| 5.1 | The Pulsar synthesis flow                                                                                                                                                               | 75  |

| 5.2 | Expansion of the nand2 gate from: (a) a single-rail Boolean truth table to (b) a 3NCL code table. In the tables, (-) indicates hysteretic behaviour                                     | 81  |

| 5.3 | Map between codes. Only valid codewords are depicted                                                                                                                                    | 81  |

| 5.4 | Dual-rail RTZ code table of the NAND2 gate with equivalent 3NCL codewords. Here, (-) means hold the previous value and (-/0) means that either: hold the previous value, or set it low. | 82  |

| 5.5 | Truth tables for the output rail functions: (a) false rail; (b) true rail. Here, (-) represents hysteretic behaviour and (?) represents that the value is a "don't-care".               | 83  |

| 5.6 | Truth tables for the output rail virtual functions: (a) false rail; (b) true rail. Here, (?) represents that the input value is a "don't-care"                                          | 84  |

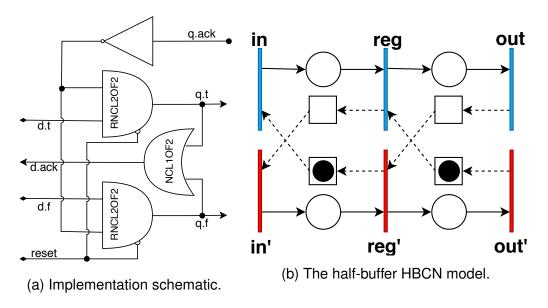

| 5.7 | The dff half-buffer dual-rail register: (a) schematic; (b) HBCn model                                                                                                                   | 87  |

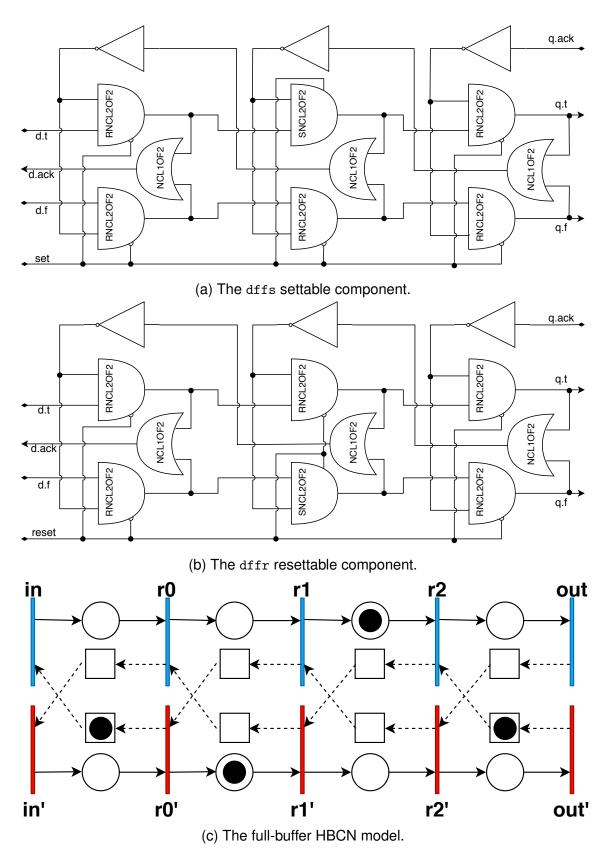

| 5.8 | The two full-buffer components: (a) DFF with set; (b) DFF with reset; (c) the HBCN model                                                                                                | 88  |

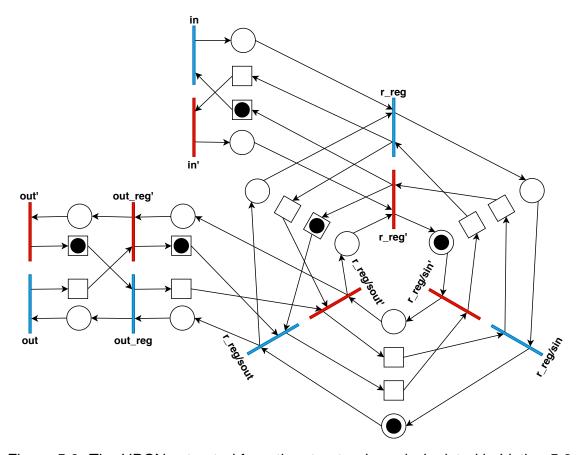

| 5.9 | The HBCN extracted from the structural graph depicted in Listing 5.8                                                                                                                    | 95  |

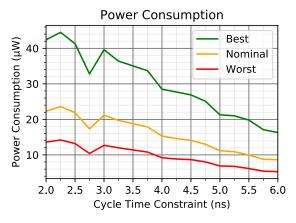

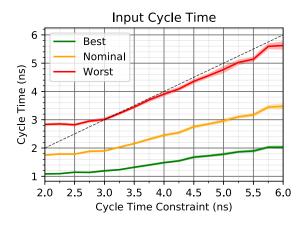

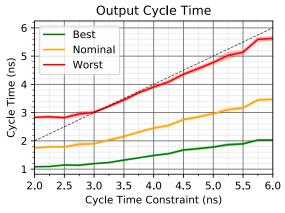

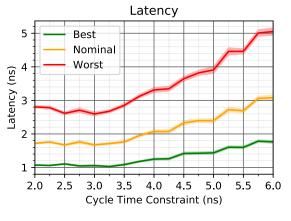

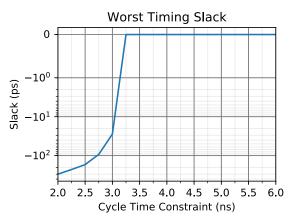

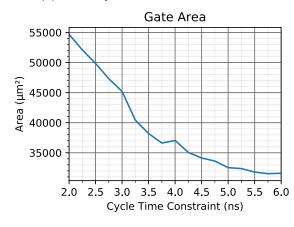

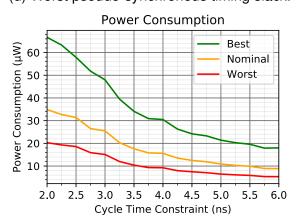

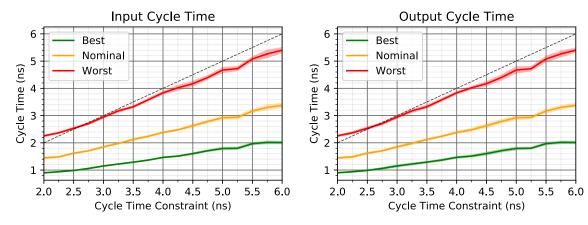

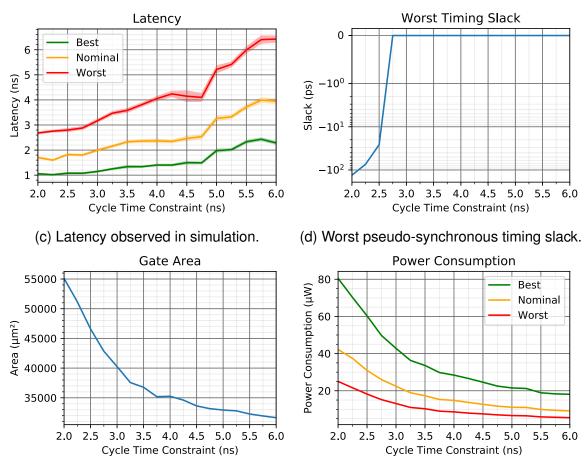

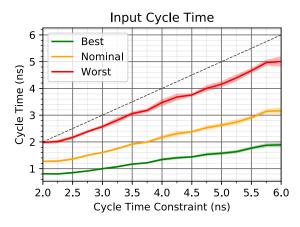

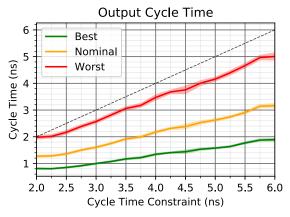

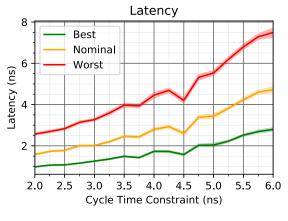

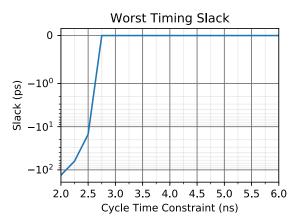

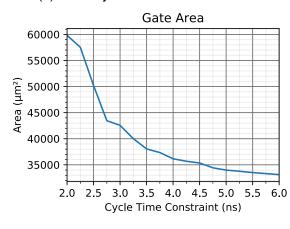

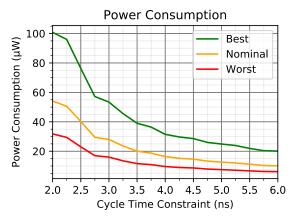

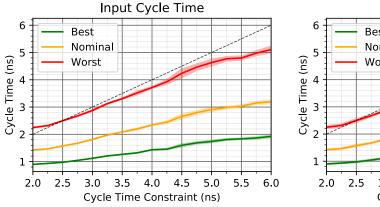

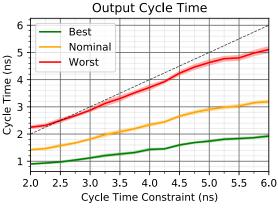

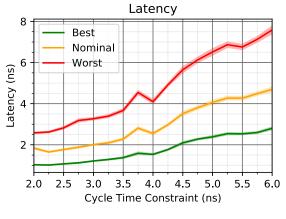

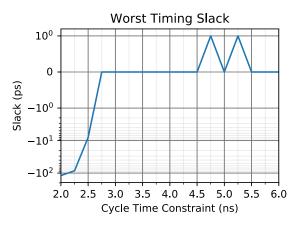

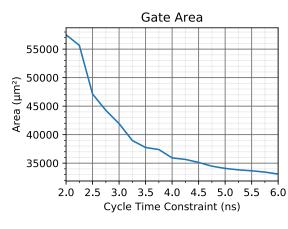

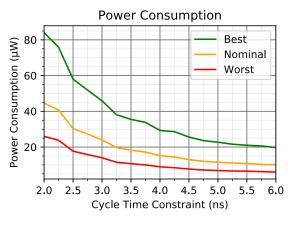

| 6.1 | Results for the 3-stage MAC                                                                                                                                                             | 106 |

| 6.2 | Results for the 4-stage MAC                                                                                                                                                             | 107 |

| 6.3 | Results for the 5-stage MAC                                                                                                                                                             | 108 |

| 6.4 | Results for the 6-stage MAC                                                                                                                                                             | 109 |

| 6.5 | Results for the 6-stage MAC synthesised with timing path exceptions on free-slack.                                                                                                      | 110 |

## **LIST OF TABLES**

| 4.1 | Solution of the LP formulation                               | 68  |

|-----|--------------------------------------------------------------|-----|

| 4.2 | Solutions to the LP problem in Algorithm 4.2                 | 71  |

| 4.3 | Solutions to the LP problem in Algorithm 4.3                 | 72  |

| 5.1 | Combinational gates of the component library                 | 85  |

| 6.1 | Characteristics of the virtual netlists for each MAC version | 104 |

## **LIST OF ALGORITHMS**

| 3.1 | The Fix X-Netlist algorithm.                                                                                                 | 54 |

|-----|------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | LP formulation to compute the cycle time and free slack for the example HBCN                                                 | 68 |

| 4.2 | LP formulation to constrain the cycle time of the HBCN in Figure 4.5 to 2ns, using the pseudo-clock method with fixed delays | 71 |

| 4.3 | LP formulation to constrain the cycle time of the HBCN in Figure 4.5 to 2ns, using the pseudo-clock method                   | 72 |

## **CONTENTS**

| 1     | INTRODUCTION AND MOTIVATION                                | 23 |

|-------|------------------------------------------------------------|----|

| 1.1   | ASYNCHRONOUS CIRCUITS AS AN ALTERNATIVE                    | 24 |

| 1.2   | CHALLENGES TO QDI ADOPTION                                 | 24 |

| 1.3   | CONTRIBUTIONS OF THIS WORK                                 | 25 |

| 2     | BACKGROUND                                                 | 27 |

| 2.1   | GRAPHS AND PETRI NETS                                      | 27 |

| 2.1.1 | PETRI NETS                                                 | 28 |

| 2.1.2 | PETRI NET PROPERTIES                                       | 29 |

| 2.1.3 | MARKED GRAPHS                                              | 30 |

| 2.2   | HANDSHAKE PROTOCOLS                                        | 31 |

| 2.3   | QUASI-DELAY-INSENSITIVE DESIGN                             | 32 |

| 2.4   | STATIC TIMING ANALYSIS                                     | 35 |

| 3     | THE PSEUDO-SYNCHRONOUS SDDS-NCL DESIGN TEMPLATE            | 39 |

| 3.1   | THE SDDS-NCL ASYNCHRONOUS DESIGN TEMPLATE (RELATED WORK) . | 39 |

| 3.2   | PSEUDO-SYNCHRONOUS WEAK-CONDITIONED HALF BUFFER (RELATED   |    |

|       | WORK)                                                      | 47 |

| 3.3   | THE PSEUDO-SYNCHRONOUS SDDS-NCL SYNTHESIS FLOW             | 50 |

| 4     | A NEW MODEL FOR CYCLE TIME COMPUTATION                     | 57 |

| 4.1   | CYCLE TIME OF ASYNCHRONOUS CIRCUITS                        | 57 |

| 4.2   | THE FBCN TIMING MODEL (RELATED WORK)                       | 58 |

| 4.3   | THE HBCN TIMING MODEL                                      | 61 |

| 4.4   | CALCULATING THE MAXIMUM CYCLE TIME                         | 65 |

| 4.5   | CONSTRAINING THE MAXIMUM CYCLE TIME                        | 69 |

| 5     | THE PULSAR SYNTHESIS FLOW                                  | 75 |

| 5.1   | QDI SYNTHESIS SYSTEMS (RELATED WORK)                       | 76 |

| 5.2   | DUAL-RAIL CHANNELS                                         | 77 |

| 5.3   | A LIBRARY OF COMPONENTS                                    | 79 |

| 5.3.1 | COMBINATIONAL COMPONENTS                                   | 80 |

| 5.3.2 | SEQUENTIAL COMPONENTS                                      | 86 |

| 5.4 | A CASE STUDY: APPLYING THE DUAL RAIL EXPANSION FLOW          | 89  |

|-----|--------------------------------------------------------------|-----|

| 5.5 | THE HBCN CONSTRUCTION AND THE CYCLE TIME CONSTRAINING        | 92  |

| 5.6 | COMPLETING THE CASE STUDY SYNTHESIS                          | 98  |

| 6   | EXPERIMENTS AND RESULTS                                      | 101 |

| 7   | CONCLUSION AND FUTURE WORK                                   | 111 |

|     | REFERENCES                                                   | 113 |

|     | APPENDIX A – The Single-Rail Synthesis Scripts               | 119 |

|     | APPENDIX B – The Dual-Rail Expander                          | 133 |

|     | APPENDIX C – The Cycle Time Constrainer                      | 139 |

|     | <b>APPENDIX D</b> – The Pseudo-Synchronous Synthesis Scripts | 147 |

## 1. INTRODUCTION AND MOTIVATION

Advances in semiconductor fabrication technologies allow higher integration, but impose design challenges. Some of the challenges faced in newer technologies are: (i) higher sensitivity to process variations; (ii) higher static power; and (iii) longer wire delays. Process variations are consequence of imperfections in the fabrication process and manifest themselves as changes in some circuit electrical properties. Static power is the power dissipated by the circuit when idle, that is, when no switching activity is taking place. Higher static power can be attributed to higher leakage current, due to thinner oxide layers between the transistor channel and the transistor gate. It is roughly proportional to the number of transistors in the die, each providing a contribution to the overall leakage power. Larger wire delays are attributable to smaller wire cross sections and relatively longer wire length, which cause reduced wire current capacity, higher parasitic capacitance and (relatively) increased effects of coupling with neighbour wires. Wire delays in recent technologies make it unfeasible to route global signals in large circuits without using buffers to "repeat" the signal during its propagation.

They pose a challenge to synchronous circuits, as these employ a global "clock" signal to provide a discrete time reference for synchronisation. The clock signal distribution is assumed to be ideal, meaning that the clock arrives to all locations in the circuit (where it is used) at nominally the same time. Meeting this clock distribution criteria requires a clock distribution network composed of buffers and other signal distribution components. This clock distribution network can have a high cost in area and power. The power consumption associated to the clock distribution can be a significant percentage of the overall power dissipated by complex circuits. Taking 40% of the total power consumption is not unusual [DMM04]. Also, as ideal clock distribution networks with no skew are difficult to achieve or even impossible to obtain, it becomes necessary to compensate the skew and uncertainties by introducing margins in the clock period. This of course impacts overall circuit performance.

Modern designs mitigate these issues by dividing the circuit in clock domains and using synchronisers to transfer signals between clock domain boundaries. The approach only helps solving the problem locally. However, logic spread across a large area (e.g. interconnects) still suffers from clock distribution problems. Furthermore, the use of multiple clock domains can result in significant synchronisation overheads, as different clock domains are possibly working at different clock phases and/or operating frequencies. A possible solution is the overall elimination of global or semi-global clock signals. Digital circuits without any global or semi-global clock signals are known as *asynchronous circuits*.

## 1.1 Asynchronous Circuits as an Alternative

In asynchronous circuits the delay of individual pipeline stages is not constrained by a global clock signal. The overall performance of the circuit is constrained only by the actual delay of data processing in its pipelines. This creates opportunities to design innovative pipeline architectures [NS15a, NS15b]. The elimination of the constraints imposed by clock distribution allows the design of fine-grained pipelines. It also allows on-demand operation analogous to very fine-grained clock gating without the associated clock gating costs.

There are two major classes of asynchronous circuits: (i) Bundled Data (BD) is a class of asynchronous circuits where correct functionality depends on assumptions about the propagation delay of individual pipeline stages; (ii) Quasi Delay Insensitive (QDI) is a class of asynchronous circuits that use Delay Insensitive (DI) codes to better tolerate gate and wire delays and their variations. Besides the advantages provided by clock elimination, QDI circuits are naturally more resilient to delay variations.

A common source of delay variations are PVT variations, ageing and other challenges faced by recent sub-micron technologies. For example, intra-die process variation causes the same gate in different parts of the circuit to present different switching delays, what can possibly lead to faulty circuit behaviour and lower production yield. This problem affects interconnect circuits more acutely, as they span over a large silicon area. QDI circuits are thus excellent candidates to tolerate the conditions imposed by intrinsic intra-die process variations. Circuits that use QDI interconnects between synchronous components can take advantage of this aspect of QDI circuits. Furthermore, the mixed use of asynchronous circuits as interconnect for synchronous components solve some of the synchronisation problems between clock domains.

## 1.2 Challenges to QDI Adoption

The design of QDI circuits often relies on specialised infrastructures, which can frequently hinder the adoption of QDI circuit design. This infrastructure often includes: (i) specific gate libraries, containing e.g. C-Elements, NCL gates or PCHB logic cells; (ii) specific synthesis tools; and (iii) specific design capture languages.

QDI circuits normally require the use of gates with hysteretic behaviour to facilitate or enable handshake synchronisation. A hysteretic gate holds the output stable until certain criteria are met. These special gates, are not usually available in conventional cell libraries designed for synchronous semi-custom ASIC flows.

Specialised tools like Uncle [RST12] and Balsa [EB02], both briefly covered in Section 5.1, can be used to produce asynchronous circuits. However, these specialised tools

do not integrate well with semi-custom ASIC flows. They also lack the power and flexibility provided by commercial EDA tools.

Another challenge to design asynchronous circuits is guaranteeing some minimal throughput operating point. This throughput is constrained by the maximum cycle time of the circuit. However, on complex concurrent asynchronous systems cycle time is not trivial to capture. Synchronous circuits typically rely on register transfer level (RTL) models, where the maximum throughput is limited by a clock period. This not only makes design capture simpler, but also eases the task of optimising a netlist, as every timing path has a same, fixed maximum delay constraint, the clock period. In fact, synchronous RTL models drove decades of development on commercial EDA tools, which provide strong means for designers to explore power, performance and area optimisation in modern technologies. These means are nonetheless very specific, and efforts to abandon the synchronous paradigm in exchange for more powerful design techniques can easily make commercial tools not applicable. Accordingly, the support for asynchronous design lags behind and, as technologies get less predictable and wire dominated, there is a particular need for new solutions that allow asynchronous circuit optimisation after technology mapping and during physical design.

An alternative that allows the use of commercial EDA tools started to be explored by works that proposed the WHCB pseudo-synchronous design flow [TBV12] and the SDDS-NCL design flow [MTMC14, MNM+14, MBSC18]. These approaches demonstrated advantages over specialised tools. They are further described respectively in Section 3.2 and in Section 3.1.

#### 1.3 Contributions of this Work

This dissertation presents Pulsar, an innovative synthesis flow for QDI circuits. Pulsar enables the design of asynchronous circuits from a RTL-alike description under cycletime constraints. Pulsar integrates the pseudo-synchronous and the SDDS-NCL design flows to enable technology mapping and optimisation of sequential SDDS-NCL circuits with commercial EDA tools. It proposes a timing model that enables the cycle time analysis and constraining using standard STA tools. Pulsar also leverages EDA tools for the design capture and dual-rail expansion of QDI circuits.

The Pulsar Flow enables the sign-off of target cycle times for QDI circuits using commercial EDA tools. This is a major breakthrough for QDI designers, as they can now safely bound worst case performance metrics for their target applications. Moreover the flow enables designers to naturally trade performance for power or area optimisations, whenever there is slack in timing budgets.

This work has six main original contributions:

- 1. Extends the pseudo-synchronous design technique, introducing new registers models.

- 2. Generalises the SDDS-NCL flow to deal with both, combinational and sequential designs.

- 3. Proposes the half-buffer channel network (HBCN), a new model for timing analysis of half-buffer asynchronous circuits.

- 4. Devises linear programming formulations to constrain an asynchronous design to a target cycle time.

- 5. Introduces an RTL-like design capture technique, associated dual-rail expansion and synthesis flow that leverages commercial EDA tools.

- 6. Creates a tool that automatically extracts the HBCN model of a circuit and computes synthesis constraints that meet a target cycle time.

Chapter 3 describes in some detail contributions 1 and 2. Contributions 3 and 4 are the target of Chapter 4. The last two original contributions (Contributions 5 and 6) are explored as part of the Pulsar flow description, in Chapter 5.

## 2. BACKGROUND

This Chapter provides an introduction to some topics required to read this dissertation. It also establishes some of the terminology used throughout the work. Sections 2.1 provide formal definitions for Petri nets and marked graphs used throughout this work, which are the basis for the HBCN model proposed herein. Sections 2.2 and 2.3 provide an overview of asynchronous circuits, especially QDI circuits. They also provide definitions for the RTO and RTZ handshake protocols, extensively employed in this Dissertation. Finally, Section 2.4 provides and overview of Static Timing Analysis, a fundamental concept for dealing with (asynchronous) cycle time constraints and their computation.

## 2.1 Graphs and Petri Nets

Most definitions used in this work rely on or derive from the fundamental concept of *graphs*, or more specifically on *directed graphs*. Accordingly, a precise definition of this concept is provided here, based on classical texts definitions such as the one provided by Cormen et al. [CLRS09].

**Definition 2.1.1 (Directed Graph)** A directed graph (or digraph) G is a pair G = (V, E), where V is a finite set and E is a binary relation on V. The set V is called the vertex set of G, and its elements are called vertices (singular: vertex). The set E is called the edge set of G, and its elements are called edges.

Given a vertex  $v \in V$  of a graph G = (V, E), the subset of V with the form  $\{w | w \in V \land (w, v) \in E\}$  is called the **preset** of vertex v. Accordingly, given a vertex  $v \in V$  of a graph G = (V, E), the subset of V with the form  $\{w | w \in V \land (v, w) \in E\}$  is called the **postset** of vertex v.

Unless otherwise noted, in this work all references to graphs refer to directed graphs and the word *directed* is omitted. Note that the previous definition includes describing the predecessor and successor vertex sets in graphs, a concept very important for more elaborate structures used herein. Graphs are generic structures that can be specialised to address more specific modelling needs. One such specialisation relevant here is that of *bipartite graphs*.

**Definition 2.1.2 (Bipartite Graph)** A **bipartite graph** is a directed graph G = (V, E) where the set V is in the union of two sets,  $V = W \cup X$  and where E is formed by edges having exactly one element from W and one element from X, i.e.  $E \subseteq \{(a, b) | ((a \in W) \land (b \in X)) \lor ((a \in X) \land (b \in W))\}$ .

#### 2.1.1 Petri Nets

Often, the modelling of asynchronous circuits relies on Petri nets, whose static structure can be captured by graphs. The next definitions formalise the general concept of Petri nets and particularise it to more specific forms useful in asynchronous circuit modelling.

Note that a Petri net has a static structure, an initial marking and a marking evolution behaviour, the two later ones encompassing the dynamics of the net. The definition covers all parts of the concept, and is based on [Mur89].

**Definition 2.1.3 (Petri Net (PN))** A **Petri net** is a 5-tuple  $PN = (P, T, F, W, M_0)$  where:  $P = \{p_1, p_2, ..., p_m\}$  is a finite set of **places**,  $T = \{t_1, t_2, ..., t_n\}$  is a finite set of **transitions**,  $F \subseteq (P \times T) \cup (T \times P)$  is a set of **arcs**, collectively called the **Petri net flow relation**,  $W : F \longrightarrow \mathbb{N}^*$  is the **weight** function, and  $M_0 : P \to \mathbb{N}$  is the **initial marking**, with  $P \cap T = \emptyset$  and  $P \cup T \neq \emptyset$ . The **Petri net structure** is the 4-tuple N = (P, T, F, W) with no consideration of marking. A Petri net with a given initial marking can be alternatively denoted by  $(N, M_0)$ .

The **behaviour** of a Petri net relies on a set of rules that dictate how a **marking** or **state** evolves into another state, according to the following set of **firing rules**:

- 1. A transition t is said to be enabled if each input place p of t is marked with at least w(p, t) tokens, where w(p, t) is the weight of the arc from p to t;

- 2. An enabled transition may or may not fire, depending on whether or not the event actually takes place;

- 3. A firing of an enabled transition t removes w(p, t) tokens from each input place p of t, and adds w(t, p) tokens to each output place p of t, where w(t, p) is the weight of the arc from t to p.

A transition without any input place is called a **source transition**, and one without any output place is called a **sink transition**. Note that a source transition is unconditionally enabled, and that the firing of a sink transition consumes tokens, but does not produce any.

A pair of a place p and a transition t is called a **self-loop** if p is both an input and output place of t. A Petri net is said to be **pure** if it has no self-loops. A Petri net is said to be **ordinary** if all of its arc weights are 1.

It should be clear from the PN definition and from Definition 2.1.2 that the structure N of a PN can be represented by a bipartite graph where the vertex set V of the graph is the union of the set of places and of the set of transitions of the Petri net, i.e.  $V = P \cup T$ . Because of this, it is common and practical to informally state that PNs *are* bipartite graphs, ignoring the underlying marking and behaviour concepts. A big advantage of treating a PN

as a graph is inheriting to PNs all graph concepts, e.g. vertex degrees, vertices (places or transitions) presets and postsets, etc. Where precision is not compromised, this document adopts this little abuse.

#### 2.1.2 Petri Net Properties

A large set of behavioural properties derives from the definition of a PN; Techniques to analyse PN instances for such properties abound in the literature. This Section explores PN properties specifically relevant to this work. The interested reader can refer to [Mur89] or to PN books such as [Rei13] for a more complete discussion of PN properties.

According to Murata [Mur89], there are two types of PN properties: those that depend on the initial marking  $M_0$ , called **behavioural properties**, and those independent of  $M_0$ , called **structural properties**. This works addresses only some of the behavioural properties.

A first important property is **reachability**. This is a fundamental property to study the dynamic properties of any system described by PNs. Reachability relies on the PN's *firing rules* and on the initial marking  $M_0$  of a PN. A marking  $M_n$  is said to be reachable from marking  $M_0$  if there exists a sequence of firings that transforms  $M_0$  into  $M_n$ . A firing or occurrence sequence is denoted by  $\sigma = M_0 t_1 M_1 t_1 M_2 \dots t_n M_n$ , or simply  $\sigma = t_1 t_1 t_2 \dots t_n$ . In this case,  $M_n$  is reachable from  $M_0$  by  $\sigma$  and we write  $M_0[\sigma > M_n$ . The set of all possible markings reachable from  $M_0$  in a PN  $(N, M_0)$  is denoted by  $R(N, M_0)$ , or simply  $R(M_0)$ . The set of all possible firing sequences from  $R_0$  in a PN  $R_0$  in a PN  $R_0$  is denoted by  $R_0$  in a PN  $R_0$  in a PN

A second property worth defining here is **boundedness**, related to the maximum amount of tokens a place of some PN holds. A PN  $(N, M_0)$  is said to be k-bounded or simply bounded if the number of tokens in each place does not exceed a finite number k for any marking reachable from  $M_0$ , i.e.  $M(p) \le k$  for every place p and every marking  $M \in R(M_0)$ . A PN  $(N, M_0)$  is said to be **safe** if it is 1-bounded. In (asynchronous) hardware design places of a PN are often used to represent buffers and registers for storing intermediate data. By verifying that the net is bounded or safe, it is guaranteed that there will be no overflows in buffers or registers, no matter what firing sequence is taken.

A last property needed to define in this work is **liveness**, associated to concepts in system design like absence of deadlocks. A PN  $(N, M_0)$  is said to be **live** (or equivalently  $M_0$  is said to be a live marking for N) if, no matter what marking has been reached from  $M_0$ , it is possible to ultimately fire any transition of the PN by progressing through some firing

sequence. This means that a live PN guarantees deadlock-free operation, no matter what firing sequence is chosen.

## 2.1.3 Marked Graphs

Marked graphs constitute a limited class of PNs that allows modelling concurrency, but not choice (to avoid e.g. non-determinism). This enables capturing the behaviour of handshaking circuits. A timed marked graph can capture not only the inter-dependency and concurrency in asynchronous circuits, but also the timing of certain events occurring within the circuit.

As a type of Petri net, marked graphs are bipartite graphs. Informally, a marked graph is a Petri net where each place has exactly one transition in its preset and exactly one transition in its postset. Also, a marked graph is guaranteed to be a safe Petri net, meaning that places can hold at most one token at any moment in time. These characteristics enable deriving a simple definition for a marked graph.

**Definition 2.1.4 (Marked Graph)** A marked graph is a 3-tuple  $MG = (T, P, M_0)$ , where T is the set of transitions,  $P \subset \{(u, v) : u, v \in T\}$  is the set of edges connecting transitions, and  $M_0 \subset P$  is the subset of edges initially marked (the initial marking). The marking  $M_i \subseteq P$  corresponds to the subset of places holding tokens at some given instant  $i \in \mathbb{N}$ . Of course, i = 0 corresponds to the initial state of MG, where the initial marking  $M_0$  in in place.  $M_i$  represents the state of MG at instant i.

Compared to a regular PN, MGs suppress the representation of places but marks still occupy their position, between transitions. In a marked graph, token movements (i.e. state changes) obey a deterministic causality relation formally defined, in this work called *token flow*.

**Definition 2.1.5 (Token Flow)** Let  $M_i$  be the marking of a marked graph MG at instant  $i \in \mathbb{N}$ . Let  $\bullet t = \{(u, v) \in P | v = t\}$  be the preset of transition t and let  $t \bullet = \{(u, v) \in P | u = t\}$  be the postset of transition t.

Then, it is true that  $\exists t \in T : \bullet t \subseteq M_i \implies \exists n \in \mathbb{N}_* : t \bullet \subseteq M_{i+n} \land \bullet t \nsubseteq M_{i+n}$ . This means that if all elements in the preset of a transition ( $\bullet t$ ) are marked, there is a moment in the future (i + n) where all elements in the postset of that transition ( $t \bullet$ ) will be marked and its preset  $\bullet t$  will be unmarked.

Transitions control the flow of tokens in a network through the firing process. As defined for any PN (MGs obviously included), when a transition fires, it removes tokens from all places in its preset and deposits tokens to all places in its postset. Said otherwise, when a

transition fires it simultaneously marks its postset and unmarks its preset. An MG transition can only fire after all edges in its preset are marked. Further limitations can be imposed as to when a transition is allowed to fire (including time counting and other conditions).

An useful extension of the MG concept is adding labels to account for time in either places and/or transitions, giving rise to the *timed marked graphs* or TMGs. The former is relevant to this work and is accordingly precisely defined.

**Definition 2.1.6 (Place-Delayed Marked Graph)** Given a marked graph MG, it is possible to define a **place-delayed marked graph** as a 3-tuple PDMG =  $(T, P, M_0)$ , where T and  $M_0$  are defined as in the corresponding MG and  $P \subset \{(u, v, d)|u, v \in T, d \in \mathbb{R}+\}$ . The edges, as in an MG, connect transition u to transition v, with a label d, representing the delay assigned to each edge.

A token flowing into a PDMG edge (u, v, d) experiences a delay d before enabling the firing of a transition. That is, once receiving a token, an edge (u, v, d) must remain marked at least for the duration d before the token is removed. As in any PN, a transition can only fire in a PDMG after all its predecessor edges are holding tokens. When a transition fires it removes the tokens from its predecessor edges and deposits tokens in all of its succeeding edges.

## 2.2 Handshake Protocols

Handshake protocols are characterised by two distinct steps: (i) **request**, when a transmitter announces data availability; (ii) data **acknowledgement**, when a receiver acknowledges data reception, allowing the transmission of new data. The implementation of these steps depends on a series of choices for specific actions on control signals. Figure 2.1 displays two possible handshake protocols performing complete handshake cycles.

Figure 2.1: Examples of handshake protocols: (a) 2-phase; (b) 4-phase.

Figure 2.1a presents a 2-phase, also known as edge-sensitive handshake protocol. In this protocol data availability and acknowledgement are determined by transitions ("edges") in control signals. It implements the request and acknowledgement steps in a cycle with 2 phases: (i) Data are placed in the *data* lines and, at the same time or immediately

afterwards a transition occurs on the *req*, announcing data availability; (ii) The transition of the **req** line triggers the consumer to capture the data, later acknowledging reception by transitioning the **ack** line.

Figure 2.1b presents an instance of a 4-phase, also known as level-sensitive, hand-shake protocol. In this protocol data availability and acknowledgement are indicated by logic levels in control signals. Handshakes take place in a cycle with two parts: (i) evaluation, when handshake signals are asserted; and (ii) reset, when the signals return to their inactive state before the next evaluation part starts. This results in data-exchange cycle with 4 phases: (i) data is placed in the *data* lines and, at the same time or immediately afterwards, the *req* line is raised to announce data availability; (ii) the consumer acknowledges the data arrival by raising the *ack* line; (iii) after recognising the rise of the *ack* signal, the producer resets the *req* signal; (iv) the consumer recognises the fall of the *req* signal by lowering the *ack* signal, thus completing the protocol reset stage and allowing a new transmission to take place.

The use of dedicated request/acknowledge signals separate from the data lines characterises what is traditionally called **Bundled Data** (BD) design style. The BD style allows simpler data path implementations, at the expense of timing constraints complexity. Since combinational logic transforming data must be transparent to the local handshake protocol [SF01], the request line must arrive to the consumer only after all computations on channel data is concluded, otherwise the consumer sequential barrier may capture incorrect data.

This poses a design challenge, as the request line may be required to be delayed with regard to data availability, to guarantee correct synchronisation. Such synchronisation is often achieved in the BD design style using delay-lines that match the delay of combinational logic in the data lines to the *req* logic generation circuit.

As an alternative, the request line can be encoded within the data itself, using some delay-insensitive encoding for data. This approach reduces the complexity of timing constraints and provides a more robust circuit implementation, at the cost of additional area. The next Section further explores this class of circuits, which will be the main target of this work.

## 2.3 Quasi-Delay-Insensitive Design

Synchronous design relies on the assumption that the value on the inputs of all its registers will only be sampled at the rising (and/or falling) edge of the clock signal. This assumption enables designers to define timing constraints for the maximum delay in logic paths, which must always be lower than the clock period. This allows ignoring gate and wire delays, as long as constraints are respected. In other words, combinational logic is allowed

to switch as it computes data during, say, the interval between two consecutive rising clock edges, but it must be stable and correct at each such edge. Having such a simple model for circuit design is possible only because the clock is a periodic signal, *i.e.* its edges only occur at specific and known points in time. Hence, in synchronous circuits, events will only take place at specific moments; time can thus be treated as a discrete variable.

However, in asynchronous circuits there is no such thing as a single clock to signal data validity on the inputs of all registers. In these, events can happen at any moment, and time must be regarded as a continuous variable. Thus, asynchronous designers rely on local handshake protocols for communication and synchronisation, and on different design templates to build circuits, each with its own specific assumptions about gate and wire delays [BOF10]. These templates can be classified in two main families: bundled-data (BD) [Sut89] and QDI [MN06]. The design of a BD circuit is similar to a synchronous one, the difference is that BD relies on carefully designed delay elements for matching the timing of logic paths and controlling registers, rather than having a clock signal. Communication and synchronisation are accomplished through handshake protocols. QDI, on the other hand, uses special data codes that allow data to carry their own validity information, enabling receivers to compute the presence or absence of data at inputs/outputs, and rendering possible the local exchange of information. Because of this characteristic QDI circuits can adapt more gracefully to wire and gate delay variations.

QDI design relies on delay-insensitive (DI) codes [Ver88], which include codewords for valid data, and a special codeword representing the absence of data. The latter codeword is usually called a **spacer**. Figure 2.2 shows a basic transition diagram for transmitting data on a 1-bit QDI channel. Assume transmission always starts with a spacer (S). A transition from the S codeword to 1 (0) characterises the transmission of a valid 1 (0) and a transition from 1 (0) to S characterises the removal of data. Thus, there is always a spacer between any pair of consecutive data values.

Figure 2.2: The basic transition diagram for transmitting binary data in a QDI channel, where S stands for the spacer. Adapted from [MBSC18].

In circuit design, often used examples of DI codes are the k-of-n codes, where  $\bf n$  is the number of wires used to represent data (or its absence) and  $\bf k$  is the number of wires that must be at a given logic value for the codeword to represent valid data. Note that an acknowledge signal is typically required to control the injection of spacers and valid data in a QDI channel. Albeit different codes are available in the contemporary literature (see

e.g. [Ver88]), according to Martin and Nyström [MN06], the most practical class of DI codes is the **1-of-n** (or one-hot), and more specifically the **1-of-2** code. The latter is the basis to form codes to represent any n-bit information using two wires to denote each of the n bits, producing the so-called **dual-rail** code. Besides data encoding QDI design usually implies a choice of either a 2-phase or a 4-phase communication protocol [MN06]. The majority of QDI designs available in the state-of-the-art, from networks-on-chip [BCV+05, PMMC10], to general purpose processors [MNW03], and network switches [DLD+14] primarily rely on a 4-phase protocol and dual-rail or 1-of-4 codes. This work focus attention on 4-phase, dual-rail QDI design.

In a 4-phase dual-rail DI channel D, a single bit datum is represented using two signals, D.1 and D.0 that carry the datum value, and one signal ack to control data flow. For the data portion of a channel, as Figure 2.3a depicts, a spacer is classically encoded as a codeword with all signals at 0. Valid data are encoded using exactly one signal at 1, D.1=1 for a logic 1 and D.0=1 for a logic 0. In this case, both signals at 1 is a codeword that does not correspond to any valid datum and is not used. Figure 2.3b shows an example of data transmission using this convention to demonstrate the control flow allowed by the ack signal combined to codewords represented in signals D.1 and D.0. In this example a sender provides dual-rail data in D.1 and D.0 to a receiver that acknowledges received data through ack. Communication starts with a spacer, all signals at 0. Note that the ack signal also starts at 0, as the receiving side is ready to receive new data. Next, the sender puts a valid 0 bit in the channel, by raising the logic value of D.O, which is acknowledged by the receiver raising the ack signal. After the sender receives ack, it produces a spacer to end communication, bringing all data signals in the channel back to 0. The receiver then lowers its ack signal, after which another communication can take place. Due to its nature, which requires all signals to go to 0 before each data transmission, this 4-phase protocol is also known as return-to-zero (RTZ).

Figure 2.3: RTZ dual-rail channel operation: (a) encoding; (b) example waveforms. Adapted from [MBSC18].

Another 4-phase protocol for dual-rail QDI design is the return-to-one (RTO) protocol [MGC12]. RTO employs the same amount of valid codewords as an equivalent RTZ, but its data values are inverted compared to the latter. As Figure 2.4a shows, a spacer here is the codeword with all signals at 1 and valid data is represented by one signal at 0, *D.1*=0 for a logic 1 and *D.0*=0 for a logic 0. Figure 2.4b depicts an example RTO data transmission,

which starts with all signals at 1 in the data channel. As soon as the sender puts valid data in the channel, the receiver may acknowledge it by lowering *ack*. Next, all data signals must return to 1 to denote a spacer, ending transmission. When the spacer is detected by the receiver, it raises the *ack* signal and new data can follow. The idea behind the RTO protocol is simple but powerful and allows a better design space exploration for QDI circuits, enabling optimisations in power [MGC12] and robustness [MGHC14]. Furthermore, as demonstrated in [MPC14], RTZ and RTO can be mixed in a same QDI design and the conversion of values between them requires only an inverter per wire. According to Martin and Nyström, in [MN06], such conversion is DI and does not compromise the robust functionality of a QDI circuit. This article refers to signals operating under the RTZ (RTO) protocol as RTZ (RTO) signals.

Figure 2.4: RTO dual-rail channel operation: (a) encoding; (b) example waveforms. Adapted from [MBSC18].

## 2.4 Static Timing Analysis

Timing analysis is an important step in digital circuit design, since establishing the circuit performance under certain operating conditions is often one of the main project requirements. Historically timing is analysed using electrical simulation, this is called Dynamic Timing Analysis (DTA). It relies on stimulating every possible path of electrical-level model of the circuit being tested and measuring the time elapsed until a stable output is given. However, this type of analysis is computationally expensive and relies on a good source of stimuli to cover every possible path.

Alternatively, Static Timing Analysis (STA) provides a cheaper alternative to analysing the timing of the circuit globally through simulation. It relies on delay models of small components of the circuit, e.g. logic gates. These delays models are used to estimate the delay of every possible timing path in the circuit. This avoids the coverage problem and is less computational intensive, allowing the use of STA on much larger circuits.

The delay models of components are created using electrical simulation in a process called characterisation. A delay model of a component captures characteristics of arcs. An arc is a timing path internal to a component, it captures how changes in a input affects

the circuit. There are three types of arcs: (i) hidden arcs, where a change in input does not affect any output; (ii) transition arcs, where a change in input causes a transition in the output; and (iii) constraint arcs, which are limitations of when an input can change. As an example, the propagation arcs of an OR gate are shown in Figure 2.5a. Each dashed line represent two propagation arcs, one for the rise and another for the fall of the output Z.

A possible model is the non-linear delay model (NLDM), which is composed of tables that capture characteristics for each arc based on the input slew and output capacitance. Some characteristics captured by the NLDM tables are: (i) slew rate, the time an output takes to finish transitioning once it starts; (ii) propagation delay, the time a transition in an input propagates to the output; (iii) power consumption, the energy consumed by a transition in the arc. The delay model of a component also captures the capacitance of pins.

The timing paths are acyclic with well defined start and end points. A timing path is composed by a chain of arcs. Transitions propagate in these paths thru arcs, due to this characteristic a timing path is also called a **propagation path** throughout this work. Figure 2.5b shows a circuit implementing a XOR gate using two inverters and three NAND gates. The timing arc relating the fall of the output Z when the input A rises is highlighted. A rise transition in A activates an arc of g0 which produce a fall transition in its output, in turn this transition activates an arc of "g2" that causes a rise in its output, which finally activate an arc of g4 that cause a fall transition in the primary output Z.

Figure 2.5: Timing models used by the STA engine: (a) gate timing arcs; (b) timing paths.

From the information contained in the delay model, it is possible to analyse the timing paths of circuits. The STA engine computes the delay of the timing paths with the following sequence of steps: First the capacitance of each net is computed based on the components connected to it, the capacitance of primary outputs are provided as a parameter. The STA engine then creates an acyclic directed graph containing all possible timing paths in the circuit from the circuit netlist and propagation arcs. For each arc in the graph, the STA engine uses the slew information in the delay model to compute the slew rate of every possible transition, the slew of the primary inputs are provided as a parameter. Once

the capacitance and slew rate are computed, the STA engine is able to use the propagation arcs of the delay models to compute the time each transition occurs in the timing path.

On synchronous sequential circuits, the timing paths are bounded by clock events. The start point of each path is either a primary input or the output of a clocked sequential element. Also, the end point is either an primary output or the input of a clocked sequential element.

The clock provides a periodic time reference which can be used to compute the timing of the circuit. Primary inputs are assumed to be synchronous to clock events and sequential elements produce new values on clock events. This implies that a clock event triggers a sequence of transitions in propagation paths. The time between the first and the last transition in the propagation path is called its propagation delay of that path.

A more comprehensive background on STA lays beyond the scope of this Dissertation. The interested reader may consult works like that of Harris "Skew-Tolerant Circuit Design" [Har01].

#### 3. THE PSEUDO-SYNCHRONOUS SDDS-NCL DESIGN TEMPLATE

The timing of propagation paths in a digital circuit can be computed using STA. Commercial EDA tools attempt to find and optimal solution that respects the timing budget while balancing power and area consumption. Also, during physical implementation, STA enables an optimal placement of gates in the layout, guaranteeing that wire delays do not compromise the circuit functionality. On synchronous flop-based circuits, the clock period bounds the delay of propagation paths between two registers. The last transition in each path must occur a certain time prior to the clock edge for the circuit to work correctly.

The pseudo-synchronous flow enables us to define a pseudo-clock period, analogous to a clock period of a synchronous flop-based circuit. This pseudo-clock can then be used to constrain the delay of propagation paths between two registers. The SDDS-NCL design template leverages standard EDA to synthesise and optimise combinational QDI circuits. This Chapter introduces the Pseudo-Synchronous SDDS-NCL, a QDI template that combines and extends both SDDC-NCL and the Pseudo-Synchronous flows. This enables the synthesis and optimisation of sequential asynchronous circuits with constrained propagation paths using commercial EDA tools.

# 3.1 The SDDS-NCL Asynchronous Design Template (Related Work)

NCL is an asynchronous design template to construct QDI circuits – Nowick and Singh present a good summary of this and other templates in [NS15a, NS15b]. Fant and Brandt proposed NCL in [FB96], targeting RTZ 1-of-n schemes. It was the technology used for industrial designs produced by Theseus Logic in the late 90s. Since then, NCL has been explored by different research groups and employed for different applications, typically focusing on low power and robust design [JSL+10, CCGC10, SCH+11, ZSD10, GLY10]. NCL assumes a semi-custom design method, and relies on a basic set of components designed at the cell level, called *NCL gates*. As Fant and Brandt discuss in [FB96], these gates allow the construction of logic blocks that ensure the *completeness of input* criterion, which enforces that a logic block only produces a spacer (valid data) in its outputs when all its inputs have a spacer (valid data). The authors state that this is the key to ensure DI operation.

NCL gates are often called *threshold gates*, but this is imprecise, because they do not exactly implement threshold logic functions (TLFs) as defined, e.g. in [Hur69]. Rather, these gates implement modifications of such TLFs coupled to specific mechanisms to ensure the completeness of input criterion [FB96]. Before defining TLFs, a useful concept is that of unate functions [BSVMH84], as all TLFs are unate [Hur69]:

**Definition 3.1.1** A Boolean function  $f(x_1, x_2, ..., x_n)$  is said to be **positive unate** in  $x_i$  ( $1 \le i \le n$ ), if  $\forall x_j$ ,  $i \ne j$ ,  $f(x_1, ..., x_{i-1}, 1, ..., x_n) \ge f(x_1, ..., x_{i-1}, 0, ..., x_n)$ . Similarly, f is called **negative unate** in  $x_i$  if  $\forall x_j$ ,  $i \ne j$ ,  $f(x_1, ..., x_{i-1}, 0, ..., x_n) \ge f(x_1, ..., x_{i-1}, 1, x_{i+1}, ..., x_n)$ . If a function is neither positive unate nor negative unate in  $x_i$ , it is said to be **binate** in  $x_i$ . Moreover, if a function is positive or negative unate in all its variables it is called a **unate function**. A unate function that is positive (negative) unate in all its variables is called a **positive** (negative) unate function. Also, this dissertation calls **positive** (negative) unate gates those that implement positive (negative) unate functions.

**Definition 3.1.2** An *n*-variable **threshold logic function (TLF)**  $\tau$  *is an n*-variable unate function defined by a **threshold value**  $T \in N^*$  and **weights**  $w_i \in N^*$  assigned to each of its variables  $x_i$  such that:

$$\tau = \begin{cases} 1, & \sum_{i=0}^{n-1} w_i x_i \ge T \\ 0, & \sum_{i=0}^{n-1} w_i x_i < T \end{cases}$$

(3.1)

Hurst [Hur69] defines threshold gates with the threshold and weights being real numbers. This work restricts attention to non-zero, natural threshold and weights. TLFs can be either negative or positive unate in a given input – but not binate. However, to ensure the completeness of input criterion, NCL gates must be positive unate in all their inputs, as they target RTZ templates, where data validity is given by wires at 1. The OFF-set of a logic gate is the set of input patterns that force its output to 0. Analogously, the ON-set is the set of input patterns that force the output of a logic gate to 1. Because the spacer corresponds to all wires at 0, the OFF-set of an NCL gate includes just the condition where all inputs are 0.

As Fant and Brandt discuss in [FB96], while a QDI logic block is transitioning between a spacer and valid data, output values of the block should be either a spacer or valid data. Therefore, NCL gates must also account for situations where an input combination is neither in the ON-set nor in the OFF-set. In these no gate output should transition. This leads to the definition of the correct behaviour for NCL gates.

**Definition 3.1.3** An *n*-input **NCL gate** is a logic gate with a threshold value  $T \in N^*$ , a weight  $w_i \in N^*$  assigned to each variable  $x_i$  (i = 1, ..., n), and a hysteresis mechanism such that the gate output Q at each instant of time t is given by:

$$Q_{t} = \begin{cases} 1, & \sum_{i=1}^{n} w_{i} x_{i} \geq T \\ 0, & \sum_{i=1}^{n} x_{i} = 0 \\ Q_{t-1}, & 0 < \sum_{i=1}^{n} w_{i} x_{i} < T \end{cases}$$

(3.2)

Figure 3.1a shows a generic NCL gate symbol, where *n* is the number of inputs of the gate and T is the threshold of the TLF it implements, for which each input has a weight

$w_i$ . If a weight  $w_i$  is omitted,  $w_i = 1$  is assumed. Weights come after the W specifier. As an example, Figure 3.1b shows the symbol of a 3-input NCL gate with threshold 3 and weights 2, 1 and 1 (in the order from the topmost input down). Figure 3.1c shows the truth table for this latter example, computed from Equation (3.2). Accordingly, the output of the gate only switches to 0 when all inputs are at 0. Also, because  $x_1$  has weight 2,  $x_2$  and  $x_3$  have weight 1 and the threshold is 3, the gate only switches to 1 when  $x_1$  is at 1 and at least one of the other inputs is at 1. In all other cases the output remains unchanged.

Figure 3.1: Characteristics of NCL gates: (a) generic symbol; (a) generic symbol; (b) specific symbol example; (c) example truth table behaviour.

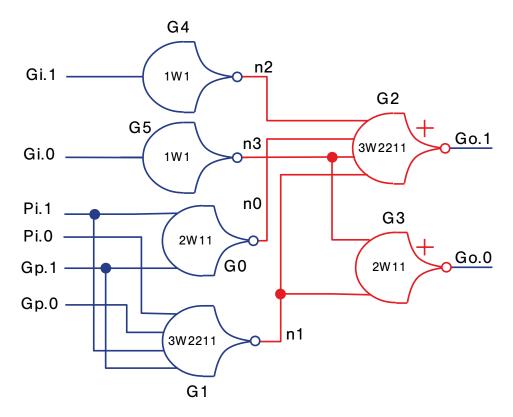

It is possible to build classic Boolean logic blocks with NCL gates, as Figure 3.2 illustrates. This schematic shows a generate path circuit fragment for an RTZ dual-rail Kogge-Stone adder, taken from [MTMC14]. Note that this circuit only generates a spacer output when all dual-rail inputs ( $G_i$ ,  $P_i$ ,  $G_p$ ) have spacers. Recalling Figure 3.1, the output of an NCL gate only goes to 0 when all its inputs are at 0, which means that gates G0-G3 in Figure 3.2 only write a 0 in their outputs when all primary inputs have spacers. Also note that the outputs become valid data only when all inputs display valid data. Accordingly, n0 is 1 only if  $P_i$  and  $G_p$  are valid 1s (i.e.  $P_i$ .1 = 1 and  $G_p$ .1 = 1) and n1 is 1 only if  $P_i$  has a valid 0 and  $G_p$  has a valid 1,  $P_i$  has a valid 1 and  $G_p$  has a valid 0, or both  $P_i$  and  $G_p$  have a valid 0. In this way, n0 and n1 are valid only if the primary inputs  $P_i$  and  $P_i$  are valid. Similarly, gates G2 and G3, which generate the outputs of the logic block, have their inputs connected to n0, n1 and primary input  $P_i$ , and these gates only generate valid data when their inputs are valid.

Even though the classic definition of an NCL gate relies on TLFs for their ON-set, different works (e.g. [JN08, RST12]) report the usage of non-TLF positive unate functions. This work also considers such functions, but as exceptions to the definition. Since these do not agree with the given NCL gate definition, they are called *hysteretic functions*. Hysteretic functions can be described using three minterm sets: (i) the ON-set contain all minterms that

Figure 3.2: Example of an NCL implementation: the generate path of part of a Kogge-Stone adder. Adapted from [MTMC14].

force the output high; (ii) the OFF-set contains all minterms that force the output low;and (iii) the HOLD-set contain all minterms that hold the current output value.

NCL supports the design of RTZ QDI circuits and, to meet the requirements of associated templates, NCL gates are typically restricted to implement only positive unate functions. This limits the potential logic optimisations on NCL circuits and complicates achieving compatibility with conventional EDA tools. However, the introduction of RTO [MGC12] and the NCL+ gates described in [MOPC13] change this situation. NCL+ gates are similar to NCL gates, but, because they target RTO templates, they need to synchronise spacers encoded by all wires at 1 and compute valid data signalled by logic 0s, as Section 2.3 described. The definition of an NCL+ gate is straightforward.

**Definition 3.1.4** An n-input **NCL+ gate** is a logic gate with a threshold value  $T \in N^*$ , specific weights  $w_i \in N^*$  assigned to each variable  $x_i$  (i = 1, ..., n), and a hysteresis mechanism such that the gate output Q at each instant of time t is given by:

$$Q_{t} = \begin{cases} 1, & \sum_{i=1}^{n} \overline{x_{i}} = 0\\ 0, & \sum_{i=1}^{n} w_{i} \overline{x_{i}} \geq T\\ Q_{t-1}, & 0 < \sum_{i=1}^{n} w_{i} \overline{x_{i}} < T \end{cases}$$

$$(3.3)$$

The symbol of an NCL+ gate is similar to that of an NCL gate, but with a + sign on its top right corner, as Figure 3.3a shows. Figure 3.3b shows an example of an NCL+ gate with 3 inputs, threshold 3 and weights 2, 1 and 1. The truth table of this gate appears in Figure 3.3c. As its truth table shows, this gate output only switches to 1 when all inputs are at 1. Also, its output only switches to 0 when  $x_1$ , which has a weight of 2, and at least one of

the other inputs, both with weight 1, are at 0. For all other combinations of inputs, the gate keeps its output value. In these cases, the output only switches to 1 (0) when all inputs are at 1 (0).

Figure 3.3: Characteristics of NCL+ gates: (a) generic symbol; (b) specific symbol example; (c) example truth table behaviour.

As in NCL, NCL+ gates are also useful to build logic blocks. For instance, Figure 3.4 shows the NCL+ version of the same generate path of the Kogge-Stone adder from Figure 3.2. The circuit topology is exactly the same as that of the NCL version. In fact, the gate characteristics are the same. The only difference is that NCL+ gates replace NCL gates with the same number of inputs, thresholds and weights. Hence, all internal nodes and primary inputs and outputs follow the RTO protocol, instead of RTZ.

Figure 3.4: Example of an NCL+ implementation: the generate path of part of a Kogge-Stone adder. Adapted from [MTMC14].

The advent of NCL+ created the possibility of mixing NCL and NCL+ in a single circuit, because RTO protocol signals can be translated to RTZ protocol signals and vice-versa

[MPC14]. Recalling Section 2.3, the conversion of a signal from RTO to RTZ, or the other way around, only requires inverters, each of which implements a negative unate function. Thus, as discussed in [MTMC14], the mix of NCL and NCL+ enables the use of negative unate functions, which allows further optimisation opportunities and expands the design space of QDI circuits. For each positive unate NCL (NCL+) gate, a negative unate gate can be defined, where the latter has its OFF-SET defined as the ON-SET of the former. To differentiate negative unate gates from positive unate ones from Definitions 3.1.3 and 3.1.4, these are named *Inverted* NCL and NCL+ gates (or INCL and INCL+, respectively) and defined accordingly.

**Definition 3.1.5** An *n*-input **INCL** gate is a logic gate with a threshold value  $T \in N^*$ , specific weights  $w_i \in N^*$  (i = 1, ..., n), assigned to each variable  $x_i$  and a hysteresis mechanism such that the gate output Q at each instant of time t is given by:

$$Q_{t} = \begin{cases} 1, & \sum_{i=1}^{n} x_{i} = 0 \\ 0, & \sum_{i=1}^{n} w_{i} x_{i} \ge T \\ Q_{t-1}, & 0 < \sum_{i=1}^{n} w_{i} x_{i} < T \end{cases}$$

(3.4)

**Definition 3.1.6** An *n*-input **INCL+ gate** is a logic gate with a threshold value  $T \in N^*$ , specific weights  $w_i \in N^*$  (i = 1, ..., n), assigned to each variable  $x_i$  and a hysteresis mechanism such that the gate output Q at each instant of time t is given by:

$$Q_{t} = \begin{cases} 1, & \sum_{i=1}^{n} w_{i}\overline{x_{i}} \geq T \\ 0, & \sum_{i=1}^{n} \overline{x_{i}} = 0 \\ Q_{t-1}, & 0 < \sum_{i=1}^{n} w_{i}\overline{x_{i}} < T \end{cases}$$

$$(3.5)$$

From a functional point of view, the only difference between an NCL (NCL+) and an INCL (INCL+) gate is that their ON- and OFF-sets are swapped. However, they all still rely on a hysteresis behaviour to ensure the respect of QDI properties. To produce INCL/INCL+ gate symbols, a bubble is added to the output of the respective non-inverted gate symbol. Using inverted gates it is possible to convert signals from RTZ to RTO, and vice versa. Because each time an inverted gate is used the protocol changes (including the codeword to representing spacers), circuits using (I)NCL and (I)NCL+ gates are called *spatially distributed dual spacer NCL* (or SDDS-NCL) [MTMC14].

Figure 3.5 shows an example of SDDS-NCL circuit equivalent to the ones in Figures 3.2 and 3.4. As the figure shows, when the circuit inputs present spacers, it issues a spacer in its output. In this figure, all INCL gates have 1 in their outputs, which means that

the INCL+ gates have 1 in all their inputs and a 0 in their outputs. In other words, all first level wires (in blue) will be at 0 and all second level wires (in red) will be at 1. From this state, whenever the inputs become valid dual-rail data, exactly two of the INCL gates fire, setting their outputs to 0, which causes exactly one of the INCL+ gates to fire, setting its output to 1.

The two inverters *G4* and *G5* (1W1 gates) are required to ensure that all the inputs of gates *G2* and *G3* are in the same domain (RTO). Also, because there are only two levels of logic and all gates are negative unate, the inputs and outputs of this circuit must be RTZ. If the output was expected to be RTO, inverters should be added after gates *G2* and *G3*, or these gates could be mapped to NCL+ ones. In fact, different combinations of NCL, INCL, NCL+ and INCL+ gates can be explored, depending on the requirements for the circuit input and output channels.

Figure 3.5: Example of an SDDS-NCL circuit: the generate path for a Kogge-Stone adder. Adapted from [MTMC14].

Having available negative and positive unate cells to compose circuits enables the use of commercial tools to perform logic and physical synthesis steps. These tools allow exploring new automation degrees in technology mapping and further logic optimisations. However, conventional CAD tools cannot explicitly handle NCL and NCL+ gates, as these present the hysteresis behaviour, which cannot be naturally handled by such tools. To overcome this problem and leverage the optimisation and automation degrees allowed by EDA tools, [MBSC18] proposes a design flow for circuits based on the SDDS-NCL template. The flow presented by Moreira et al. supports logic blocks only, requiring the designer to split

sequential from combinational blocks and synthesise the latter in isolation. This Chapter later further extends the SDDS-NCL and the pseudo-synchronous [TBV12] design flows to support the fully automated synthesis of both combinational and sequential blocks.

The SDDS-NCL design flow comprises two steps: logic and physical synthesis. Both are based in the usage of *virtual libraries*, a concept similar to that of image libraries proposed for the Proteus asynchronous design flow [BDL11]. The virtual library (VL) concept builds upon the definition of virtual function (VF), presented herein.

**Definition 3.1.7** A **virtual function (VF)** is an n-input Boolean function associated with an n-input NCL, NCL+, INCL or INCL+ gate, called its support gate. The truth table of a virtual function f is defined as follows:

- 1. if the support gate of f is an NCL gate  $\theta$ , the ON-set of f is the same as the ON-set of  $\theta$ . The OFF-set of f comprises all other n-input patterns;

- 2. if the support gate of f is an NCL+ gate  $\phi$ , the OFF-set of f is the same as the OFF-set of  $\phi$ . The ON-set of f comprises all other f-input patterns;

- 3. if the support gate of f is an INCL gate  $\psi$ , the OFF-set of f is the same as the OFF-set of  $\psi$ . The ON-set of f comprises all other f-input patterns;

- 4. if the support gate of f is an INCL+ gate v, the ON-set of f is the same as the ON-set of v. The OFF-set of f comprises all other f-input patterns.

If the support gate of f is of types NCL or NCL+, f is a positive VF. Otherwise, f is a negative VF.

Note that each VF always has exactly one NCL and one NCL+ support gates or one INCL and one INCL+ support gates. Reference [MNM+14] provides the detailed description of a method to compute the support gates for VFs. As another consequence of Definition 3.1.7, all positive VFs are positive unate functions, but not all positive unate functions are positive VFs. Furthermore, all negative VFs are negative unate functions, but not all negative unate functions are negative VFs. Hence, all VFs are unate functions, but not all unate functions are VFs. As an example, consider the 3-input NCL gate 3W211 depicted in Figure 3.1. The reader can verify that the virtual function  $f_1$  for this gate can be expressed by  $f_1 = x_0.(x_1 + x_2)$ . Another example is the 3-input NCL+ gate 3W211 depicted in Figure 3.3 has a virtual function  $f_2$  expressible by  $f_2 = x_0 + x_1.x_2$ . As expected and can be verified, these VFs are positive unate.

**Definition 3.1.8** A virtual library (VL) is a library of cells such that their functions are modelled exclusively using VFs. In this way, it is guaranteed that synthesis tools will be able to handle a VL, as all VFs are unate functions. Two types of VLs exist, NCL VLs and NCL+ VLs.

- 1. An NCL VL is a VL composed exclusively by NCL and INCL gates modelled using VFs.

- 2. An NCL+ VL is a VL composed exclusively by NCL+ and INCL+ gates modelled using VFs.

## 3.2 Pseudo-Synchronous Weak-Conditioned Half Buffer (Related Work)

Weak-Conditioned Half Buffer or WCHB is a classical asynchronous QDI template used to build sequential asynchronous circuits [BOF10]. It assumes the use of a DI code (often, the dual-rail one) and allows constructing asynchronous pipelines where stages containing data are surrounded by stages containing spacers and vice-versa (originating the half buffer denomination, meaning a data token at each two stages).

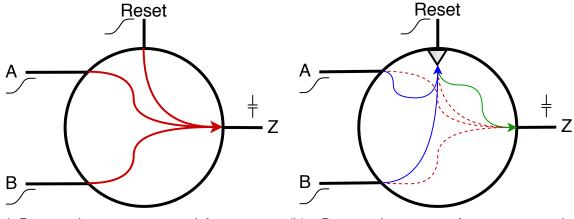

In [TBV12] Thonnart et al. compare the timing arcs of a resetable C-element, a basic building block of WCHB pipeline registers, to those of edge-triggered flip-flops, a basic building block of synchronous pipelines. From this analysis arises the proposal of pseudo-synchronous WCHB design technique, which relies on a clever modelling of asynchronous components and on standard static timing analysis (STA) tools to optimise sequential logic specifically for the WCHB QDI design template. They propose a modified, pseudo-synchronous (flop-like) model to represent resetable C-elements, building timing tables in the Open Liberty standard supported by conventional STA tools. The underlying reasoning is that conventional tools can analyse timing paths that start and end only at flip-flops, primary inputs, or primary outputs.

The Thonnart et al. model allows the analysis of paths that start and/or end in pseudo-synchronous flops without adding significant error to the actual delay of these C-elements. This work also details the specification of a pseudo-clock that guides the synthesis decision making process and constrains each logic stage during synthesis. Included is also a methodology to characterise pseudo-synchronous C-elements.

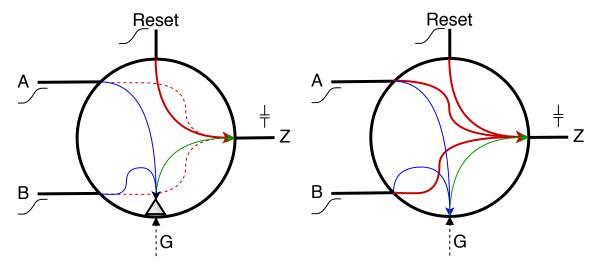

The original timing arcs of a C-element appear in Figure 3.6a, arcs from A, B to Z, and the arc from Reset to Z. These arcs are modelled as a function of the slew from an incoming transition in an input pin and the capacitance being driven by the output pin. In the model devised for use in the pseudo-synchronous flow, the arcs are modified to mimic those equivalent to a flip-flop (as in Figure 3.6b) [TBV12].

Here, the C-element Reset is transformed into a pseudo-clock pin and each of its original propagation arcs are split in two parts: (i) a clock propagation delay (in green), from Reset to Z (a function of the slew in Reset and of the capacitance in Z); and (ii) setup constraints (in blue), from A to Reset (a function of the slew in A and of the slew in Reset) and from B to Reset (a function of the slew in B and of the slew in Reset). Note that, since the sequential nature of the Reset pin is only a mechanism to create the pseudo-clock, its

(a) Propagation arcs extracted from a con- (b) Propagation arcs from a pseudo-ventional description.

Figure 3.6: Two arc models for a resetable C-element: (a) conventional description; (b) pseudo-synchronous description [TBV12].

slew is usually ignored. This way, the generated delay tables are a single row (or column) that depends only on the slew of A or B and on the capacitance driven by Z.

The reasoning behind this is that the original arcs can be constructed from the sum of a clock propagation delay and from a setup constraint of the Thonnart et al. model. For example, the original A to Z arc is represented by the propagation delay from Reset to Z added to the setup constraint from A to Reset.

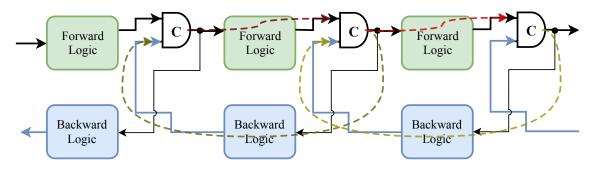

This way, every time the STA tool encounters a pseudo-synchronous flop model of a C-element, it identifies a new start point for paths that begin at output Z and a new end point for paths finishing at inputs A or B. This is crucial to enable STA in WCHB pipelines, as every pipeline stage is marked by the presence of a group of C-elements (e.g. 2 for a 1-of-2, 4-phase encoding, 1-bit data channel). The logic paths between these C-elements are optimised to meet the defined period (say  $\lambda$ ) of the pseudo-clock connected to the Reset pin.

For example, Figure 3.7 shows how these paths are analysed in a WCHB pipeline. It shows a single C-element composing the memory of each pipeline stage (hardly true in practice, due to the use of DI codes) and two types of logic paths: (i) the forward logic (usually where useful computation happens); and (ii) the backward logic (usually used for flow control). As the Figure shows, between every pair of C-elements in a cycle there are forward and backward logic paths that are constrained by a single pseudo-clock, with period  $\lambda$ , entering at the Reset pin (not shown). Furthermore, there are also paths between the input channel and the first C-element and the last C-element and the output channel.