# Assessing Rules in Memory Controllers with Hardware Simulator Executing Real Programs

Authors and affiliations omitted for a blind review process

*Abstract*— Electronic memories are subject to failure due to magnetic fields and radiation, causing temporary faults that can be mitigated by error correction codes. Evaluating the efficacy of these mechanisms in hardware can make the design more expensive, take a long prototyping time, and even lose time to market. Hardware simulators or emulators are often generic, requiring specific and specialized development to evaluate memory controllers. This work proposes Absimth to assess the computational system behavior in the presence of memory errors. Absimth is a hardware simulator focusing on memory controller data flow, allowing the creation and configuration of custom modules. The simulator aims to optimize the design of next-generation memory controller architectures, meeting fault tolerance requirements with fast validation before the hardware implementation phases.

Keywords— Hardware Simulator; Memory Controller; Fault Tolerance evaluation.

#### I. INTRODUCTION

Hardware reliability is a central requirement for highperformance computing and storage projects [1]. The memory reliability is particularly sensitive to variation in the manufacturing process, environmental conditions, or wear caused by the time of use [2][3]. Many areas are affected by memory errors, like (i) big service providers such as Facebook [4] with 2.5% per month and Google with 8% of memory modules per year [1]; (ii) personal computers turned on for 30 days have a 0.059% chance of failing, according to Microsoft [5]; and (iii) space projects, where it is common to use commercial memories due to their high density and low cost. However, commercial memories are not resilient to the numerous problems that can occur due to radiation, with the loss of cell functionality being the main consequence in intense radiation scenarios [6][7][8][9].

Fast and accurate simulation tools are essential for computer architects to analyze problems and compare the efficacy of each solution. It is even more critical to try a new set of constraints or incorporate an emerging technology with widely different properties than the standard technologies [10]. Computer system simulators are built for general purposes and cannot run native programs in general. Besides, there are few proposals regarding memory controller simulators, like FaultSim [10], whose operation is based on an analytical model.

This work proposes Absimth, an extensible fast memory controller simulator for improving studies of memory controller architectures used in various mobile devices to extreme-scale supercomputers. Absimth enables the behavior evaluation of the traditional applications over intense bitflips with different Error Correction Codes (ECC). To reach the behavior assessment, we simulated a homogeneous multiprocessor architecture composed of RISC-V 32I processors that access memory modules from a DDR4 SDRAM with ECC model MT40A1G16 from Micron [11], applying a synthetic application described in C. Absimth allows evaluating the ECC flow applied to memories; it enables configuring and creating custom modules for processors, memory devices, and memory controllers. Additionally, the simulator provides error injection models into memory for assessing the system behavior in the face of memory runtime faults with tons of metrics.

#### II. RELATED WORK

The design of general and specific purpose simulators is a significant research challenge, addressed over decades by several works. This section discusses some recent work and presents the motivation for proposing Absimth.

Nair et al. [10] proposed FaultSim, a configurable simulator to assess the reliability of memories, employing the Monte Carlo algorithm that generates pattern faults equivalent to the real world. The authors implemented and evaluated BCH-1 and Chipkill ECCs in real executions to validate FaultSim; the experiments show a deviation between 0.036% and 8.41%.

Dong et al. [12] presented a simulator to model Non-Volatile Memory (NVM) at the circuit level. The simulator evaluates timing, energy, and area consumption, supporting validating various NVM technologies, such as STT-RAM, PCRAM, ReRAM, and the traditional NAND FLASH.

Balasubramonian et al. [13] added a model to assess memory energy consumption to CACTI [14], allowing defining new interconnection types. The analysis has shown that the design parameters significantly impact energy consumption. A simple topology change can increase performance by 22% and reduce cost by 65%. Additionally, the article presents DDR3 and DDR4 designs that improve performance by 18% and reduce energy consumption by 23%.

Kim, Yang, and Mutlu [15] introduced Ramulator, a generic memory simulator that supports several standards like DDR3/4 LPDDR3/4, GDDR5, WIO1/2 HBM, and other academic proposals like SALP, AL-DRAM, ROW Clone, TL-DRAM, and SARP.

Mittal, Wang, and Vetter [16] presented Destiny, a tool to model, at the semiconductor level, the manufacturing process of 2D and 3D memories, such as SRAM, resistive STT-RAM, eDRAM, SOT-RAM, DWM, and flash. The simulator enables latency and area validation and provides comprehensive design modeling and spatial exploration. Destiny results were validated with several commercial prototypes, including the 2D and 3D designs of SRAMs and eDRAMs. The experiments presented less than 10% of modeling errors for most cases and less than 20% for all cases.

Chatterjee et al. [17] described the USIMM (Utah SIMulated Memory Module), an infrastructure for simulating DRAM memory, focusing on the energy consumption of the request schedulers that are part of the memory controller.

Wang et al. [18] developed MEMRES, a fast simulator to test the main memory reliability. MEMRES enables simulating memory failures, being computationally efficient in obtaining failure probabilities, and optimizing the memory system reliability. The authors performed a case study based on Spin-Transfer Torque Random Access Memory (STT-RAM); the results indicated that in-memory ECC could significantly mitigate the write error rate of STT-RAM.

Binkert et al. [19] proposed the gem5 simulator, a modular platform for researching computer system architecture, ranging from system level to processor microarchitecture. Gem5 is an open software project conceived initially for research into computer architecture in academia. Still, it has been used in academic works and industrial research by companies such as ARM, AMD, Google, HP, and Samsung.

Several works focus on the modeling and simulation of general-purpose computational systems, and some are dedicated to evaluating specific aspects of memories. Nevertheless, to the best of our knowledge, this is the first work on memory controller modeling and simulation focusing on fault tolerance. The Absimth simulator allows evaluation techniques and architectures of memory controllers, enabling the exploration of tradeoffs between error correction efficacy and implementation costs.

#### **III. ABSIMTH ARCHITECTURE DESCRIPTION**

This chapter details the Absimth simulator and the functionalities available to evaluate the behavior of memory controllers in a stressful environment.

#### A. Absimth Architecture

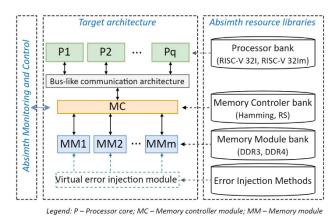

Fig. 1 displays a high-level description of Absimth for creating and configuring custom modules of processors, memory controllers, and a memory device split into memory modules. Absimth also disposes of a low complex Operating System (OS) for task management and a virtual module for simulating memory error injection.

Fig. 1. High-level description of the Absimth platform.

All modules described next have a standardized interface allowing them to be customized or changed.

#### Processor

Absimth includes the three following RISC-V 32-bit compatible processors [20] and allows executing several programs on single or multiple heterogeneous processors.

RISC-V 32I (32 bits and ISA composed by integer instructions);

- RISC-V 32Im (including multiplication and division instructions at the RISC-V32I), and

- RISC-V 32f (the same features of RISC-V 32Im but including floating point).

# **Memory Controller**

Absimth connects the processor and memory modules through customizable memory controllers and includes many types of memory controllers available, including or not ECCs; the available ECCs are Parity, Hamming, and Reed-Solomon.

# **Memory Device**

Absimth helps to create memory according to the user configuration, and OS accesses the memory devices using the memory controller address. The designer can navigate the memory hierarchy by examining any bit, byte, or word value of modules, rank, bank group, or each bank regarding any column, row, or height.

## **Error Injection Module**

Employing a virtual module for error injection, the designer can create several error scenarios based on the predefined templates, such as creating bitflip at random memory addresses in a given execution cycle. Absimth encompasses four error injection models based on [1][5] and a five-error injection based on error occurrence probability:

- *NoFaultError* meaning a memory without errors to assess the application execution time and amount of data transferred. It is the basis for comparing with other scenarios, occurring in about 91.78% of server cases [1][5].

- OneError implying a single bitflip to simulate the most common error scenario, occurring in approximately 8% of server cases [1][5]. This model makes the simulator generate an error at a specific address and bit position.

- *MultipleErrors* describing a memory with multiple corrupted bits to simulate scenarios representing from 0.044% to 0.066% of server cases [1][5].

- One2MultipleErrors one bit corrupted initially followed by multiple bitflips to simulate 0.154% to 0.176% of the multiple-error scenarios [1][5]. The simulator executes the OneError configuration; next, it performs the MultipleErrors format to evaluate the system behavior from one to multiple errors, one common memory scenario.

- *BitFlipProbability* enables to configure the following bitflip modes and probability rates: (a) probability rate of a bitflip occurring in every tick; (b) the maximum number of bitflips can occur in one cycle; (c) random or specific error address; (d) module memory subject to error occurrence; (e) the address distance between bitflip occurrence; (f) range allowed to bitflip inside the address (bit position range); (g) probability rate to generate a bitflip out of the address range; and (h) a seed for generating random errors.

# **Operating System**

Absimth implements a simple distributed OS that uses specific memory space; all data used by OS is neither passed nor allocated in the memory defined by the configuration. OS loads instruction from one task into memory per time or executes the instruction in application load mode. OS executes a specific number of user-defined instructions (quantum); once the quantum is completed, OS schedules the next task. Absimth employs a global Round-Robin with random-order task choices within each quantum as default scheduling. When the execution cycles reach the quantum defined by the user, OS saves the processor context, looks for the next task according to the scheduling algorithm, and loads its context into the processor. The current Absimth version does not allow disabling the default OS or implementing a customized OS.

#### Reports

At the end of the application execution, Absimth creates a simulation report containing the following information:

- Programs containing a list of programs executed, each one containing the (i) name and identification of the program, (ii) initial memory address, (iii) instruction length, (iv) initial data address, (v) stack size, (vii) a total of allocated memory used, (vii) last allocated address, (viii) first data address used, (ix) total of data address used, (x) last data address used, (xi) processor identifier (processor + core), (xii) processor number, (xiii) core number, (xiv) processor type, (xv) the total of cycles executed by the application, (xvi) task identification and (xvii) information if the program was executed with success.

- *Memory* comprising the number of instructions, data, and total reading and writing operations.

- Memory faults encompassing a list of physical memory addresses with error and the associated error type. An error injected is classified as INVERTED when the program execution does not access the error address; if the program accesses the error address, the error is classified as FIXED or UNFIXED, depending on the success of the error correction algorithm.

- *Memory controller* containing information about the numbers of memory read and write performed by the memory controller module.

- *Processor list* containing a list of processors with the (i) identification, (ii) type, (iii) core number, and (iv) number of the last tick executed.

- *General information* including (i) the entire simulation execution time (in milliseconds), (ii) the total number of ticks, and (iii) the maximum tick for each core.

# B. Absimth Execution Flow

The Absimth execution flow goes through two macro phases. The first phase, called Task Initialization, defines the simulator initialization activities; the second phase, called Task Simulation, implements the execution, insertion of errors, and application task monitoring.

## Task Initialization

Absimth initializes loading the application settings defined by the designer; in this step, the simulator allocates the memory areas of each task and maps these tasks to the processors of the target architecture.

The simulator checks the *PeripheralAddressSize* parameter, which contains the memory size allocated to each peripheral, allowing mapping peripherals into the memory addresses. Therefore, if the developer creates a specific module, the simulator allocates part of the memory address for this module operation. Afterward, Absimth loads the application tasks, forwarding the following items to OS: (i) the chosen processor identification and target architecture; (ii) task identification; (iii) total memory used according to the

stack size configured at program compilation time, and (iv) a reference for application loading.

# **Task Simulation**

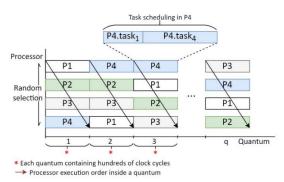

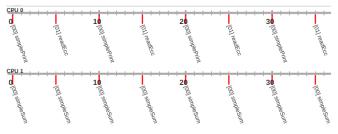

Fig. 2 displays that Absimth randomly selects the processor order execution inside a quantum - i.e., a predefined number of clock cycles, simulating random concurrency among processors. Although the order of processors is random, all processors must execute a quantum before starting a new random sequence of processor execution. After choosing the processor, OS schedules the task that must be executed in each processor. For each task in each processor, Absimth executes an instruction and waits for the next cycle.

Fig. 2. Example of Task Simulation phase encompassing four processors (P1...P4) execution during q quanta of simulation. This figure emphasizes intra-quantum scheduling of P4, covering task<sub>1</sub> and task<sub>4</sub>.

## IV. MEMORY BITFLIP OBSERVATION

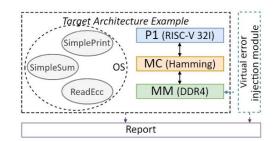

This section shows the memory bitflip observation processes, exemplifying three synthetic tasks executing in a single processor (Fig. 3). This processor is connected to a DDR4 through a memory controller that performs reading and writing operations using Hamming ECC.

Fig. 3. Target architecture and tasks employed in the simulation example.

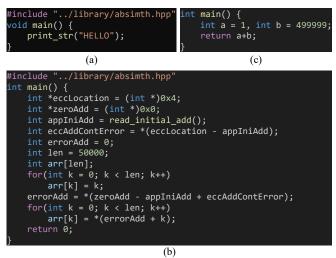

## A. Synthetic Application and Hardware Description

Fig. 4 describes SimplePrint, ReadEcc, and SimpleSum three synthetic low-complex tasks developed to observe the behavior of an application operating over a memory RAM with bitflip. Fig. 4(a) displays the small source code of the program SimplePrint, which only sends a message to the standard output. Fig. 4(b). shows the ReadEcc source code. The program starts by executing a loop to simulate reading and writing in the final position of the memory allocated for this task; since OS allocates the initial memory area for the program code and the final memory area for the program data. Subsequently, the program reads the information provided by the memory controller, informing which address has an error. This error information enables the beginning of reading the affected page, making the memory controller change the application encoding and OS transparently. Fig. 4(c) exhibits the SimpleSum source code, a simple program that sums and returns two values.

Fig. 4. Source code of three synthetic tasks: (a) *SimplePrint* (b) *ReadEcc*, and (c) *SimpleSum*.

Fig. 5 shows the Absimth configuration, encompassing (i) memory size reserved for hardware modules; (ii) processors used, in this case, two RISC-V 32i; (iii) memory configured with a DDR4 based on MT40A2G8 model [11] but with a smaller size, since for these applications require few kilobytes.

#### B. Memory Inspector

Absimth allows us to look in-depth at the processor status or memory during each execution or in the final process. Fig. 6 presents the *Memory Area Inspector*, exemplifying a memory data region. The memory information is grouped in 32 bits, with eight columns per line, for better screen use and to demonstrate a more significant amount of simultaneous data. Data containing errors are colored in red, in this case at address 0x3E8. When selecting an address, the rightmost column shows its physical breakdown. Consequently, in addition to the *Address* field, it shows the following fields: (i) *Module*, (ii) *Rank*, (iii) *Bank Group*, (iv) *Bank*, (v) *Row*, (vi) *Column*, and (vii) *Height* range. The simulator does not provide information on the chip, as each chip receives 1 byte.

| *        |          |          |           |          | itemory View by | Address  |          |          |                | - +               |

|----------|----------|----------|-----------|----------|-----------------|----------|----------|----------|----------------|-------------------|

| File     |          |          |           |          |                 |          |          |          |                |                   |

| Address  | x0       | x1       | x2        | x3       | x4              | x5       | хб       | x7       | Address        | Total: 0x00a12200 |

| 0x000300 | 0x000000 | 0x000000 | 0x0000000 | 0x000000 | 0x000000        | 0x000000 | 0×000000 | 0x000000 | Address        | 0x000003e8        |

| 0×000308 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 | Module         | 0                 |

| 0x000310 | 0x000000 | 0×000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 | Rank           | 0                 |

| 0x000318 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 | Bank Group     | 0                 |

| 0x000320 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0×000000 | 0x000000 | Bank           | 0                 |

| 0×000328 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 | Row            | 0                 |

| 0x000330 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 | and the second |                   |

| 0x000338 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 | Column         | 500               |

| 0x000340 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 | Height         | 0-8               |

| 0x000348 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x000350 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x000358 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x000360 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x000368 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x000370 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x000378 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x000380 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x000388 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x000390 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x000398 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x0003A0 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x0003A8 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0×000000 | 0x000000 |                |                   |

| 0x0003B0 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x0003B8 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x0003C0 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x0003C8 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x0003D0 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x0003D8 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x0003E0 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x0003E8 | 00000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x0003F0 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0x000000 | 0x000000 | 0x000000 |                |                   |

| 0x0003F8 | 0x000000 | 0x000000 | 0x000000  | 0x000000 | 0x000000        | 0×000000 | 0x000000 | 0x000000 |                |                   |

Fig. 6. Memory Area Inspector tool, containing an error in address 0x3E8.

Absimth provides the DDR memories default hierarchical model, enabling the designer to navigate throughout all the memory addresses, giving the spatial location. Besides, the designer can provide a customized memory structure by adjusting the memory template of Absimth.

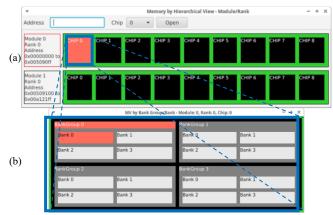

The spatial location is crucial to evaluate and simulate scenarios where memory has a location more susceptible to bitflips than other locations - e.g., the rightmost location of the memory is close to a heated area because of the processor place. Fig. 7(a) presents the highest memory level for navigating the structure of memory modules, ranks, and chips. The leftmost column reports the module number, rank, and addressing range. In case of an error in any data, the units are colored in red. It is possible to go into any chips to see the internal memory structure, exploring the error neighborhood in a three-dimensional (3D) format. The hierarchical view continues selecting a given module, rank, and chip. For instance, considering that chip 0 of module 0, rank 0 contains errors since it is colored in red in Fig. 7(a), Fig. 7(b) shows the visualization inside this chip, encircling the organization of memory banks inside each bank group.

Fig. 7. (a) The highest memory level, including memory modules, rank, and chips, showing that Chip 0, Module 0, and Rank 0, contain at least one bit with error; (b) Memory bank organization inside the bank groups. The Bank 0 of Bank Group 0 contains errors since it is colored in red.

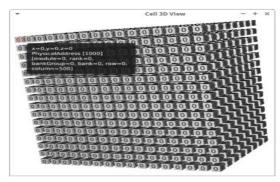

Fig. 8 displays the Absimth window when selecting the memory bank 0, which enables browsing the bank by memory address and physical cell placement - i.e., row, column, and height. The designer can also see the 3D view of a memory cell (along with height); Fig. 9 exemplifies a 3D view.

| Ŧ  |   |   |   |   |   |   |   |   |   |   | MV by | Cell |    |    |    |    |                  | -              |  |

|----|---|---|---|---|---|---|---|---|---|---|-------|------|----|----|----|----|------------------|----------------|--|

| x  | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10    | 11   | 12 | 13 | 14 | 15 | 6.11.2           | 30 x 1000      |  |

| 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  |                  |                |  |

| 1  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  | Cell Information |                |  |

| 2  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  | Cell Positi      | on 0 x 500 x 0 |  |

| 3  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  | Address          | 0x000003e8     |  |

| 4  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  | Module           | 0              |  |

| 5  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  | Rank             | 0              |  |

| 6  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  | Chip             | 0              |  |

| 7  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  | Bank Group       | 0              |  |

| 8  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  | Bank             | 0              |  |

| 9  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  | Bow              | 0              |  |

| 10 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  |                  | 500            |  |

| 11 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  | Column           |                |  |

| 12 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  | Cell Data Hexa   | 0x2c           |  |

| 13 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  | Cell Data Bits   | 00110100       |  |

| 14 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  |                  |                |  |

|    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0  | 0  | 0  | 0  | Height 0         | -              |  |

Fig. 8. Memory cell window; this view displays a single error on bit 0 (colored in red) of address 0x3E8.

Fig. 9. 3D memory cell preview window.

# C. Execution Investigation

The execution exemplification employs a memory controller with Hamming ECC and a virtual module generating a bitflip at address 0×3E8 to simulate a stuck bit. The *Processor Management* tool helps to watch the exact moment the instruction or data is corrupted and enables selecting a given processor and task. Each instruction of the assigned task can be executed step by step on the designated processor - the OS is bypassed in this execution.

Fig. 10 shows the *Processor Management* tool running *ReadEcc* on CPU\_0, covering the object code of the task, the status of the processor registers, and the memory address accessed at the instruction moment.

| *        |            | CF | 0 0    |                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 |

|----------|------------|----|--------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| File     |            |    |        |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| Register | Value      |    | CPU I  | readEccInformationFull | ÷                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| x0       | 0          |    |        |                        | Note that the second seco |   |

| ×1       | 8          |    | Next   | Run                    | Next Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| x2       | 1048576    |    | PC     |                        | Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

| x3       | 10         |    | 0      | lui x2 256             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| x4       | 0          |    | 4      | ial x1 x144            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| x5       | 0          |    | 8      | addi x11 x10 0         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| xб       | 0          |    | 12     | addi x10 x0 10         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| x7       | 0          | ~  | 16     | ecall                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| Address  | Data       |    | 20     | addi x2 x2 -32         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0×100019 | 0×100137   |    | 24     | sw x8 28(x2)           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0×10001A | 0x90000EF  |    | 28     | addi x8 x2 32          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0×10001B | 0×050593   |    | 32     | sw x10 -20(x8)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0×10001C | 0×A00513   |    | 36     | addi x10 x0 4          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0x10001D | 0x000073   |    | 40     | lw x11 -20(x8)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0×10001E | 0×FE010113 |    | 44     | ecall                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0×10001F | 0x812E23   |    | 48     | addi x0 x0 0           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0x100020 | 0x2010413  |    | 52     | lw x8 28(x2)           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0×100021 | 0xFEA42623 |    | 56     | addi x2 x2 32          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0×100022 | 0x400513   |    | 60     | jalr x0 x0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0×100023 | 0xFEC42583 |    | 64     | addi x2 x2 -32         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0×100024 | 0x000073   |    | 68     | sw x8 28(x2)           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0×100025 | 0×000013   |    | 72     | addi x8 x2 32          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0×100026 | 0x1C12403  |    | 76     | sw x10 -20(x8)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 0×100027 | 0×2010113  |    | 80     | addi x10 x0 1          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |