## PONTIFÍCIA UNIVERSIDADE CATÓLICA DO RIO GRANDE DO SUL FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

## RUNTIME ADAPTIVE QOS MANAGEMENT IN NOC-BASED MPSOCS

MARCELO RUARO

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Computer Science at Pontificia Universidade Católica do Rio Grande do Sul.

Advisor: Prof. Fernando Gehm Moraes Co-Advisor: Prof. Everton Alceu Carara

### Dados Internacionais de Catalogação na Publicação (CIP)

R894r Ruaro, Marcelo

Runtime adaptive QOS management in NOC-based MPSOCS / Marcelo Ruaro. – Porto Alegre, 2014.

89 p.

Diss. (Mestrado) - Fac. de Informática, PUCRS. Orientador: Prof. Fernando Gehm Moraes. Co-orientador: Prof. Everton Alceu Carara.

- 1. Informática. 2. Arquitetura de Computador.

- 3. Multiprocessadores. I. Moraes, Fernando Gehm. II. Carara, Everton Alceu. III. Título.

CDD 004.35

Ficha Catalográfica elaborada pelo Setor de Tratamento da Informação da BC-PUCRS

# Pontifícia Universidade Católica do Rio Grande do Sul FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

## TERMO DE APRESENTAÇÃO DE DISSERTAÇÃO DE MESTRADO

Dissertação intitulada "Runtime Adaptive QoS Management in NoC-Based MPSoCs" apresentada por Marcelo Ruaro como parte dos requisitos para obtenção do grau de Mestre em Ciência da Computação, aprovada em 26/02/2014 pela Comissão Examinadora:

| Firends John Moras                                       |                         |

|----------------------------------------------------------|-------------------------|

| Prof. Dr. Fernando Gehm Moraes –<br>Orientador           | PPGCC/PUCRS             |

|                                                          |                         |

| Prof. Dr. Everton Alceu Carara –<br>Coorientador         | UFSM                    |

| Prof. Dr. Ney Laert Calazans -                           | PPGCC/PUCRS             |

| Prof. Dr. Rodolfo Jardim de Azevedo –                    | UNICAMP                 |

| Homologada em.24./.04./2.014, conforme Ata Coordenadora. | a No. 006 pela Comissão |

Prof. Dr. Luiz Gustavo Leão Fernandes Coordenador.

DIICDO

**Campus Central**

Av. Ipiranga, 6681 - P32- sala 507 - CEP: 90619-900 Fone: (51) 3320-3611 - Fax (51) 3320-3621

E-mail: <a href="mailto:ppgcc@pucrs.br">ppgcc@pucrs.br</a> www.pucrs.br/facin/pos

#### **AGRADECIMENTOS**

Agradeço a minha família (meu pai Silvio, minha mãe Marinês, minha irmã Thaís e especialmente ao meu tio Nelson) por tudo, antes, durante e depois desse momento.

Agradeço ao meu orientador Prof. Fernando Gehm Moraes por me aceitar no Mestrado como seu "desorientando". Por ter a paciência de me explicar os conceitos da área de sistemas embarcados. Pela pontualidade nas orientações e disciplina nas cobranças, atitudes que certamente já me baseio em minhas atividades docentes. Pelo tempo passado depurando trechos de código em *Assembly* na memória. Pelas revisões de todos os volumes do PPGCC e artigos escritos e publicados. Enfim, por ser orientador.

Agradeço especialmente a minha namorada e meu amor Fabiana que me apoia, me inspira, me acalma e que foi muito paciente em minhas tarefas do mestrado.

Agradeço aos meus colegas do GAPH (Grupo de Apoio de Pesquisa ao Hardware), pelo companheirismo, pela ajuda prestada, e pelas discussões, que com certeza contribuíram na escrita desse documento.

Agradeço aos professores do PPGCC pelos ensinamentos e conhecimento transmitido ao longo do Mestrado.

Agradeço aos membros da banca avaliadora, do Mestrado e dos volumes anteriores (professores Ney, Afonso e Amory) pelas revisões a sugestões.

Agradeço ao meu coorientador Prof. Everton Alceu Carara, pelas revisões de textos e esclarecimento de dúvidas técnicas.

Agradeço também ao CNPq pelo suporte financeiro.

E quero prestar um agradecimento a Deus, que de uma forma muito misteriosa, tenho certeza que me ajudou a completar com calma essa caminhada.

Por fim, quero enfatizar minha felicidade por concluir mais essa importante fase em minha vida, rodeado por pessoas que estiveram comigo e me apoiaram. Sei que os desafios não devem acabar, por que aí a vida fica sem graça, e por isso estou iniciando uma nova fase (Doutorado) que certamente irá me fornecer muitas experiências e conhecimentos.

## GERENCIAMENTO ADAPTATIVO EM TEMPO DE EXECUÇÃO DE QOS PARA MPSOC BASEADOS EM NOC

#### **RESUMO**

Sistemas multiprocessados em chip (MPSoCs), baseados em redes em chip (NoCs), são resultados da contínua redução no tamanho dos transistores e na busca por um crescente poder computacional. Este aumento da capacidade de computação é alcançado através da replicação de componentes (processadores, memórias, roteadores, etc.), o que também fornece escalabilidade e simplifica o projeto. A estimativa de MPSoCs com elevado número de processadores acompanha a lei de Moore, e segundo o ITRS 2011 são previstos até 1000 elementos de processamento (PE) em um único chip até o ano de 2025. Esta estimativa é impulsionada principalmente pela mercado de telecomunicações e multimídia, que inclui dispositivos como *smarthphones* e computadores móveis. Este tipo de emprego de MPSoCs exige que tais sistemas sejam capazes de suportar uma variada gama de aplicações e com diversos requisitos de desempenho. Assim, o sistema deve ser capaz de fornecer qualidade de serviço (QoS) para as aplicações e ajustá-la em tempo de execução.

As propostas atuais da literatura visam fornecer adaptação de QoS em tempo de execução levando em consideração o uso de poucas ou de somente uma técnica de QoS. Observada a variedade de aplicações é claramente perceptível que certas aplicações possuem requisitos diferenciados de QoS, podendo requisitar mais recursos de computação, comunicação, ou ambos simultaneamente.

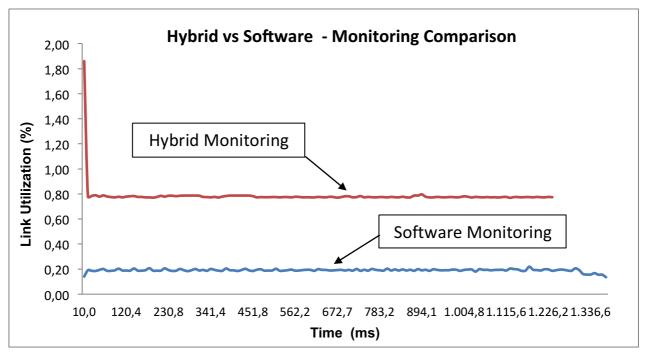

Portanto, este trabalho propõe explorar diferentes níveis de QoS através do uso de quatro diferentes técnicas adaptativas de QoS que são gerenciadas em tempo de execução de acordo com os requisitos das aplicações. O gerenciamento é distribuído através do particionamento do MPSoC em regiões, denominadas *clusters*, havendo um PE responsável pela gerência de cada *cluster*. Este gerenciamento adaptativo é realizado através de uma heurística que é executada em cada sistema operacional gerente de *cluster*. Uma infraestrutura de monitoramento híbrido fornece as informações necessárias para a heurística adaptativa. Esta infraestrutura é dividida em dois níveis hierárquicos, sendo escalável e com um nível de intrusão que corresponde no pior caso a 0,8% de utilização do enlace da NoC. O gerenciamento adaptativo de QoS em tempo de execução age na computação, comunicação ou em ambos e faz com que aplicações de tempo real flexíveis possam restaurar seu desempenho após detectado uma queda do mesmo pelo monitoramento.

Neste tralho é também proposta uma ferramenta de depuração para MPSoCs baseados em NoC, esta ferramenta fornece depuração no nível de protocolo de comunicação ente os PEs, e facilita o processo de implementação, validação e obtenção de resultados de novos protocolos para o sistema.

Palavras Chave: MPSoCs baseados em NoC, QoS, adaptação, monitoramento.

#### RUNTIME ADAPTIVE QOS MANAGEMENT IN DISTRIBUTED NOC-BASED MPSOCS

#### **ABSTRACT**

Multiprocessor systems on chip (MPSoCs), using networks on chip (NoC) as the communication infrastructure, result from the continuous reduction in the transistors size and the need for increasing computational power. This increased computing capacity is obtained through the reuse of components (processors, memories, routers, etc.), which also provides scalability, and simplifies the design process. MPSoCs with hundreds of processing elements (PEs) follows the Moore's law, and according to the ITRS 2011 it is predicted up to 1000 PEs in a single chip at the end of 2025. This estimation is driven mainly by the telecommunications and multimedia market, which includes devices such as smartphones and mobile computers. Such devices require systems able to execute a wide range of applications, with different performance requirements. Thus, the system must be able to provide quality of service (QoS) to applications, and adjust the resources usage at runtime.

Literature proposals provide runtime QoS adaptation taking into consideration the use of only one or two QoS techniques. Considering the application diversity that may execute in MPSoCs, applications may have different QoS requirements, requiring more computing resources, communication resources, or both simultaneously.

Therefore, this work aims to explore different QoS levels addressing four different adaptive QoS techniques managed at runtime according to the soft real-time applications' requirements. It is assumed that the MPSoC is partitioned in regions, named clusters, with one manager PE per cluster. This adaptive management is controlled through a heuristic that is executed by the OS of each cluster manager. A hybrid monitoring infrastructure provides the necessary information for the adaptive heuristic. This infrastructure is divided in two hierarchical levels, being scalable and with an intrusion level that corresponds, in the worst case, to 0.8% of the link utilization. The runtime adaptive QoS management acts in computing, communication, or both, enabling soft real time applications to restore their performance after detected a performance decrease by monitoring.

Furthermore, a debugging tool for NoC-based MPSoCs is proposed in this work. This tool provides a communication protocol level debugging, and helps the process of implementation, validation and extraction of results of new system protocols.

Keywords: NoC-based MPSoCs, QoS, adaptation, monitoring.

## **LIST OF FIGURES**

| Figure 1 – Distributed versus centralized MPSoC management                                      | 19     |

|-------------------------------------------------------------------------------------------------|--------|

| Figure 2 – Overview of the monitoring approach [FAR12]                                          | 25     |

| Figure 3 – Monitoring using watchdogs [SAI10]                                                   | 25     |

| Figure 4 – Overview of NoC monitoring infrastructure proposed in [FIO10]                        | 26     |

| Figure 5 – MNoC Overview of [ZHA11]                                                             | 27     |

| Figure 6 – Agents Hierarchies [FAR10]                                                           | 27     |

| Figure 7 - MPSoC Management Hierarchy [FAT11]                                                   | 29     |

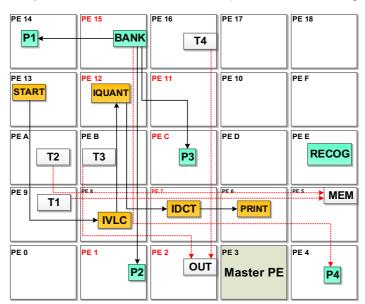

| Figure 8 – Overview of Distributed-HeMPS platform. The cluster-based management is the          | main   |

| feature                                                                                         | 35     |

| Figure 9 - Overview of QoS-HeMPS platform. The QoS support is the main feature of the platf     | orm.   |

|                                                                                                 |        |

| Figure 10 – QD-HeMPS Overview. QoS-HeMPS and Distributed HeMPS Integration                      | 37     |

| Figure 11 –Communication Model (MPI-like) adopted in the platforms                              |        |

| Figure 12 - Files used to describe the MPSoC platform                                           |        |

| Figure 13 - Simulation and debugging flow.                                                      | 44     |

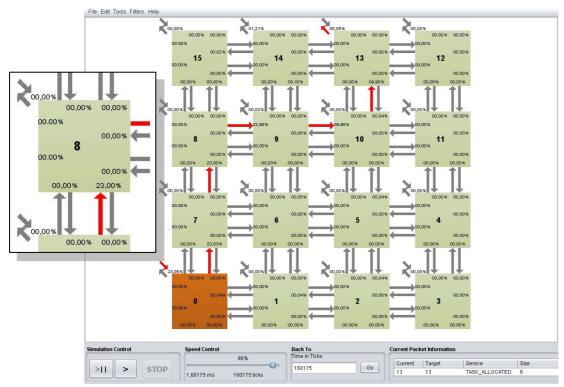

| Figure 14 - Throughput view GUI, for a 4x4 MPSoC, with duplicated physical channels. PEO i      | s the  |

| manager PE. Router 8 is highlighted, with an average link use of 23% in one of the south ports. | 44     |

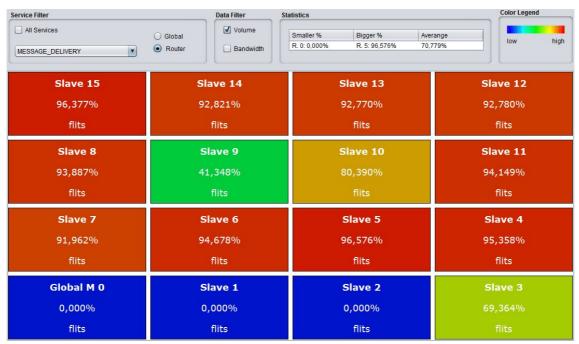

| Figure 15 - Load view for the message delivery service, evaluating the percentage of rece       | eived  |

| packets at each router corresponding to the reception of data packets                           | 45     |

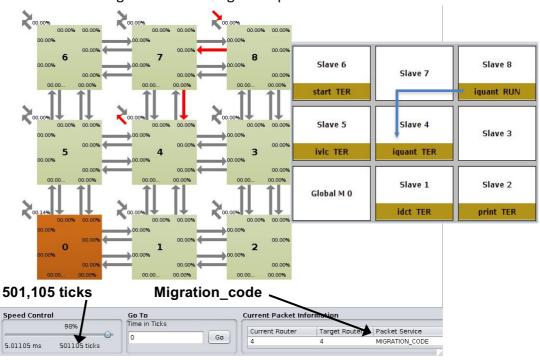

| Figure 16 - Mapping view, for a scenario with 7 applications. The OS running in the slave       | e PEs  |

| enable the execution of two simultaneous tasks. The Global PE manages the MPSoC                 | 46     |

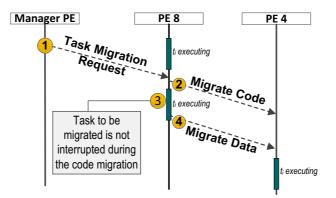

| Figure 17 - Task migration protocol                                                             | 47     |

| Figure 18 - Debug process for task migration protocol, with task iquant (MJPEG applica          | ition) |

| migrated from PE 8 to PE 4                                                                      | 47     |

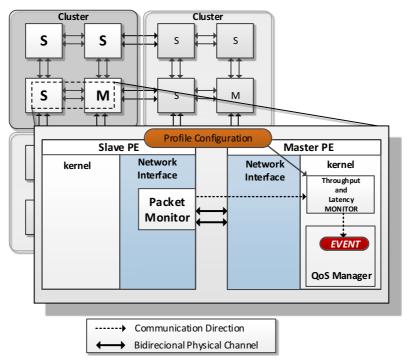

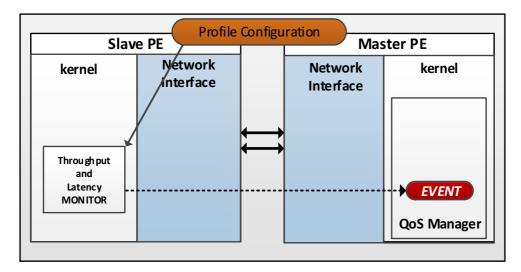

| Figure 19 - Proposed monitoring system. 'S' corresponds to slave PEs, and 'M' to master PEs     | 49     |

| Figure 20 – Example of task graph                                                               | 50     |

| Figure 21 – System call to configure task monitoring                                            | 50     |

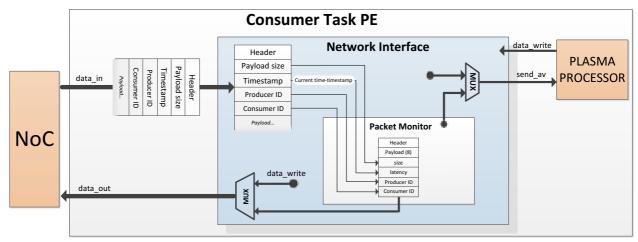

| Figure 22 – Packet Monitor Overview.                                                            | 51     |

| Figure 23 - Overview of software monitoring implementation                                      | 53     |

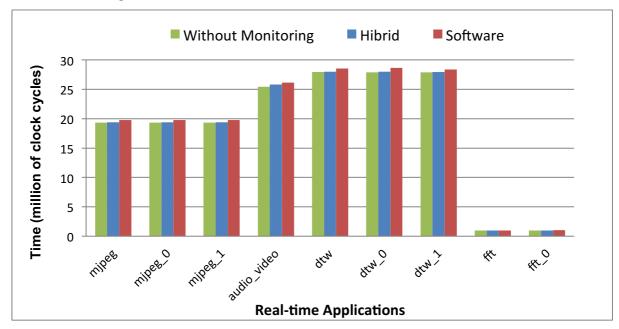

| Figure 24 – Execution time comparison in real scenario                                          | 54     |

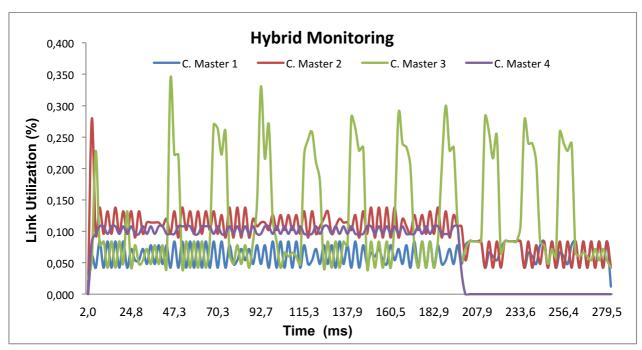

| Figure 25 – Hybrid Monitoring link utilization                                                  | 55     |

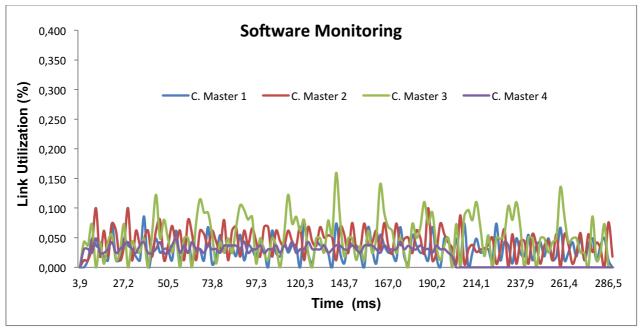

| Figure 26 – Software Monitoring link utilization.                                               | 55     |

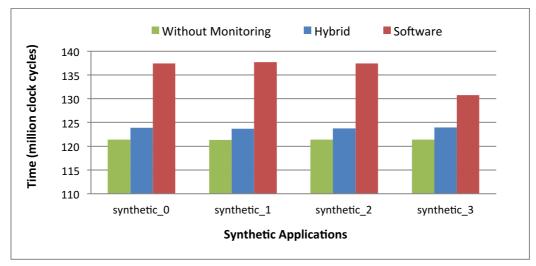

| Figure 27 – Execution time comparison in the synthetic scenario.                                | 56     |

| Figure 28 – Hybrid vs. Software monitoring comparison                                           | 56     |

| Figure 29 - Overview of QoS adaptation. The QoS Manager receives an event, chooses              | s the  |

| appropriated QoS technique, and sends the adaptation order to the Adaptation Module             | 59     |

| Figure 30 – Protocol to establishment and release of CS by QoS Manager                          | 60     |

| Figure 31 – Optimized task migration protocol.                                                  | 62     |

| Figure 32 – Overview of the Runtime Adaptive QoS Management                                     | 65     |

| Figure 33 – Pseudocode for the flow priority and CS adaptation                                  | 66     |

| Figure 34 – Time_Out_Monitor pseudocode                                                             | 67            |

|-----------------------------------------------------------------------------------------------------|---------------|

| Figure 35 - Non-optimal mapping of the synthetic applications, with the disturbing                  | applications. |

| Empty PEs are supposed to be allocated to other applications                                        | 69            |

| Figure 36 - Flow adaptation of the synthetic applications during execution. Each ho                 | orizontal bar |

| represents the flow state. The numbers above each bar indicate a change in the flow                 | state (in ms) |

|                                                                                                     | 69            |

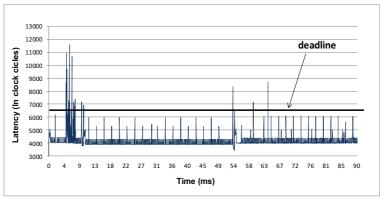

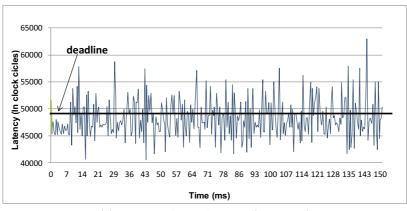

| Figure 37 – Latencies of the SR2 task with disturbing traffic. SR1 presents similar latence         | y results. 70 |

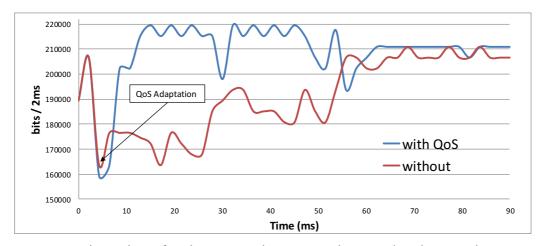

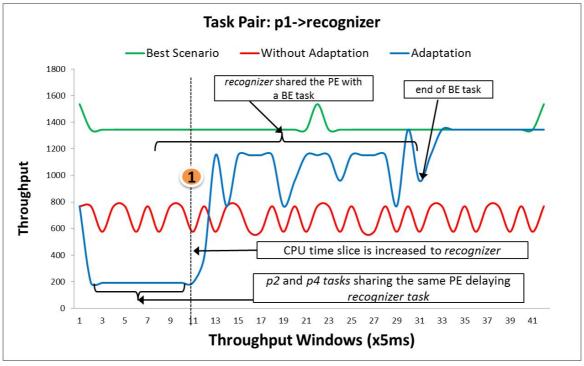

| Figure 38 - Throughput for the SR2 application, without and with QoS adaptation                     | 71            |

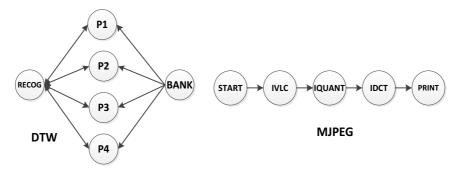

| Figure 39 – Task graphs for applications DTW and MJPEG                                              | 71            |

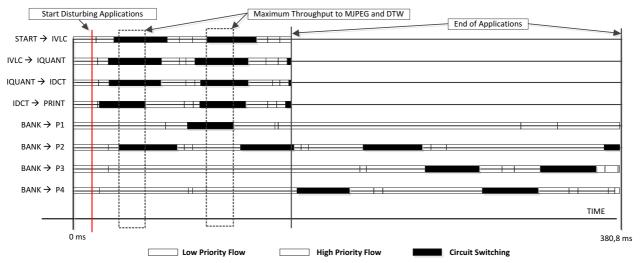

| Figure 40 - Flow adaptation of MJPEG and DTW applications during execution                          | 72            |

| Figure 41 - Non-optimal mapping in a 5x5 MPSoC instance, with MJPEG and DTW                         | applications  |

| running with disturbing applications. Empty PEs are supposed to be allocate                         | d to other    |

| applications                                                                                        | 72            |

| Figure 42 - Latencies of the PRINT task with disturbing traffic                                     | 73            |

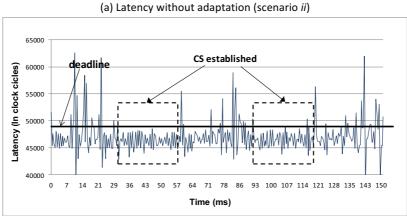

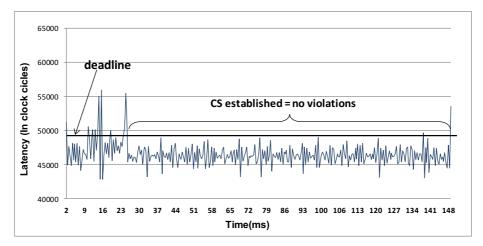

| Figure 43 - Latencies of the PRINT task with disturbing traffic, with CSt set to a value $\epsilon$ | quivalent to  |

| the application execution time                                                                      | 74            |

| Figure 44 - Latencies of the P4 task with disturbing traffic                                        | 75            |

| Figure 45 – ChangeQoSComputation pseudocode                                                         | 76            |

| Figure 46 – Task graph of audio_video and FFT applications                                          | 77            |

| Figure 47 – Execution time of RT applications                                                       | 78            |

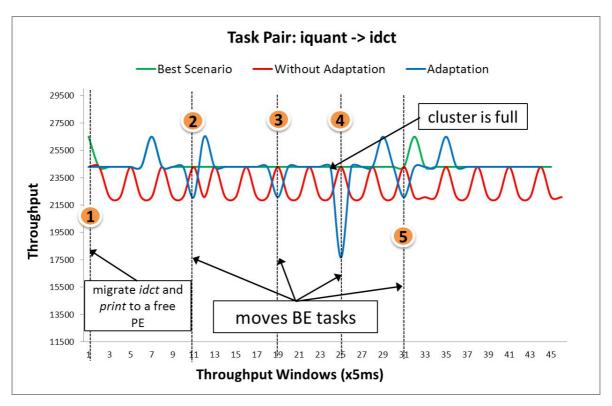

| Figure 48 – Throughput results for the communicating task pair iquant $\rightarrow$ idct            | 79            |

| Figure 49 – Adaptation cluster steps for the MJPEG application                                      |               |

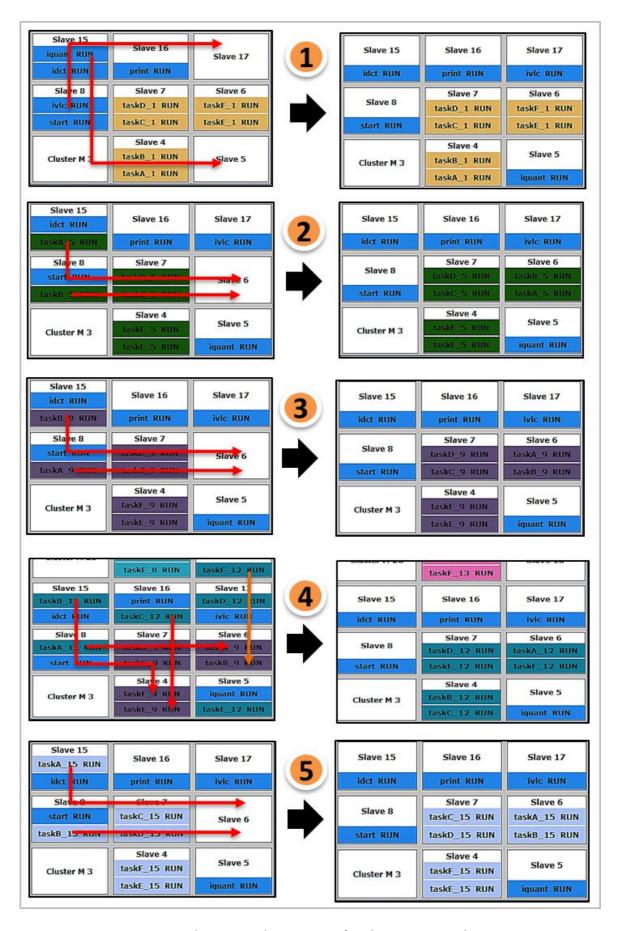

| Figure 50 - Throughput results for the communicating task pair bank->p2                             | 82            |

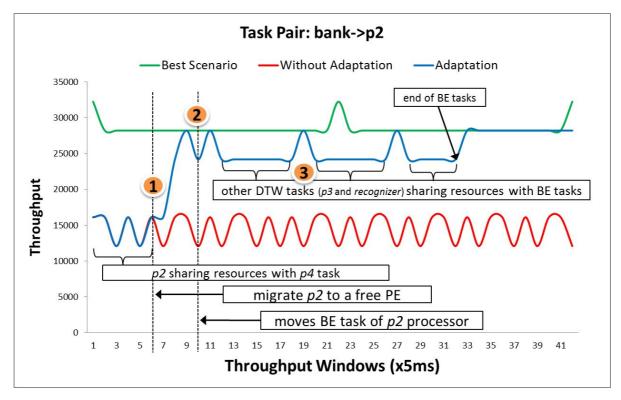

| Figure 51 – Throughput results for the communicating task pair p1->recognizer                       | 83            |

## **LIST OF TABLES**

| Table 1 - State-of-the-art comparing works targeting monitoring support in NoCs | 30 |

|---------------------------------------------------------------------------------|----|

| Table 2 - State-of-the-art comparing works targeting QoS support in NoCs        | 33 |

| Table 3 – Packet Monitor area overhead                                          | 52 |

| Table 4 - Effect of QoS techniques in communication and computation             | 58 |

#### **LIST OF ACRONYMS**

API Application Programming Interface

ASIP Application Specific Instruction Set Processors

CA Cluster Agent

CM Cluster Manager

CPU Central Processing Unit

CS Circuit Switching

DMA Direct Memory Access

DSP Digital Signal Processor

DTM Dynamic Thermal Management

DTW Dynamic Time Warping

DVFS Dynamic Voltage and Frequency Scaling

FFT Fast Fourier Transform

FPGA Field Programmable Gate Array

GA Global Agent

GPP General Porpoise Processor

GPU Graphical Processor Unit

GS Guaranteed Service

GT Guaranteed Throughput

GUI Graphical User Interface

IP Intellectual Property

ISA Instruction Set Architecture

ITRS International Technology Roadmap for Semiconductors

MEP Monitor Executive Processor

MNoC Monitor Network on Chip

MPI Messaging Passing Interface

MPSoC Multi-Processor System on Chip

NI Network Interface

NoC Network on Chip

OCP Open Core Protocol

OS Operating System

PE Processing Element

PLB Peripheral Local Bus

PMU Probes Management Unit

PS Packet Switching

QoS Quality of Service

RT Real Time

RTL Register Transfer Level

SDM Spatial Division Multiplexing

TA Tile Agent

TCB Task Control Block VC Virtual Channel

VHDL VHSIC Hardware Description Language

## **TABLE OF CONTENTS**

| 1 | INT  | FRODUCTION                                                             | 17 |

|---|------|------------------------------------------------------------------------|----|

|   | 1.1  | MPSoC                                                                  | 17 |

|   | 1.2  | NoC                                                                    | 18 |

|   | 1.3  | DISTRIBUTED RESOURCE MANAGEMENT                                        | 18 |

|   | 1.4  | QUALITY OF SERVICE                                                     | 19 |

|   | 1.5  | Monitoring                                                             | 21 |

|   | 1.6  | MOTIVATION                                                             | 21 |

|   | 1.7  | GOALS                                                                  | 22 |

|   | 1.8  | Contributions                                                          | 22 |

|   | 1.9  | DOCUMENT ORGANIZATION                                                  | 22 |

| 2 | STA  | ATE OF THE ART                                                         | 24 |

|   | 2.1  | Monitoring                                                             | 24 |

|   | 2.2  | QUALITY OF SERVICE                                                     | 31 |

| 3 | REF  | FERENCE PLATFORM                                                       | 35 |

|   | 3.1  | Distributed-HeMPS                                                      | 35 |

|   | 3.2  | QoS-HEMPS                                                              | 36 |

|   | 3.3  | DEVELOPED PLATFORM: QD-HEMPS                                           | 37 |

|   | 3.3. | 1.1 Tasks Communication                                                | 38 |

| 4 | DEE  | BUGGING TOOL FOR MPSOCS                                                | 40 |

|   | 4.1  | MPSoC Architecture Assumptions in the context of the debug environment | 41 |

|   | 4.2  | Packet Logger                                                          | 42 |

|   | 4.3  | DEBUG ENVIRONMENT                                                      | 43 |

|   | 4.4  | Throughput View                                                        | 44 |

|   | 4.5  | LOAD VIEW                                                              | 45 |

|   | 4.6  | MAPPING VIEW                                                           | 46 |

|   | 4.7  | CASE STUDY USING THE PROPOSED DEBUG ENVIRONMENT                        | 46 |

| 5 | МО   | ONITORING                                                              | 48 |

|   | 5.1  | Hybrid Monitoring                                                      | 48 |

|   | 5.1. | .1 Profile Configuration and Monitoring API                            | 49 |

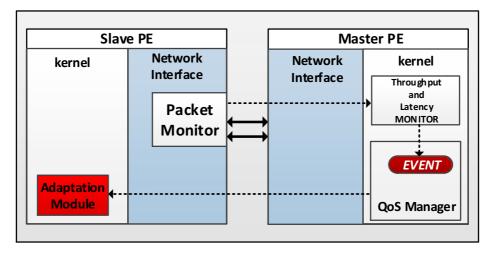

|   | 5.1. | .2 Packet Monitor                                                      | 51 |

|   | 5.1. | .3 Throughput and Latency Monitors                                     | 52 |

|   | 5.2  | SOFTWARE MONITORING                                                    | 52 |

|   | 5.3  | MONITORING EVALUATION                                                  | 53 |

|   | 5.3. | 2.1 Results for scenario with real applications                        | 54 |

|   | 5.3. | 2.2 Results for scenario with synthetic applications                   | 55 |

|   | 5.3. | 2.3 Conclusion                                                         | 56 |

| 6 | AD   | APTIVE QOS TECHINIQUES                                                 | 58 |

|   | 6.1  | Adaptive Flow Priority                                                 | 59 |

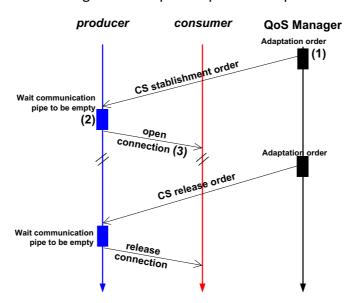

|   | 6.2  | Dynamic Circuit-Switching                                              | 60 |

|   | 6.3  | TASK MIGRATION                                                         | 61 |

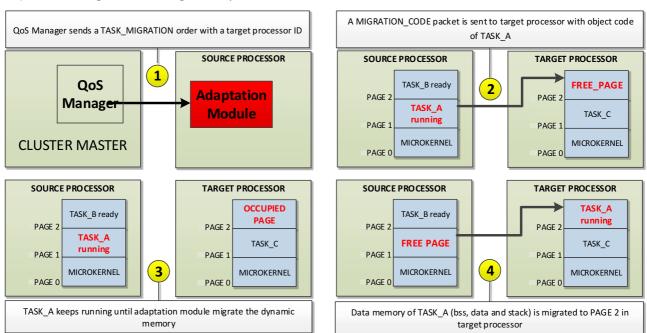

|   | 6.4  | Processor Scheduling                                                   | 63 |

|   | 6.5  | Cluster Defragmentation                                                | 63 |

| 7 RU | JNTIME ADAPTIVE QOS MANAGEMENT | 65        |

|------|--------------------------------|-----------|

| 7.1  | FLOW ADAPTATION                | 66        |

| 7    | 1.1 Results                    | 68        |

| 7.2  | COMPUTING ADAPTATION           |           |

|      | 2.1 Results                    | 77        |

| 7    | 2.1 Results                    | //        |

| ,    | ONCLUSIONS AND FUTURE WORKS    | 84        |

| ,    | DNCLUSIONS AND FUTURE WORKS    | <b>84</b> |

| 8 CC | ONCLUSIONS AND FUTURE WORKS    | <b>84</b> |

#### 1 INTRODUCTION

The reduction of the transistor size allowed the design of increasingly complex systems, with billions of transistors in a single chip [KOR13] [TIL13]. Currently, the state of the art in the semiconductor industry is addressing 22 nm transistors scale [INT13]. Together with this growing complexity, the reuse of IPs (Intellectual Property modules) is a design technique to explore the available number of transistors that can be manufactured in a single die. NoC-based MPSoCs arise in this context, aggregating multiples processing units interconnected by a communication network to compose a system offering scalability and a high degree of parallel processing. NoC-based MPSoCs are a concept that emerged in the beginning of last decade [BEN02], and thenceforth has evolved through several contributions in academic and industrial works.

MPSoCs are adopted in several areas of the electronic industry, with emphasis on embedded systems. Embedded systems are specialized computing systems, with specific requirements to be fulfilled. Examples of embedded systems include: smartphones, tablets, game consoles, avionic devices, automotive devices, medical monitoring systems, biometric systems, among others. Therefore, it is noticeable the potential that embedded systems have, and the relevance of the research in this field, aiming to add more computing power to such systems.

#### 1.1 MPSoC

An MPSoC [WOL08] is composed by several IPs, whose objective is to perform a specific function according to the embedded system application. MPSoCs can be classified into two large groups: heterogeneous and homogeneous.

- In *heterogeneous* MPSoCs, also known as asymmetric MPSoCs, different PE (Processing Element) architectures are used, as GPPs, GPUs, DSPs and ASIPs.

- In *homogeneous* MPSoCs, also known as symmetric MPSoCs, all PEs have the same architecture and are replicated in the system enabling the support of multitask parallel processing. A PE contains a processing unit, a DMA (Direct Memory Access) module, a NI (Network Interface) module, and usually a local memory. In this work, it is also included the router module in the PE definition.

Heterogeneous MPSoC target specific applications, because their IPs are specialized according to the application. In the other hand, homogeneous MPSoCs target general-purpose applications, such as multimedia and telecom applications, and use the replication of identical components (PEs) to increase the processing power. Homogeneous MPSoCs are a trend, due the possibility to achieve better load balancing and fault tolerance due to the redundancy of components. Currently, the industry already works with homogeneous MPSoCs, with e.g. 72 PEs per chip [TIL13]. According to the ITRS 2011, at the end of 2025 MPSoCs will have more than 1000 PEs (http://www.itrs.net/).

Examples of important research topics in the MPSoCs arena include energy consumption, temperature control, QoS, programmability, and fault-tolerance.

#### 1.2 NoC

A NoC [BEN02] is a communication infrastructure to interconnect IPs, decoupling the computation from communication. NoC is composed, basically, by routers and wires. Routers have the function to define the path for each exchanged packet between a given source-target pair, and wires have the function to interconnect routers, and to connect each router with its respective IP.

The main features of a NoC are topology, routing algorithm, flow control, and switching mode [MOR04]. As for the topology, currently stand out the 2D-mesh topology, due its ease of implementation and scalability. As for the routing algorithm, the turn-based algorithms (XY, West-first, etc.) are mostly used, due to low area requirement, minimum path, and deadlock free features. Example of flow control method is the synchronous credit-based, which provides lower latency compared to handshake methods. The most used switching mode is the wormhole packet switching, since it requires the smaller amount of space in buffers and avoids the reservation of network resources for a large amount of time as circuit switching.

An important challenge in the NoC area is to integrate more than one NoC in an MPSoC [TIL13], aiming to allow certain services to use a dedicated communication infrastructure. Another reason to have more than one NoC in the MPSoC is the need of system monitoring support, which can induce excessive traffic on a single network, disturbing applications' communication.

#### 1.3 Distributed Resource Management

In a general purpose MPSoC, with dozen of PEs and several applications starting and finishing over time, it becomes necessary to employ system management. One PE, named master PE, usually performs this management. The master usually does not execute applications' tasks, it is responsible for the system management. Examples of functions that can be assigned to the master PE include: task mapping, task migration, monitoring, execution of adaptive heuristics, among others.

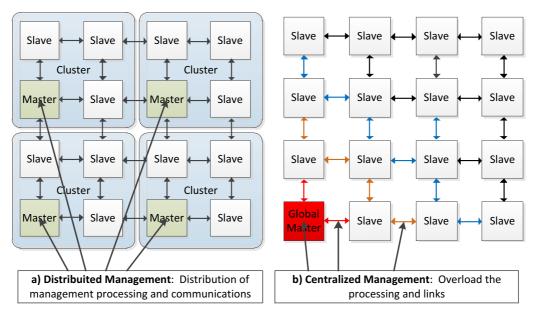

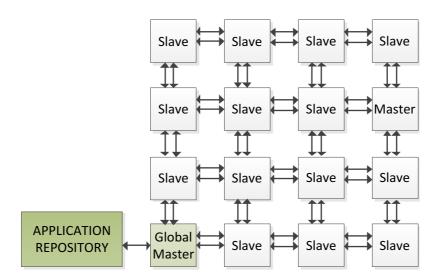

Considering the large number of PEs in current MPSoCs [TIL13], having only one master PE responsible for the entire system management (Figure 1-b) represents a bottleneck, compromising scalability. This single master PE can become unable to handle all system requirements, and induce hotspots in the NoC links close to the master PE.

In distributed management [SHA11][CAS13a] (Figure 1–a), the objective is to divide an MPSoC in clusters, and associate one master PE to each cluster, distributing the management tasks, making the system scalable. In addition, there is a greater isolation between applications, because mapping heuristic will try to map all tasks of a given application in the same cluster. Such isolation between applications favors composability, an important feature for QoS. Clusters can

also change their size at runtime – through reclustering techniques – if the number of application tasks is greater than the number of available cluster resources [CAS13b]. The main drawback of distributed management is the amount of resources reserved for the system management, but this is an acceptable cost due the offered scalability and composability provided by this management scheme.

Figure 1 – Distributed versus centralized MPSoC management.

#### 1.4 Quality of Service

Quality of service (QoS) is a system capability to provide services that meet the user applications requirements. To achieve QoS the system can dedicate some of its resources exclusively to fulfill with the applications requirements. The availability of mechanisms to ensure QoS is an indispensable feature for systems with real-time applications support [CAR11].

There are two main classes of applications that a system with QoS support must consider: (i) Best-Effort (BE) applications, which do not have time requirements; (ii) real time (RT) applications, with temporal requirements, requiring certain levels of QoS to not suffer interference from other applications running on the system.

With the increased complexity of NoC-based MPSoCs in terms of processing elements (PEs), more applications can run simultaneously on such systems, requiring management techniques able to meet the RT applications constraints. In a general purpose MPSoCs, such those described in [HOW10] and [TIL13], applications may start their execution at any moment, characterizing a dynamic workload behavior. In addition, resource sharing among running applications may lead to performance degradation. Thus, a major challenge in the design of such systems is to ensure QoS without performance degradation after a certain period of execution, when several applications were inserted and removed from the system.

Composability is a key feature to achieve QoS in platforms with resource sharing. Composability has as its main objective minimize the inter-application interference and, consequently, allowing the RT applications to reach its constraints. As previously mentioned, the clustering management favors composability through application isolation.

In NoC-based MPSoCs context, two classes of techniques may help to provide composability: communication and computation. The main concern of communication techniques is to control the network resources avoiding traffic interferences. The main concern of computation techniques is to control the processor utilization avoiding interferences due to processor scheduling. To provide a complete QoS support, the platform must support these two classes of techniques.

Flow priority is a communication QoS technique. The basic assumption is to assign different priority levels to the packets injected into the NoC, and reserve network resources according to this priority. Packets with higher priority receive a differentiated treatment, with regard to the resource allocation and differentiated services (differentiated routing algorithms, larger buffer size, arbitration privileges, dedicated physical channels, among others). This approach enables to support soft real-time applications because it contributes to the isolation of the traffic on the network.

Circuit switching (CS) is also a QoS communication technique. CS is largely used to fulfill the constraints of hard real time applications. In CS communication mode, an end-to-end path reservation is established, and the communication takes advantage of the absence of interference from other flows to achieve maximum throughput and minimal jitter.

Besides these techniques, other QoS communication techniques may be employed such as: virtual channels [SAL11][FAN11], time division multiplexing [STE12], and clustering [CUI12][LIA11].

Another way to provide QoS is to act in the computation. In this context, most techniques avoid that RT tasks share the same processor with other RT tasks. Processor scheduling is an example of adopted technique [MOR12]. RT tasks can execute for larger time slices, running for longer periods without interference from other tasks. The scheduler must implement a priority policy enabling to increase the time slice value according to the task priority. The same task scheduler priority can be used together with network flow priority.

Task migration can also provide QoS, if the previous techniques do not achieve the required QoS level. Task migration moves a given task from one PE to another PE [MOR12]. The main goals of task migration in MPSoCs comprise workload distribution, temperature balancing and energy consumption optimization. Task migration may help to achieve the QoS level since the migrated task may be allocated in a free PE (computation technique), and can act in the communication, because the distance between communicating tasks can be reduced (communication technique).

#### 1.5 Monitoring

Monitoring is the key mechanism to enable runtime system adaptability. The monitoring evaluates, at runtime, the system performance, and usually notifies through events an event manager [KOR13]. The event manager can choose the technique that best fits to restore the part of the system with a QoS requirement infringement. The monitoring also can be applied at task level, monitoring RT tasks performance and employing QoS techniques as necessary. Examples of system performance parameters that can be monitored include latency, throughput, jitter, CPU usage, temperature, voltage, among others. The main features to observe in the monitoring implementation are fast response and low intrusiveness, i.e. avoid that monitoring disturbs the application performance.

Monitoring systems can be implemented in software, hardware or be hybrid [KOR13]. Software implementation addresses monitoring at the system level, enabling to control the performance of applications or individual tasks. The main drawback is processing intrusion, because software monitoring generally uses the same processor used by tasks. Hardware implementation addresses monitoring at lower levels, enabling faster responses, and consequently support to real time applications. The hardware monitor can share the same regular data network or employ a specific hardware (dedicated network). Its main drawback is the area cost, and its advantage is low communication intrusion, if monitoring data do not interfere with application data. Finally, hybrid implementations mix software and hardware implementations, and enables the performance parameter monitoring at the system (e.g. tasks execution time, CPU usage) and network (throughput, latency, and jitter) levels. However, such hybrid schemes can penalize the CPU performance and the communication network. To cope with this, the monitoring infrastructure can be hierarchically organized. This feature allows the system to distribute the amount of data produced in multiple event managers, providing scalability.

#### 1.6 Motivation

Everton Carara PhD Thesis [CAR11] addressed the exploration of differentiated communication services to provide QoS in NoC-based MPSoCs. These services are exposed to application's developers through API primitives that enable developers to configure, at application design time, different QoS levels to each application task. The main feature missing in that work is the runtime adaptation of the proposed QoS services.

The motivation to the present work was to integrate several QoS techniques together with a monitoring scheme. As can be observed in Chapter 2 (state of the art), current proposals are focused in providing some degree of adaptation, employing usually only one or two QoS techniques. The present work adopts a monitoring and QoS adaptation that can provide runtime adaptation with four techniques that maximize system resource utilization through heuristics that employ a gradual QoS adjustment according to the requirements of each communicating task pair.

#### 1.7 Goals

This work has strategic and specific goals. The strategic goal is to propose an adaptive heuristic to be employed at runtime, with four different techniques to provide QoS for RT applications at the computation and communication levels for large MPSoCs. Each QoS technique is chosen according to the monitoring data extracted from the system and from application requirements.

The specific goals included:

- Hardware and software integration of two HeMPS platforms (Distributed-HeMPS [CAS13b] and QoS-HeMPS [CAR11]), to compose a new one called QD-HeMPS.

- Development of a software and hybrid distributed monitoring scheme;

- Evaluation of the intrusiveness of both monitoring schemes, choosing the one presenting smaller intrusiveness and higher scalability;

- Development of three adaptive QoS techniques: (i) flow priority; (ii) circuit switching;

(iii) task migration;

- Integration of the processor scheduling priority mechanism proposed in [MAD13], to provide QoS (the fourth QoS technique);

- Development of an adaptive heuristic to employ at runtime all four QoS techniques;

- Evaluation of the QoS heuristic.

#### 1.8 Contributions

The contributions of this work include:

- A distributed and QoS NoC-based MPSoC platform;

- A software and hybrid monitoring schemes, with the evaluation and comparison of both schemes;

- Three adaptive QoS techniques: (i) flow priority; (ii) circuit switching; (iii) task migration;

- A heuristic to employ the appropriate QoS technique at runtime.

Another important contribution was the development of a protocol-based debugging tool to aid in the implementation of the specific goals. This debugging tool became a powerful tool to implement and validate new protocols and to debug NoC-based MPSoCs.

#### 1.9 Document Organization

This document is organized as follows. Chapter 2 presents the state of the art in two areas of NoC-based MPSoCs: monitoring and QoS. Chapter 3 presents the MPSoC platforms used as

reference for the development of this work. Chapter 4 presents the debugging tool. Chapter 5 presents the monitoring infrastructure. Chapter 6 presents the adaptive QoS techniques. Chapter 7 presents the runtime adaptive QoS management of the techniques presented in Chapter 6. Finally, Chapter 8 presents conclusions and directions for future works.

#### 2 STATE OF THE ART

This Chapter reviews related works in monitoring and QoS of NoC-based MPSoC systems. At the end of each session, a comparative table is presented positioning the present work with the state of the art.

#### 2.1 Monitoring

Stan et al. [STA11] proposes monitoring at runtime to detect timelines violations on MPSoCs. The monitoring scheme is implemented in hardware, enabling run-time verification according to the loss of deadlines in the communication between tasks. This evaluation occurs at each PE in the PLB (Peripheral Local Bus), observing the transactions made at a circular buffer, mapped in the processor memory space. This circular buffer is used in the communication between the tasks. The monitor evaluates communication's time intervals defined in experiments (profiling step) with the communication's time intervals measured in the PLB, and generates events when a violation is detected. No monitoring results are presented.

Matos et al. [MAT10] proposed a monitoring scheme observing the NoC communication buffers. The monitor consists of one hardware block implemented inside the local buffer controller. The monitor counts the number of packets transmitted through the channel. If the number of monitored packets violates a threshold (configured at design time), the monitor sends the amount of monitored packets to a central controller. The central controller checks whether the amount of received packets achieved a threshold (set at design time), and then invokes a policy for buffer resizing. The obtained area overhead was 37,5% over the reference router. No intrusion results are explored.

Faruque et al. [FAR12] proposed a monitor to support QoS through buffer resizing. The implemented monitoring evaluates the occurrence of events. Events are situations when successful traffic propagation is prevented in the communication architecture. The monitoring component is event-based. Events are created when a performance reduction in a subsystem of an individual router is detected (*TTL-expire-event*, *No-route-found-event*, *No-buffer-event*, *Buffer-full-event*). Figure 2 presents the monitor overview. The monitor is implemented between the router and the NI, being a counter that evaluates the number of events up to a threshold. If the number of events is greater than the threshold, the monitor notifies the NI. When the NI receives a notification from the monitor (in the form of a monitoring packet), it performs adaptations to avoid new violations. As monitoring is based on events, there is no monitoring traffic when the network operates normally. The monitoring intrusion obtained by experiments was 0.7% of the total link capacity. The area overhead was 297 slices on an FPGA to each PE.

Figure 2 – Overview of the monitoring approach [FAR12].

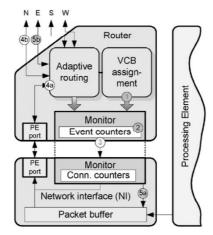

Saind et al. [SAI10] proposed a technique to monitor tasks with temporal constraints. Only periodic tasks are considered. The descriptor of the task TCB (Task Control Block) was modified aiming to support variables that enable to control time thresholds for periodic tasks. The monitoring is based on watchdog timers, divided into two hierarchical levels: local and global watchdogs. Figure 3 presents the monitoring approach using the watchdogs. Local watchdogs control the execution at the task level, and the global watchdog control the execution at the system level. The global watchdog has a common hyper period for all tasks. A communication between a task and its watchdog is created when the task starts, initializing the watchdog with temporal parameters obtained in a profiling step. Local watchdogs communicate with the global watchdog to report the loss of deadlines through an event. The global watchdog stores these events. When the hyper period expires, the global watchdog analyzes the list of events and verifies if these affected the overall execution of the system. If there are any violations, the global watchdog searches where the source of violations is located, and triggers a measure to solve the problem. No monitoring results are presented.

Figure 3 – Monitoring using watchdogs [SAI10].

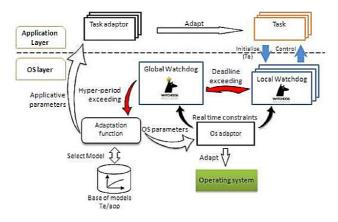

Fiorin et al. [FIO10] proposes a monitoring architecture for NoCs. The architecture is based on probes that monitor the occurrence of events. The monitoring system is composed of three main components (Figure 4):

- (i) probes, located inside NIs and monitor the cores' operations and events (reading the OCP/IP signals), as well as resources utilization and the communication events generation in routers and NIs;

- (ii) a *subsystem* for data collection and storage;

- (iii) a *central element* (Probes Management Unit PMU), which is in charge of the configuration of the probes and the collected data handling.

The probes are generic and can be configured with different communication thresholds. In [FIO10] time windows are defined, and at the end of a window the events collected by each probe are sent to the PMU. The PMU has two basic tasks: program the probes' registers with thresholds, and process the collected data from probes. Both tasks are software implemented by the subsystem that runs in each PMU. The Authors report that the monitoring traffic presented an intrusion to 0.2% of the bandwidth of the NoC (equivalent to 2 GBps) and 5% of traffic generated by the PEs. The area overhead was 55% compared to the reference NoC and 3% over the entire PE.

Figure 4 – Overview of NoC monitoring infrastructure proposed in [FIO10].

Wang et al. [WAN10] proposes a monitoring scheme based on sensors to monitor temperature and voltage. The sensors are distributed and are inserted at each PE (between the core and the NI). Each sensor sends its data using a dedicated NoC communication infrastructure. The data is sent to a central manager – CM, which can take actions to avoid violations of predefined thresholds. The sensors collect information at runtime for each PE. The monitoring information contains the address of the sensor that sent it, which allows the CM to identify the source of the information and apply the adaption procedure. The maximum intrusion was 0.8% compared to NoC without sensors. The Authors do not present area overhead results.

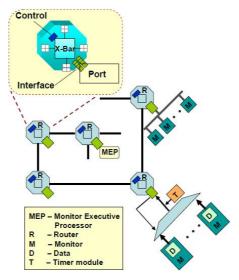

Zhao et al. [ZHA11] proposes a centralized monitoring infrastructure for temperature, voltage and error data monitoring. A dedicated monitoring NoC called MNoC (Monitor Network-on-Chip) interconnects the monitors. Figure 5 presents the MNoC overview. The MNoC also has an interface to an exclusive monitoring processor called MEP (Monitor Executive Processor). This processor has a software layer that implements the monitoring algorithms. The monitors are divided into two categories: regular monitors (used for periodic monitoring data, such as temperature), and irregular monitors (with reports abnormal events, as faults). The communication in this scheme occurs only between monitors and MEP and not between monitors.

The monitored data is classified in two classes. The regular monitors have low priority, and irregular monitors higher priority. Once the MEP receives monitoring data from the monitors, it uses this information to determine the type and location of the event and take the necessary actions by changing system parameters.

Figure 5 – MNoC Overview of [ZHA11].

An area overhead of 0.2% was obtained for the monitor interconnection when applied to an eight-core system based on the AMD Athlon processors. In network comparisons, the entire MNoC router is about 7% of the size of a reference NoC router.

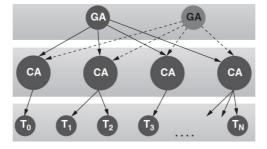

Faruque et al. [FAR10] proposes software monitoring for Dynamic Thermal Management (DTM). The goal is to keep the temperature of each core below a threshold, avoiding hotspots. The monitoring is performed through agents implemented in a distributed manner. The scheme employs a hierarchical management with three agent classes, Figure 6. The Tile Agents (TAs) are attached to each tile, containing sensors that measure the tile temperature and communication volume. When a temperature threshold is reached, it is generated a notification from a TA to a CA (Cluster Agents), and this may initiate the DTM. CAs keep the temperature information of each cluster tile, and execute task remapping according to the tiles' temperature. They also communicate with other CAs, and store application details such as the application task graph. Global Agents (GAs) perform assignment of unmapped tiles to clusters, create and destroy CAs, and are called by CAs to remap applications to enable DTM across clusters.

Figure 6 – Agents Hierarchies [FAR10].

The overhead is measured in terms of memory usage. Agents require 147.5 Kbytes, 494.1 Kbytes, and 19 bytes of on-chip memory for a GA, the CAs, and a TA, respectively, for a 64x64 architecture with 32 clusters. The required on-chip memory required was 0.65 Mbytes, which can be considered, according to the Authors, negligible in future technology nodes. No monitoring intrusion results were presented.

Guang et al. [GUA10] proposes a hierarchical monitor system for power management. The work evaluates latency and throughput parameters. If these parameters exceed a threshold, DVFS (Dynamic and Voltage Frequency Scale) is applied. The monitors are divided into four types of agents: cell agents (hardware implemented, corresponding to the lower hierarchical level); cluster agents (software and hardware implemented, second level of hierarchy); platform agents (software implemented, third level of hierarchy); and application agents (software implementation, with the higher hierarchy level). Each agent has a specific role. Application agents sends latency application's requirement to platform agents. Platform agents determine the number of processors for each application and map these processors on nodes of the network based on a tree algorithm. Platform agents also determine the maximum load of buffers for each cluster agent according to each application's requirements. Cluster agents apply DVFS for each application according to monitored cluster traffic reported by cell agents. The proposal overhead of the hardware agents was 0.003 mm² and 0.008 mm² to cluster and cell agents respectively. No overheads related to software agents are presented.

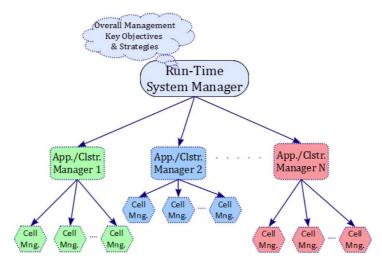

Fattah et al. [FAT11] proposes a model for a hierarchical management that mixes a distributed and centralized monitoring system. In the proposed scheme, there are various levels of managers/monitors. The first level corresponds to monitors allocated in PEs (cell monitors) that send information to the application manager, which sends its information to a global manager (Figure 7). According to system demands, each cell may contain different monitoring capabilities (e.g. temperature sensors, power monitors, fault detectors, etc.), along with several actuators such as voltage and frequency regulators, reconfiguration possibilities, and so on. Each cell has its own manager that generates events for its higher-level manager based in the monitored information. A mid-level manager groups and manages a set the cells. In the proposal, the size of the cluster is application oriented (a cluster consists of a group of PEs that runs tasks of an application), but different clustering policies may be employed. The mid-level manager, called application manager, manages each cluster. Each application manager is responsible for the distribution and management of tasks in order to supply the requirements of the application. A top-level manager, or System Manager, is responsible for managing the system, and coordinates the actions of lower-level managers (application managers). The System Manager runs at the operating system level, creating and removing application managers according to the characteristics of the system.

Figure 7 - MPSoC Management Hierarchy [FAT11].

Kornaros et al. [KOR12] proposes a real time hierarchical monitoring infrastructure. The implemented monitoring is based on local monitoring units of low granularity. These units are hardware implemented at the NI. The data collected at real time on each local unit is transferred to the monitoring manager. This manager, implemented in hardware, can analyze statistically the data and employ adaptive resource management techniques. The monitors implemented in the NI can also take local decisions, communicating with a buffer manager to execute a dynamic buffer resizing. Each monitor of the NI evaluates the packets' header, and through a filter mechanism, which can be programmed by software, can reduce the volume of data collected before sending to the monitoring manager. Local monitors also are able to differentiate packets from different clusters and applications. The monitoring scheme is hierarchically organized. In the first level (system level), the monitoring manager, execute software management routines. The manager is responsible for monitoring data from the probes of each NI. Furthermore, as a top hierarchical level, the work proposes a high performance global manager implemented in hardware. Each cluster monitoring manager or local monitors, can communicate with this central manager, and signalize the occurrence of events. The proposed monitoring scheme is generic and allows the designer to customize it at design time. It is also possible to determine how local monitors will communicate with the monitoring manager, being possible to use a dedicated link or the NoC links. The Authors mention that the monitoring process delay (capturing, selection and transmission of the identified event), takes in average 50 clock cycles. The obtained area overhead was 11,7% compared to a Hermes 2x2 NoC [MOR04].

Table 1 compares the reviewed works. The second column of the Table addresses the monitoring organization. Works [STA11][MAT10][FAR12][SAI10] adopt distributed monitoring. In this context, a monitor module is inserted at each node of the MPSoC or NoC, executing local adaptations. This scheme may be used with simple adaptation protocols, or with simple intermonitor communication. However, it is not scalable because the protocols must be implemented at each node, increasing the overhead (redundancy) of the platform. In addition, a fully distributed

approach does not contain a global or partial view of the system, leading to local decisions, which may compromise the performance of the whole system.

Works [FIO10][WAN10][ZHA11] employ a centralized monitoring scheme. The centralized organization avoids the drawback of the distributed monitoring, using a single global unit to control the system. This approach often adopts a hybrid implementation (hardware and software monitors), due to more abstract information handling by the control unit. As in the fully distributed approach, the centralized monitoring is also not scalable because concentrate all the monitored information in a single unit.

Works [KOR12][FAR10][FAT11][GUA10] use a hierarchical monitoring organization. These proposals divide the monitoring management in usually in two hierarchical levels. Each level executes specific monitoring actions, based on their granularity. This scheme is scalable, because it distributes the monitoring traffic and monitoring management in regions, named clusters. Inside each clusters the monitoring is centralized, but at the platform level, the monitoring is distributed. Such scheme also uses a hybrid implementation enabling generic monitoring, because the user can implement different adaptation techniques in the two management levels (cluster and global), and can configure the monitoring characteristics at design time.

Works [ZHA11][GUA10] use a dedicated network for monitoring. This approach eliminates the intrusion of the monitoring traffic in the regular traffic, but requires more area, energy, and increases the design complexity.

The present work adopts a hierarchical organization, with a hybrid implementation and a cluster management only, not adopting a global manager due the management bottleneck possibility in this manager level. The proposed monitoring can be used for general purposes because it is not linked with the runtime adaptation modules.

| Proposal        | Organization | Implementation | Monitoring Management      | Application                      |

|-----------------|--------------|----------------|----------------------------|----------------------------------|

| Stan (2011)     | Distributed  | Hardware       | Each PE                    | QoS                              |

| Matos (2010)    | Distributed  | Hardware       | Router                     | Buffer resizing                  |

| Faruque (2012)  | Distributed  | Hardware       | Router/NI                  | QoS and Buffer resizing          |

| Said (2010)     | Distributed  | Software       | Microkernel                | Real time task deadline          |

| Fiorin (2010)   | Centralized  | Hybrid         | NoC Central Unit           | Generic (resources availability) |

| Wang (2010)     | Centralized  | Hybrid         | NoC Central Unit           | Thermal and Voltage              |

| Zhao (2011)     | Centralized  | Hybrid         | NoC Central Unit           | Temperature, voltage, error data |

| Faruque (2010)  | Hierarchical | Hybrid         | Cluster and Global Manager | Dynamic Thermal Management       |

| Guang (2010)    | Hierarchical | Hybrid         | Cluster and Global Manager | DVFS                             |

| Fattah (2011)   | Hierarchical | Hybrid         | Cluster and Global Manager | General purpose                  |

| Kornaros (2012) | Hierarchical | Hybrid         | Cluster and Global Manager | General purpose                  |

| This proposal   | Hierarchical | Hybrid         | At each Cluster Manager    | General purpose                  |

Table 1 - State-of-the-art comparing works targeting monitoring support in NoCs.

#### 2.2 Quality of Service

Wang and Bagherzadeh [WAN12] propose a router able to meet QoS constraints through arbitration with dynamic congestion control and adaptive routing. The Authors adopt a NoC with 64-bit bi-directional links, where each router has 2 horizontal links, 4 vertical links, and 4 diagonal links. VCs are not used in the adopted NoC. For the dynamic control of QoS it is used an algorithm that evaluates the congestion at input and output ports. Packets coming from hotspots have high priority to be arbitrated, reducing congestion. However, this congestion control is restricted to the router, where local decisions are made, which may not necessarily eliminate congestion, but just transfer it to another point.

Wissem et al. [WIS11] presented the design of a *Switch Allocator* for a router to enable QoS support. The Switch Allocator contains five dynamic arbiters, and receives routing requests from each input port, assigning packets to the output port in accordance with the packet priority. The packet that has the highest priority grants access to the output port. When there is more than one packet with the same priority, the order is defined by a round-robin algorithm. According to the Authors, the proposed router supplies a bounded latency to real time packets.

Kakoee et al. [KAK11] propose a fault tolerant router and QoS support with flow priority and duplicated physical channels. The channels are divided in high and low priority. Each packet has a bit setting its priority. In the proposal, one channel is dedicated to high-priority traffic, and the second one for low-priority traffic, being possible to share it with high-priority packets.

Salah and Tourki [SAL11] propose a router architecture for real-time applications, using packet switching, QoS support and a priority-based flit scheduler for BE and GS flows. The scheduler evaluates the deadlines of the incoming flows, selecting VCs according to the flow class, BE or GS. According to the Authors, results show that their router achieves an optimal packets scheduling, increasing channel utilization and throughput, a reduction of network latency, and avoidance of resources conflicts.

Fan et al. [FAN11] propose a router combining VCs with duplicated physical channels. Each physical channel creates a *subnet*, with a dynamic number of VCs. The allocation of VCs is executed at runtime, by an arbiter, reserving VCs and dynamically allocating them according to the demand of each port. Each subnet uses a different routing algorithm: XY and YX. The NI chooses which subnet a given flow will use. Once on a subnet, a packet cannot change the subnet. The VCs for XY only accept packets routed according to the XY algorithm, and vice versa.

Lusala and Legat [LUS11] propose a NoC with simultaneous PS (packet switching) and CS (circuit switching). Two subnets are created: one for CS using SDM (Spatial Division Multiplexing), and the other one for PS. A "sub-router" controls each subnet. GT (guaranteed throughput) flows use the CS subnet, while BE flows use the PS subnet. The PS sub-router, besides transmitting BE traffic, is responsible for the configuration of the CS sub-router, receiving connection requests and reserving a channel of the CS sub-router.

Winter and Fettweis [WIN11] presented and evaluated different implementations of a central hardware unit, name *NoCManager*, which allocates at run-time guaranteed service VCs providing QoS in packet-switched NoCs. The Authors argue that the central *NoCManager* is superior to the distributed technique. Besides this conclusion, the Authors mention scalability issues, and point out a hierarchical method as future work.

Saponara et al. [SAP12] presents the design of a network interface with hardware support for error management, power management, ordering handling, security, QoS management, programmability, end-to-end protocol interoperability, remapping. The Authors adopts virtual channels and a bandwidth allocation scheme to ensure QoS for real-time applications. An API is used to manage the NI resources/services. The Authors evaluate the NI area, without performance results related to QoS. The main drawback of the hardware approaches to ensure QoS is the lack of flexibility. Software policies, as the ones presented in this work, may be easily modified according to the applications running in the MPSoC.

Joven and Marongiu [JOV10] integrate hardware and software to provide QoS control at the application level in an *xpipe*-based NoC. The QoS architecture, implemented at the hardware level consists of control blocks that are implemented on the router to handle different QoS services: GS (guaranteed service) and BE (best-effort). The Authors use communication priorities (up to 8 priority levels) and GS through allocation of connection channels. The implementation at the software level uses an *openMP* framework, adopting an API that interacts directly with the NI. The NI inserts the priority in the header of the packets and is responsible for the initiation and termination of connections. The kernel provides abstract functions to send and receive messages, and to establish and close connections. The Authors employ a layered design to expose the hardware QoS features to the architecture, similar to our proposal, but the services are statically controlled by the application, without a monitoring scheme to adapt the system on the fly when the applications requirements are violated.

Motakis et al. [MOT11] explores the management of the NoC services to adapt the hardware resources through techniques implemented in software, allowing the user to explore the different network services through an abstract API. The implementation is based on the *Spidergon* STNoC platform. Lower-level layers are explored, along with a library of functions named *libstnoc* accessible to the user. The work focuses on dynamic reconfiguration of the communication services through the *libstnoc*. The designer can access information services (energy management, routing, QoS and security), and also enable and change these parameters through memory-mapped registers. The API can also perform a diagnostic service of the NoC traffic, changing QoS parameters at run time based in constraints defined by the user. As Joven and Marongiu [JOV10], the hardware is exposed to the application level. The Authors conclude their work mentioning the need to include NoC traffic monitoring services to ensure QoS.

Cui et al. [CUI12] propose a decentralized heuristic for task mapping. The proposal adopts a cluster-based method, implemented using the Tera Scale platform NoC. The clusters do not have a

fixed size. Clusters can be resized at runtime, according to the characteristics of each application, and they can contain more than one application. The local managers control the cluster resizing in a decentralized fashion. The clustered approach achieves QoS by isolating applications, ensuring composability.

Liao and Srikanthan [LIA11] explore QoS through a hierarchical structure, dividing the MPSoC in clusters. Each cluster contains one application and a cluster manager. The system also has a global manager responsible for high-level tasks. The goal of the clustering heuristic, implemented in software, is to ensure at runtime the isolation of the traffic between different applications, favoring composability, an important feature for QoS.

Table 2 compares the reviewed works. In most works, [SAL11][FAN11][WAN12][WIS11] [KAK11][LUS11], the QoS management (2<sup>nd</sup> column of the Table) is made at the router level. Such approach takes local decisions, which may be inefficient at the system level. A centralized approach, as the one proposed in [WIN11], has a global view of the system, but scalability is sacrificed. In [MOT11], a scheme of QoS adaptation is implemented at the PE level, as in the present work, where the user informs the constraints. However, that proposal does not solve the scalability issue, and the work is tightly dependent to the *Spidergon STNoC*. A trade-off is achieved with a hierarchical approach, with several managers distributed in the system [CUI12][LIA11]. Our work may be applied to centralized or hierarchical systems, and is able to provide QoS adaptability.

Physical channel QoS Management QoS Technique Adaptive technique Proposal 2 horiz., 4 vertic., and 4 Dynamic Arbitration and Congestion Aware Wang (2012) Router level diagonal Adaptive Routing Routing Algorithm Wissem (2011) Router level Flow Priority One per direction No Kakoee et al. (2011) Router level **Duplicated channels** Flow Priority No Flow Priority Salah (2011) Router level One per direction Flit Scheduling Virtual Channels Fan (2011) Router level **Duplicated channels** Virtual Channels Virtual channel allocation Lusala (2011) Router level PS+CS (SDM) **Duplicate channels** Winter (2011) Router level / Centralized One per direction Virtual Channels / CS Central NoC Manager (HW) Virtual Channels / Saponara (2012) Network interface level One per direction Management API admission control Joven (2010) Router and PE levels One per direction Flow Priority / CS Management API Motakis (2011) PE level One per direction Bandwidth allocation Management API

One per direction

One per direction

**Duplicated channels**

Composability

Composability

Flow Priority / CS / Task

Migration / Scheduling

**Priority**

Reclustering

Cluster Allocation

Monitoring and runtime

QoS adaptation according

to constraints

Hierarchical

Hierarchical

Hierarchical

Cui (2012)

Liao (2011)

This Proposal

Table 2 - State-of-the-art comparing works targeting QoS support in NoCs.

A common choice in NoC designs is to interconnect routers using single bi-directional links (3<sup>rd</sup> column). An alternative to such approach, leading to good results, in terms of communication performance and QoS, is to increase the number of physical channels [FAN11][WAN12][KAK11]

[LUS11]. Such approach replaces VCs, with a smaller silicon cost, and may result in disjoint networks, enabling the use of priorities or simultaneous switching modes [KAK11].

As can be observed in the fourth column of the Table, approaches with QoS management at the router level adopt three main techniques to meet QoS: flow priorities [FAN11][WIS11] [KAK11] [JOV10], virtual channels (VCs) [SAL11][FAN11][WIN11] and circuit switching (CS) [WIN11][JOV10]. The hierarchical management [CUI12][LIA11] meets QoS favoring composability, i.e., applications are "isolated" in clusters, without the interference of other flows. The drawback of hierarchical approaches is to find continuous regions to map applications, even if available resources exist, and avoid the application fragmentation in dynamic workload scenarios.

As can be observed in NoC research arena, designers focus their efforts to develop mechanisms to provide QoS at the network level. However, MPSoCs start to employ NoCs as the de-facto communication infrastructure, adding a software layer over the network. Hence, the designers start to work on APIs to expose at the software level the QoS mechanisms. Currently the main gap observed in the literature is the adaptive techniques managed at runtime to meet QoS (5<sup>th</sup> column of Table 1). Works [SAL11][FAN11][WIS11][KAK11][LUS11] ensure QoS at the NoC level using synthetic traffic. Works [MOT11][JOV10][SAP12] expose the NoC level to the application, leading to the application developer the responsibility to select the most appropriate adaptive technique. The goal of works [CUI12] and [LIA11] is to isolate applications in clusters, to minimize the interference of other flows, ensuring QoS.

The originality of the present work is to select at runtime a given adaptive technique by using monitoring to detect violations, and a QoS Manager to control the flows. The work herein proposed adopts flow priority, CS, task migration and scheduling priority, controlled by a QoS Manager.

#### 3 REFERENCE PLATFORM

The reference platform, developed in this work, integrates two existing ones: Distributed-HeMPS and QoS-HeMPS. This Chapter describes such platforms, and the integration between them, corresponding to the first contribution of the present work.

#### 3.1 Distributed-HeMPS

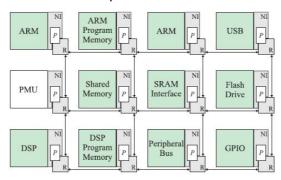

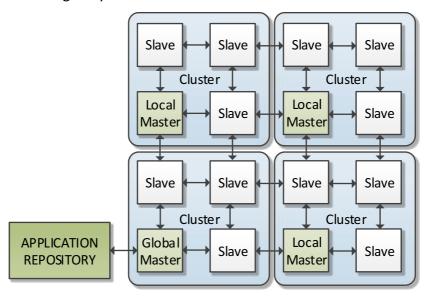

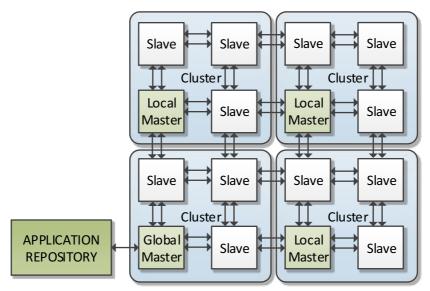

The Distributed-HeMPS platform [CAS13] implements in the PE microkernel (small operating system) the clustering concept to distribute management actions. The platform assigns to the PEs three different roles: slave, local master and global master.

Observing Figure 8, each cluster contains a set of slave PEs (for user applications processing), managed by a local master (manager PE). The local master is responsible to implement heuristics as task mapping, task migration, and reclustering. Reclustering is a technique that allows the local master to borrow resources from neighbor clusters if the cluster does not have enough resources to execute a given application assigned to it. A resource is a processor page at each slave processor memory, which can allocate one task (note that is assumed a paged memory organization in this work). The cluster size is variable, because reclustering can increase the number of slave PEs managed by the local master.

Figure 8 – Overview of Distributed-HeMPS platform. The cluster-based management is the main feature.

The platform has also one global master (global manager PE), which communicates with the local masters, characterizing a three level hierarchical management structure (global master  $\rightarrow$  local masters  $\rightarrow$  slaves). The global master implements the same functions as the local masters, and in addition accesses an external application repository to map applications to the clusters. The application repository is a memory that stores applications that can enter in system (workload). As soon as the global master receives an application request of a local master, it accesses the

repository and transfers the object code of application (task object code) directly to the slave PE that will run the task.

The Distributed-HeMPS uses the Hermes NoC [MOR04], configured with 16-bit physical channels; XY routing algorithm; input buffering; credit-based flow control; round robin arbitration; and wormhole packet switching. The PE connected to each NoC router contains: a 32-bit Plasma processor (MIPS-like architecture); a local memory; a DMA (Direct Memory Access) module; and a NI (network interface).

#### 3.2 QoS-HeMPS

Figure 9 presents overview of QoS-HeMPS [CAR11] platform. The QoS-HeMPS is a platform with centralized management, supporting QoS through differentiated communication services. The platform assigns to PEs two different roles: slaves and one global master. Slave PEs execute user applications, and their microkernel implements the software layer for QoS services. An API exposes to the application developer the control of differentiated communication services, implemented in NoC and NI. The single global master accesses the external repository, and implements protocols for task allocation and task termination in the slaves PEs.

Figure 9 - Overview of QoS-HeMPS platform. The QoS support is the main feature of the platform.

The QoS-HeMPS NoC implements differentiated communication services to enable QoS support. The relevant features of this NoC are: (i) duplicated 16-bit physical channels, assigning high priority to channel 0 and low priority to channel 1 (high priority packets may use both channels); (ii) deterministic Hamiltonian routing [LIN94] in channel 1 and partially adaptive Hamiltonian routing in channel 0; (iii) simultaneous packet and circuit switching; (iv) unicast and multicast transmission; (v) input buffering; (vi) credit-based flow control; (vii) round robin arbitration.

Except for the NI, the hardware of the PE is practically the same as the Distributed-HeMPS. The difference comes from one mapped-memory register to signalize to the microkernel an

incoming packet requisition made by CS. The NI implements a QoS treatment, in order to inject the packet into the appropriate physical channel.

### 3.3 Developed Platform: QD-HeMPS

A new platform was developed in the scope of this work, integrating the two previous platforms, named QD-HeMPS.

To accomplish such integration the main executed tasks were:

- Translation from VHDL to RTL-SystemC of the QoS-HeMPS NoC, and the corresponding validation through simulation;

- Translation from VHDL to RTL-SystemC of the QoS-HeMPS NI, and the corresponding validation through simulation;

- QoS software layer adaptation and validation in the slave, local and global Distributed-HeMPS microkernels;

- API adaptation to expose the QoS services to user.

The first two tasks were necessary because the Distributed-HeMPS was modeled in RTL-SystemC and the QoS-HeMPS was modeled in VHDL. SystemC was also chosen since it enables fast simulation, keeping the accuracy of the RTL VHDL model.

During this process, some errors in the Distributed-HeMPS were identified, being reported to the research group, and corrected. The backward compatibility was kept, and an application that runs in the Distributed-HeMPS executes in the new platform, without modifications. Figure 10 depicts the QD-HeMPS. The new QD-HeMPS includes the distributed management features of the Distributed-HeMPS and the duplicated physical channels, the main feature of QoS-HeMPS.

Figure 10 – QD-HeMPS Overview. QoS-HeMPS and Distributed HeMPS Integration.

#### 3.3.1 Tasks Communication

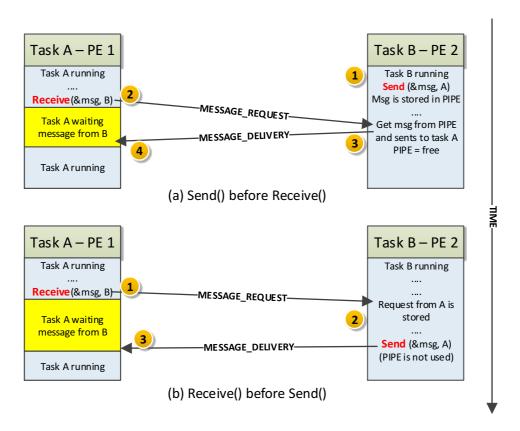

The task communication model is the same in both platforms (Distributed and QoS HeMPS), and was kept in the QD-HeMPS. In this model (MPI-based), tasks communicate using *Send()* and *Receive()* primitives. The Send() primitive is called by the producer task, and the Receive() primitive is called by the consumer task.

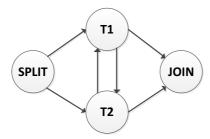

The protocol is the *read-request*, i.e., a message is injected in the network only when the producer task has received a message requisition. This requisition corresponds to a control packet named MESSAGE\_REQUEST. A MESSAGE\_REQUEST packet is generated by a consumer task when it calls the *Receive()* primitive. The OS of the consumer task blocks the task, putting it in WAITING state, up to the reception of a MESSAGE\_DELIVERY packet. The MESSAGE\_DELIVERY is a data packet that is generated by the producer task in two situations: (i) *Send()* called before a Receive(); (ii) *Receive()* called before a *Send()*. Figure 11 describes the task communication model, explaining the possible two scenarios.

Figure 11 –Communication Model (MPI-like) adopted in the platforms.

Figure 11(a) presents a *Send()* called before a Receive(). It is supposed that task A is running in PE 1, and task B in PE 2. In step 1, task B executes a *Send()*, producing a message to task A. At this point, the microkernel searches for the respective MESSAGE\_REQUEST, but no requisition is found because task A did not called the *Receive()* primitive yet. Hence, the message produced by task B is stored in a buffer named *pipe*, and task B keeps running normally, *characterizing a non-blocking send*. In step 2, task A executes a *Receive()*, generating a MESSAGE\_REQUEST packet to

task B. Task A is blocked, going to a WAITING state, characterizing a blocking receive. When PE 2 receives the requisition packet in step 3, the microkernel finds the message stored in the pipe, and sends it to task A through a MESSAGE\_DELIVERY . Finally, in step 4, the microkernel of PE 1 handles the received MESSAGE\_DELIVERY packet, transferring the packet to the memory space of task A, and re-schedules task A for execution (READY state).

Figure 11(b) presents a *Receive()* called before a *Send()*. In step 1, task A executes a *Receive()*, generating a MESSAGE\_REQUEST packet that is sent to task B, and the task A switches to the WAITING state. In step 2, the packet is handled by the microkernel of PE 2, which searches for the respective MESSAGE\_DELIVERY, but no message is found because task B did not called the *Send()* primitive yet. Thus, the microkernel stores this MESSAGE\_REQUEST. In step 3, when task B calls the *Send()* primitive, the microkernel finds the stored MESSAGE\_REQUEST, and the message produced by task B is directly forwarded to task A, without storing it in the pipe. When task A receives the MESSAGE\_DELIVERY, the microkernel releases task A and restores its execution.

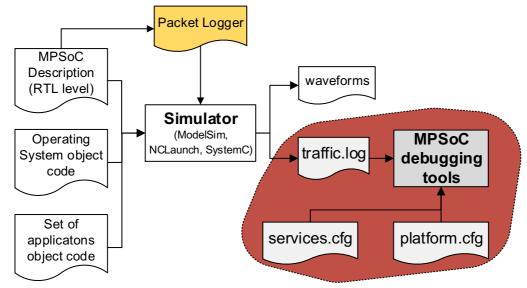

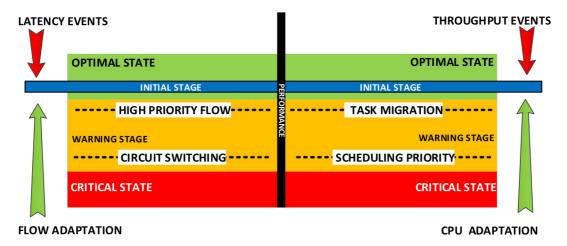

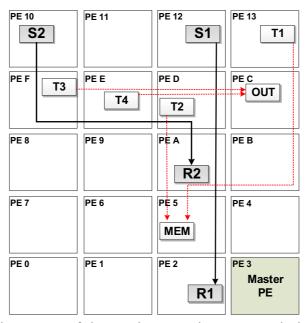

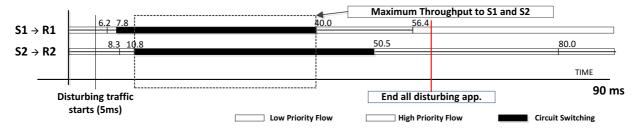

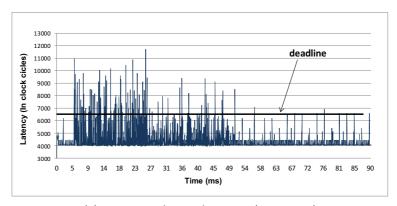

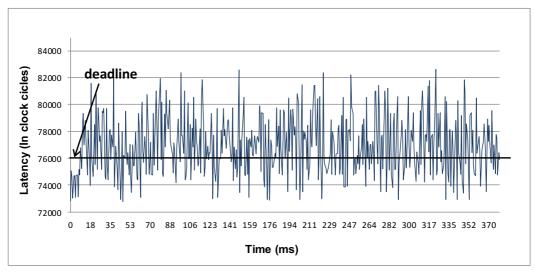

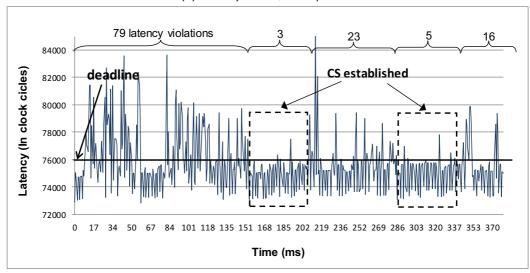

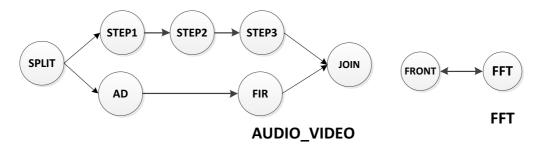

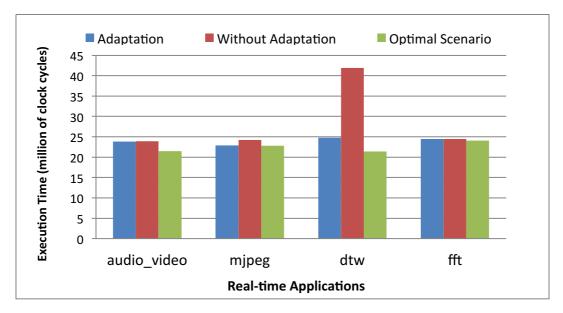

### 4 DEBUGGING TOOL FOR MPSoCs