## PONTIFICAL CATHOLIC UNIVERSITY OF RIO GRANDE DO SUL FACULTY OF INFORMATICS COMPUTER SCIENCE GRADUATE PROGRAM

# ANALYSIS OF VOLTAGE SCALING EFFECTS IN THE DESIGN OF RESILIENT CIRCUITS

## **MATHEUS GIBILUKA**

Dissertation submitted to the Pontifical Catholic University of Rio Grande do Sul in partial fullfillment of the requirements for the degree of Master in Computer Science.

Advisor: Prof. Dr. Ney Laert Vilar Calazans

## Dados Internacionais de Catalogação na Publicação (CIP)

G446a Gibiluka, Matheus

Analysis of voltage scaling effects in the design of resilient circuits / Matheus Gibiluka. – 2016.

103 f.

Dissertação (Mestrado) – Faculdade de Informática, PUCRS. Orientador: Prof. Dr. Ney Laert Vilar Calazans

1. Informática. 2. Processamento de Imagens. 3. Circuitos Assíncronos. 4. Diagnóstico por Imagem. 5. Arquitetura de Redes. I. Calazans, Ney Laert Vilar. II. Título.

CDD 004.6

Ficha Catalográfica elaborada por Loiva Duarte Novak - CRB10/2079

Prof. Dr. Luiz Gustavo Leão Fernandes

Coordenador.

## Pontifícia Universidade Católica do Rio Grande do Sul FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

# TERMO DE APRESENTAÇÃO DE DISSERTAÇÃO DE MESTRADO

| Dissertação intitulada " <i>Analysis of Voltage Scaling Effects in the De</i><br>Circuits" apresentada por Matheus Gibiluka como parte dos requisito<br>do grau de Mestre em Ciência da Computação, aprovada em 4 de<br>pela Comissão Examinadora: | os para obtenção |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|                                                                                                                                                                                                                                                    |                  |

| Prof. Dr. Ney Laert Vilar Calazans–<br>Orientador                                                                                                                                                                                                  | PPGCC/PUCRS      |

| Fund Jam los                                                                                                                                                                                                                                       |                  |

| Prof. Dr. Fernando Gehm Moraes –                                                                                                                                                                                                                   | PPGCC/PUCRS      |

|                                                                                                                                                                                                                                                    |                  |

| Dr. Matheus Trevisan Moreira -                                                                                                                                                                                                                     | Chronos Tech     |

| Eleva laco arine                                                                                                                                                                                                                                   |                  |

| Prof. Dr. Edson Ifarraguierre Moreno -                                                                                                                                                                                                             | FACIN/PUCRS      |

| 5                                                                                                                                                                                                                                                  |                  |

| Homologada em/, conforme Ata No pela Coordenadora.                                                                                                                                                                                                 | Comissão         |

|                                                                                                                                                                                                                                                    |                  |

|                                                                                                                                                                                                                                                    |                  |

#### **ACKNOWLEDGMENTS**

To my parents, Liamara and Moacir, for their continued support.

To my advisor, Dr. Ney L. V. Calazans, for the patience and guidance throughout the course of this research.

To Walter Lau Neto, for the assistance in the characterization tasks.

To my friends at GAPH and GSE for the helpful discussions and support throughout the Master's course.

To my girlfriend, Ana, for the love, support and patience.

# ANÁLISE DOS EFEITOS DE ESCALAMENTO DE TENSÃO NO PROJETO DE CIRCUITOS RESILIENTES

#### **RESUMO**

Embora o avanço da tecnologia de semicondutores permita a fabricação de dispositivos com atrasos de propagação reduzidos, potencialmente habilitando o aumento da frequência de operação, as variações em processos de fabricação modernos crescem de forma muito agressiva. Para lidar com este problema, significativas margens de atraso devem ser adicionadas ao período de sinais de relógio, limitando os ganhos em desempenho e a eficiência energética do circuito. Entre as diversas técnicas exploradas nas últimas décadas para amenizar esta dificuldade, três se destacam como relevantes e promissoras, isoladas ou combinadas: a redução da tensão de alimentação, o uso de projeto assíncrono e arquiteturas resilientes. Este trabalho investiga como a redução de tensão de alimentação afeta os atrasos de caminhos em circuitos digitais, e produz três contribuições originais. A primeira é a definição uma técnica para garantir que circuitos sintetizados com um conjunto reduzido de células atinjam resultados comparaveis aos da biblioteca completa, mantendo a sua funcionalidade mesmo quando alimentados por tensões reduzidas. A segunda é a composição de um método para estender o suporte a níveis de tensão de alimentação para bibliotecas de células padrão providas por fabicantes de Cls, através de novas técnicas de caracterização de bibliotecas. A terceira é a análise dos efeitos do escalamento de tensão no projeto de circuitos resilientes, considerando tensões de alimentação superiores e inferiores à tensão de limiar dos transistores.

**Palavras-Chave:** circuitos assíncronos, circuitos resilientes, escalamento de tensão, projeto de circuitos digitais, caracterização de bibliotecas de células padrão.

# ANALYSIS OF VOLTAGE SCALING EFFECTS IN THE DESIGN OF RESILIENT CIRCUITS

#### **ABSTRACT**

Although the advancement of semiconductor technology enable the fabrication of devices with increasingly reduced propagation delay, potentially leading to higher operating frequencies, manufacturing process variability grows very aggressively in modern processes. To cope with growing variability phenomena, significant delay margins need to be added to clock signal's periods, to ensure timing closure, which limits performance gains and constrains power efficiency. Among the several techniques that have been explored in the last decades to address these problems, three are quite relevant and promising either in isolation or combined: voltage scaling, asynchronous circuits and resilient architectures. This work investigates how voltage scaling affects circuit path delays, and produces three sets of original contributions. The first set establishes a technique to ensure that circuits synthesized with a reduced library achieve results comparable to the full library, while keeping functionality at low supply voltages. The second set of contributions composes a method to extend the voltage corners supported by standard cell libraries. This takes place through new library characterization techniques. The third set of contributions provides insights on the effects of voltage scaling in the design of resilient circuits. This analysis evaluates supply voltages in super- and sub-threshold levels.

**Keywords:** asynchronous circuits, resilient architectures, voltage scaling, digital circuit design, standard cell library characterization.

# **LIST OF FIGURES**

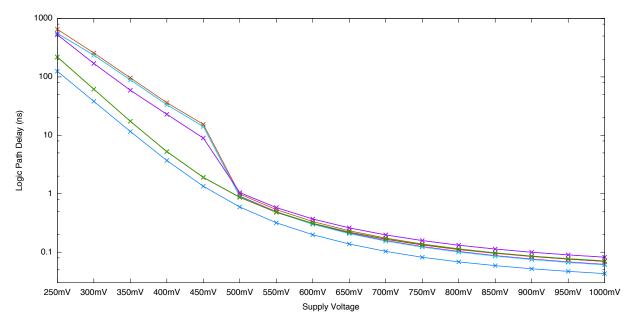

| Figure     | 1.1 – Logic path delays of the c17 circuit as a function of the supply voltage.                                                                                  | 24  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

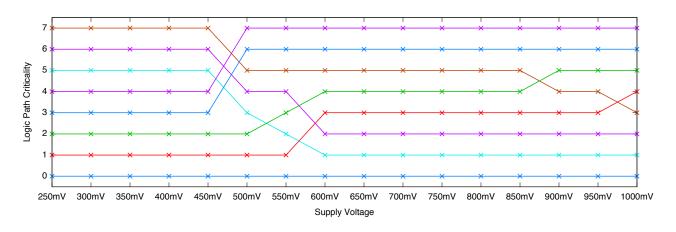

| Figure     | 1.2 - Path migration plot for the c17 circuit [HYH99]                                                                                                            | 25  |

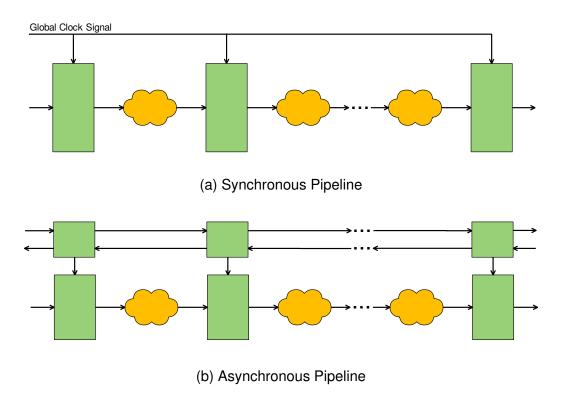

| Figure     | 2.1 – An abstract view of pipelines                                                                                                                              | 27  |

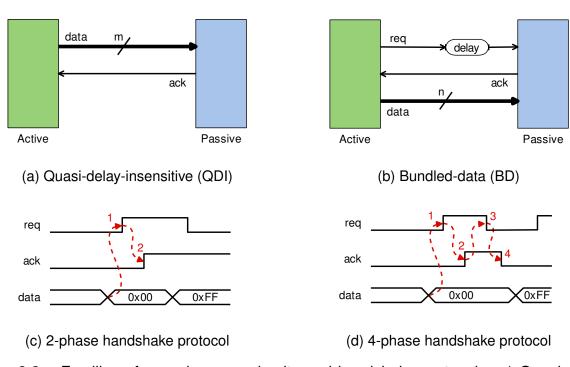

| Figure     | 2.2 - Families of asynchronous circuits and handshake protocols                                                                                                  | 28  |

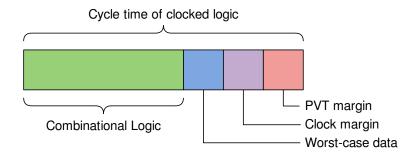

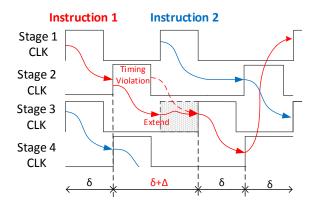

| Figure     | 2.3 - Timing margins on contemporary VLSI designs                                                                                                                | 30  |

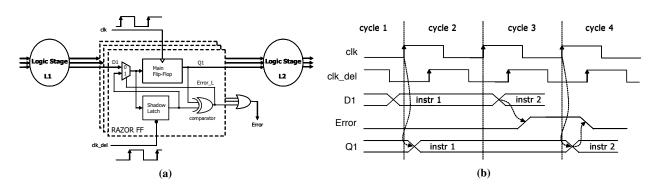

| Figure     | 2.4 - Overview of the Razor I Architecture                                                                                                                       | 30  |

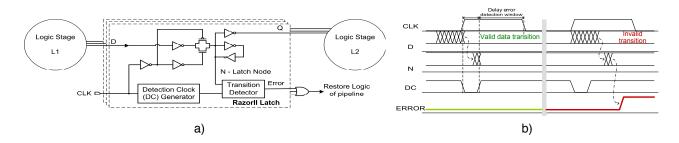

| Figure     | 2.5 - Razor II flip-flop design and operation                                                                                                                    | 32  |

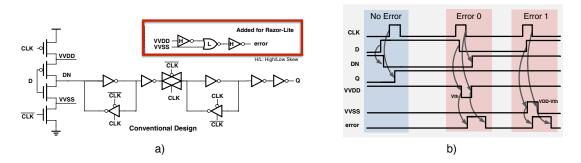

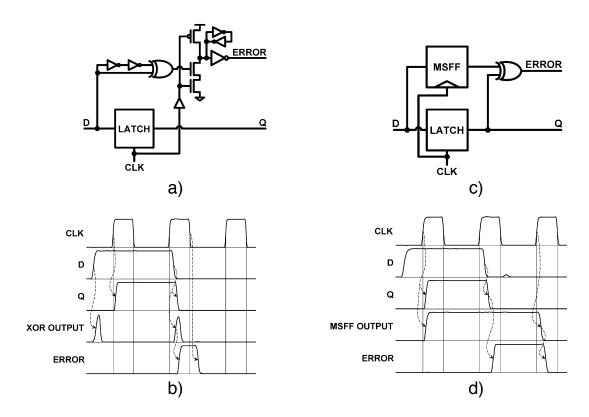

| Figure     | 2.6 - Razor-Lite error detector design and operation                                                                                                             | 33  |

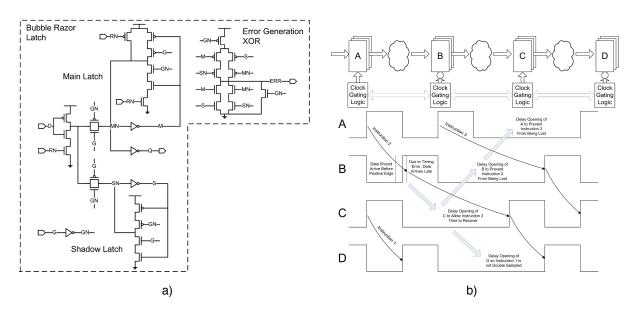

| Figure     | 2.7 - Bubble Razor Latch design and operation                                                                                                                    | 34  |

| Figure     | 2.8 - TDTB and DSTB register architecture and operation                                                                                                          | 35  |

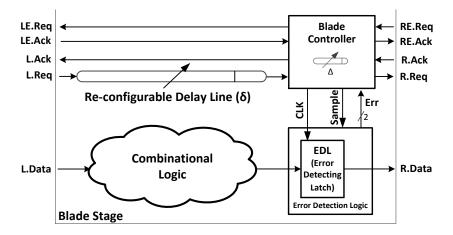

| Figure     | 2.9 - The Blade architecture                                                                                                                                     | 38  |

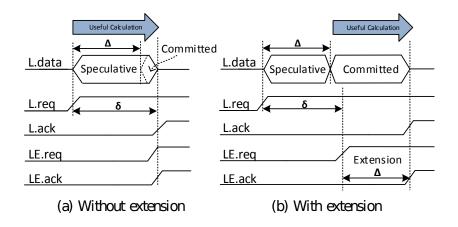

| Figure     | 2.10 - Speculative handshaking protocol                                                                                                                          | 39  |

| Figure     | 2.11 - Timing diagram of Blade                                                                                                                                   | 39  |

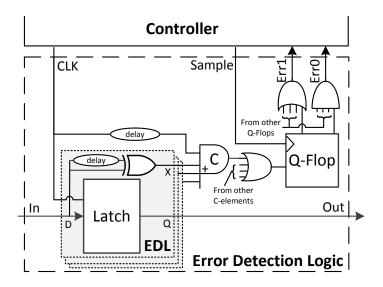

| Figure     | 2.12 – General structure of the error detection logic                                                                                                            | 40  |

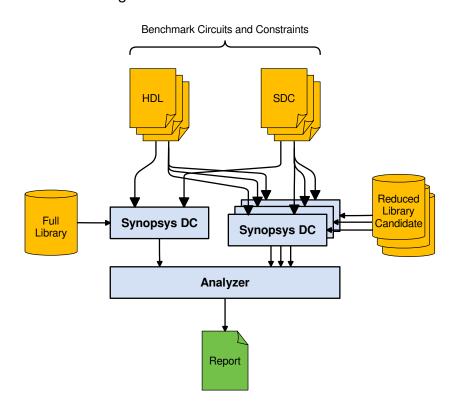

| Figure     | 3.1 - Automated synthesis environment used to compare performance re-                                                                                            |     |

|            | sults between the full library and the reduced library candidates                                                                                                | 44  |

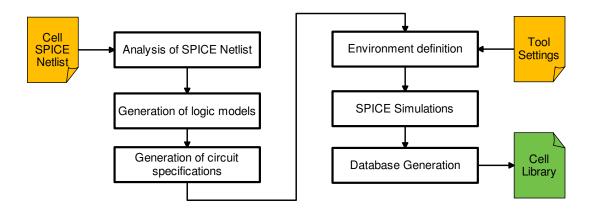

| Figure     | 4.1 - High-level view of the characterization flow                                                                                                               | 54  |

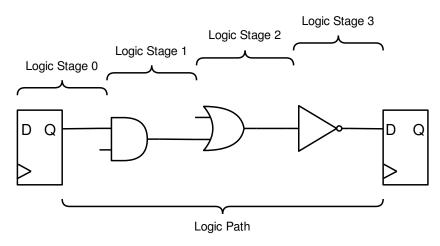

| Figure     | 4.2 – Illustration of the logic path definition                                                                                                                  | 55  |

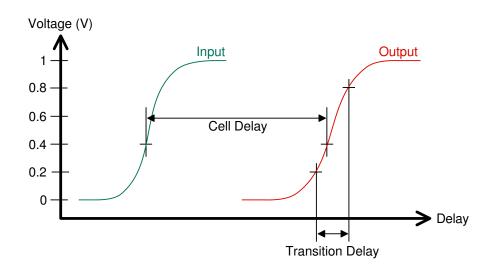

| Figure     | 4.3 - Illustration of cell and transition delays                                                                                                                 | 56  |

| Figure     | 4.4 - Waveform illustrating the SPICE simulations required to characterize                                                                                       |     |

|            | a rising input of an inverter                                                                                                                                    | 59  |

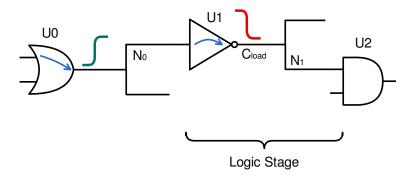

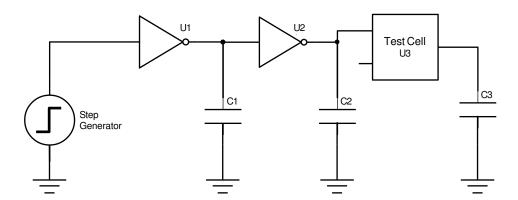

| Figure     | 4.5 – Circuit schematic of an example circuit used to compute cell delay                                                                                         |     |

| <b>-</b> · | with NLDM.                                                                                                                                                       | 59  |

| _          | 4.6 – High-level illustration of the structure of a technology library                                                                                           | 60  |

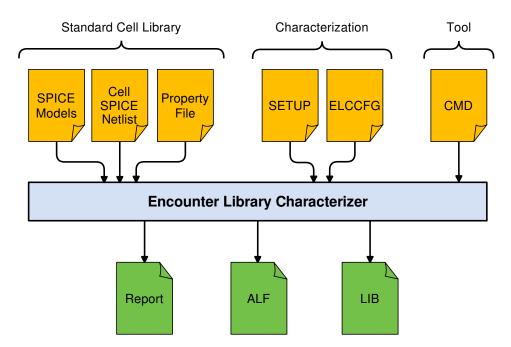

| •          | 4.7 – Inputs and outputs of Encounter Library Characterizer                                                                                                      | 61  |

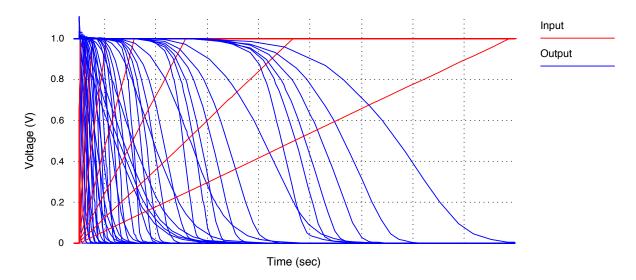

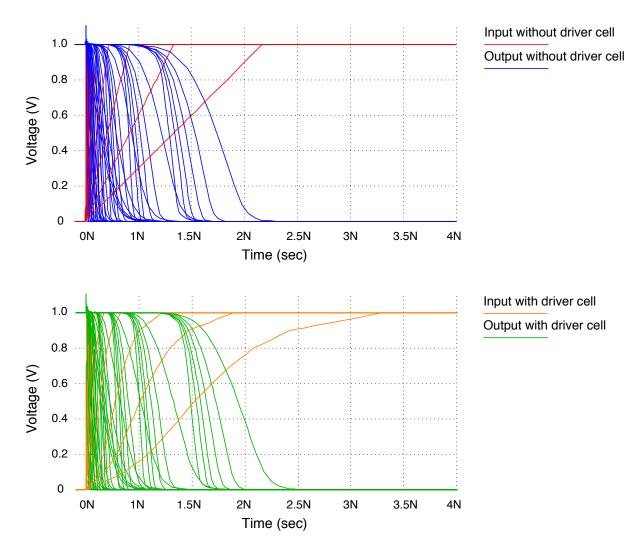

| Figure     | 4.8 — Waveforms illustrating the rising input characterization of an inverter, considering scenarios with linear and non-linear inputs                           | 64  |

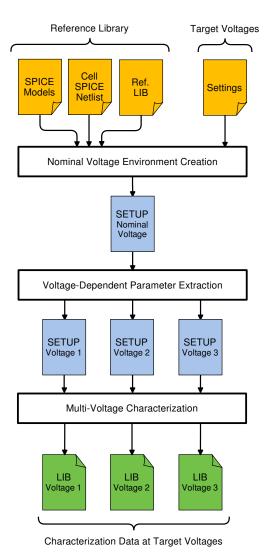

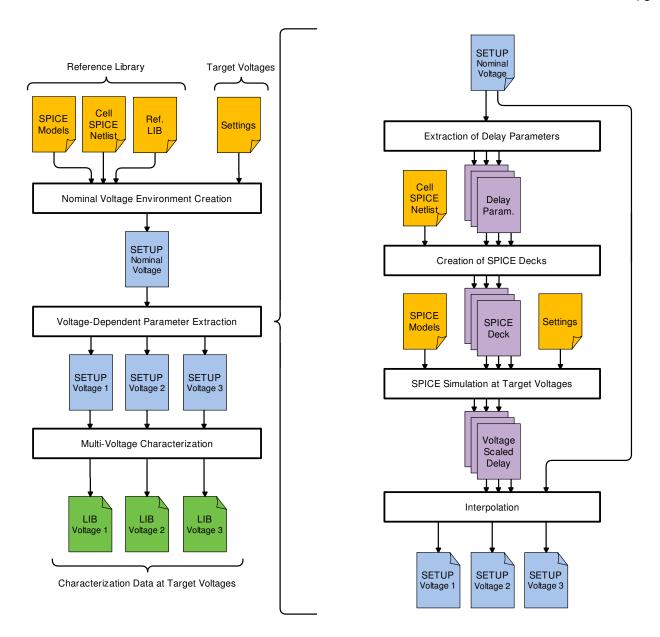

| Eiguro     |                                                                                                                                                                  | 67  |

| _          | <ul> <li>4.9 – Overview of the Multi-voltage Characterization Flow.</li> <li>4.10 – Detailed view of the Nominal Voltage Environment Creation task of</li> </ul> | 07  |

| rigure     | the MVC flow                                                                                                                                                     | 68  |

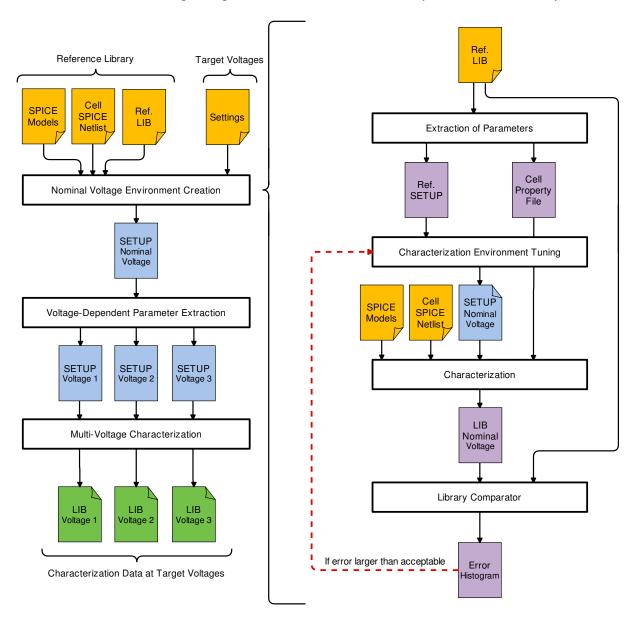

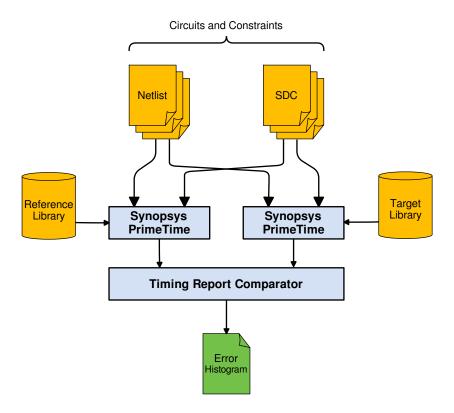

| Figure     | 4.11 – Automated environment used to compare data models from Liberty                                                                                            | -50 |

| 94.0       | libraries                                                                                                                                                        | 70  |

| Figure     | 4.12 – Generic SPICE deck employed in parameter scaling                                                                                                          | 71  |

| Figure 4.13 – Detailed view of the Voltage-Scaled Parameter Extraction task of the                                             |    |

|--------------------------------------------------------------------------------------------------------------------------------|----|

| Multi-voltage Characterization Flow                                                                                            | 73 |

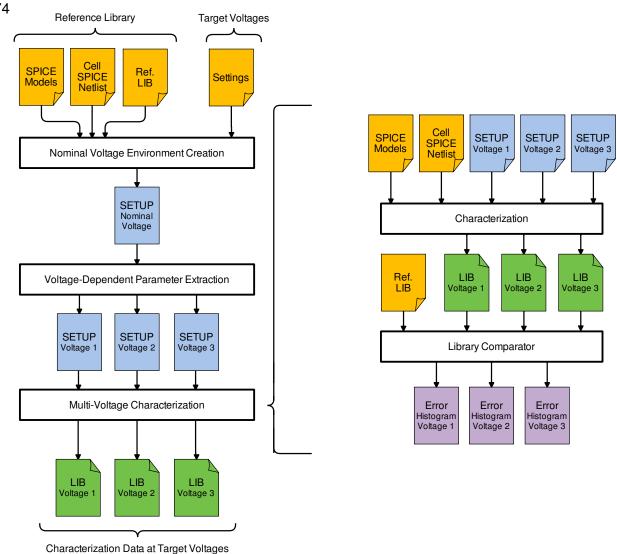

| Figure 4.14 - Detailed view of the Characterization task of the Multi-voltage Char-                                            |    |

| acterization Flow                                                                                                              | 74 |

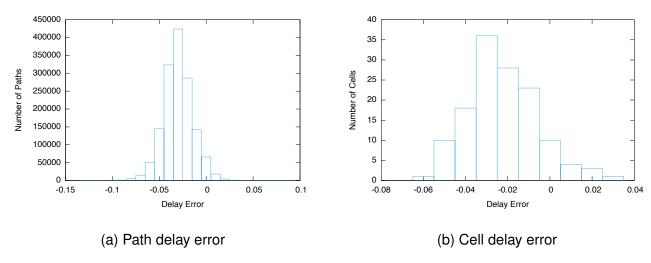

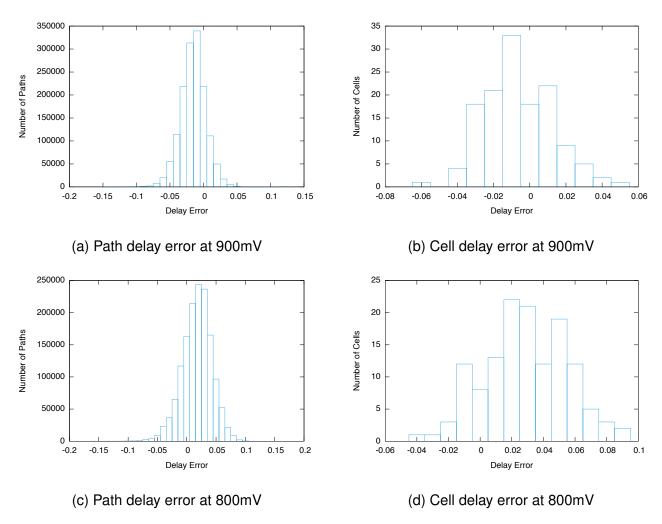

| Figure 4.15 – Error histograms comparing the reduced cell library characterization at nominal voltage to the reference library | 75 |

| Figure 4.16 - Error histograms comparing the 800mV and 900mV characteriza-                                                     |    |

| tions of the reduced cell library to the reference                                                                             | 77 |

| Figure 5.1 – Simplified model of CMOS inverter                                                                                 | 79 |

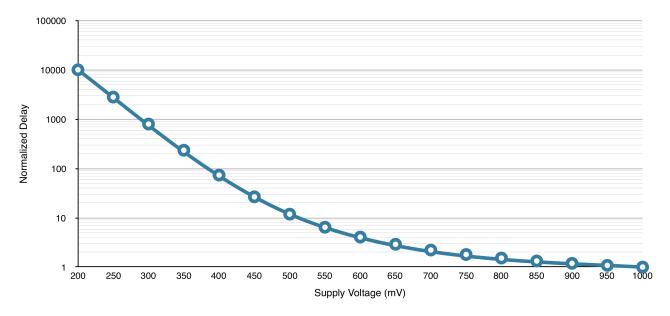

| Figure 5.2 - Plot of the normalized delay of a CMOS static inverter as a function                                              |    |

| of the supply voltage                                                                                                          | 81 |

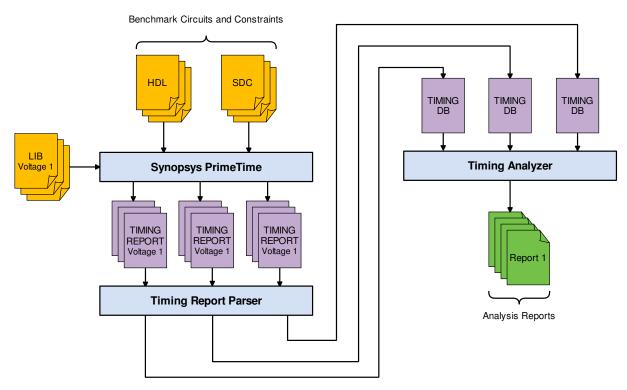

| Figure 5.3 - Path Analyzer (PA), an automated environment used to compute the                                                  |    |

| changes of path delays, considering a number of voltage corners                                                                | 83 |

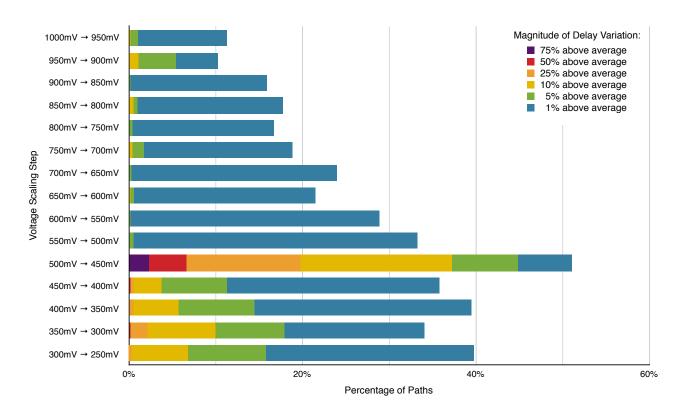

| Figure 5.4 - Magnitude distribution of logic path fluctuations for a range of voltage                                          |    |

| scaling steps                                                                                                                  | 85 |

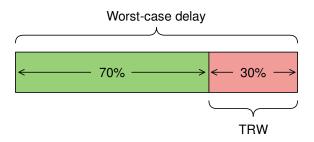

| Figure 5.5 - Representation of a timing resilience window (TRW) set to 30% of                                                  |    |

| the worst-case delay of a circuit                                                                                              | 87 |

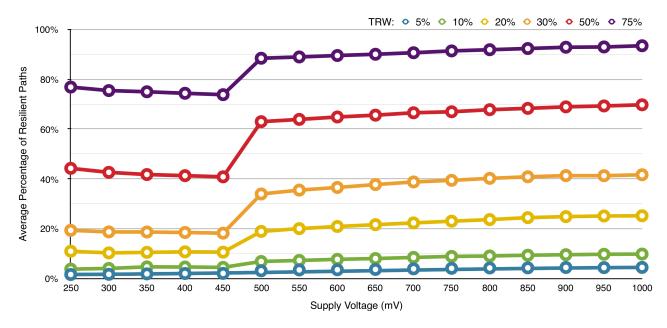

| Figure 5.6 - Average percentage of resilient paths for each TRW and voltage                                                    |    |

| corner analyzed                                                                                                                | 89 |

## **LIST OF TABLES**

| Table 2.1 – Summary of the state of the art in synchronous resilient architectures.                                                                                                                                                                                                                                                           | 37   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 3.1 – Description of the circuits used as benchmarks for evaluation of reduced library candidates. The number of cells was computed considering                                                                                                                                                                                         |      |

| the results of the synthesis with the full library. The acronyms SEC/DED                                                                                                                                                                                                                                                                      |      |

| stand for "single-error-correcting" and "double-error detecting", respectively.                                                                                                                                                                                                                                                               | 45   |

| Table 3.2 – List of cell functions from the full library sorted by the percentage of use in the benchmark circuits                                                                                                                                                                                                                            | 48   |

| Table 3.3 — Synthesis results for reduced library candidates based on the number                                                                                                                                                                                                                                                              |      |

| of inputs                                                                                                                                                                                                                                                                                                                                     | 50   |

| ·                                                                                                                                                                                                                                                                                                                                             |      |

| Table 3.4 — List of cells that compose the library of 3-input cells                                                                                                                                                                                                                                                                           | 51   |

| Table 4.1 – NLDM delay table for a falling output cell delay of an inverter. Delays                                                                                                                                                                                                                                                           |      |

| are in nanoseconds                                                                                                                                                                                                                                                                                                                            | 58   |

| Table 4.2 - Example of input slew scaling through cross-multiplication between                                                                                                                                                                                                                                                                |      |

| reference and scaled values                                                                                                                                                                                                                                                                                                                   | 72   |

| Table 4.3 – Scaled input slew vectors for reduced cell library obtained through cross-multiplication. Reference values (1000mV) obtained from characteri-                                                                                                                                                                                     |      |

| zation environment validated at the nominal voltage                                                                                                                                                                                                                                                                                           | 76   |

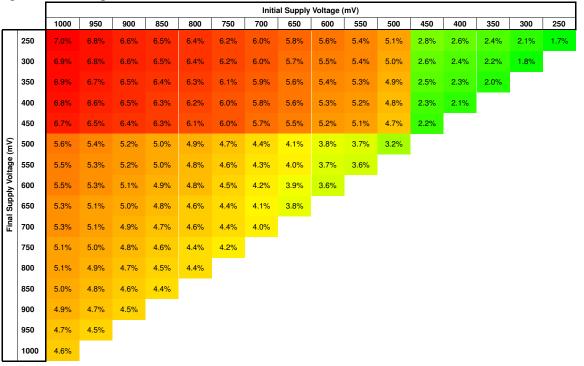

| Table 5.1 – Average percentage of resilient paths $(\overline{PRP_{VS}})$ for a given range of voltage scaling, considering a 10% TRW. The Table shows the results for all possible ranges of voltage scaling from 1V to 250mV in 50mV steps. Each cell is colored according to the $\overline{PRP_{VS}}$ magnitude – red denote large values |      |

| and green indicate small values                                                                                                                                                                                                                                                                                                               | 91   |

| Table A.1 – Average percentage of resilient paths $(\overline{PRP_{VS}})$ for a given range of                                                                                                                                                                                                                                                |      |

| voltage scaling, considering a 5% TRW                                                                                                                                                                                                                                                                                                         | 101  |

| Table A.2 – Average percentage of resilient paths ( $\overline{PRP_{VS}}$ ) for a given range of voltage scaling, considering a 20% TRW                                                                                                                                                                                                       | 102  |

|                                                                                                                                                                                                                                                                                                                                               | . 0_ |

| Table A.3 – Average percentage of resilient paths $(\overline{PRP_{VS}})$ for a given range of voltage scaling, considering a 30% TRW                                                                                                                                                                                                         | 102  |

| Table A.4 – Average percentage of resilient paths ( $\overline{PRP_{VS}}$ ) for a given range of voltage scaling, considering a 50% TRW                                                                                                                                                                                                       | 103  |

| Table A.5 – Average percentage of resilient paths ( $\overline{PRP_{VS}}$ ) for a given range of                                                                                                                                                                                                                                              |      |

| voltage scaling, considering a 75% TRW                                                                                                                                                                                                                                                                                                        | 103  |

#### LIST OF ACRONYMS

ALF – Advanced Library Format

ASIC - Application-specific Integrated Circuit

BD - Bundled-data

CSM - Current Source Models

DI - Delay Insensitive

DSM - Deep Submicron

DSTB - Double Sampling With Time Borrowing

DVFS - Dynamic Voltage and Frequency Scaling

EDA - Electronic Design Automation

EDL - Error Detecting Latches

ELC - Encounter Library Characterizer

FF - Flip-flop

HDL - Hardware Description Language

IC – Integrated Circuit

IOT – Internet of Things

IP – Intellectual Property

LC – Library Comparator

MSFF - Master-Slave Flip-Flop

MVC - Multi-Voltage Characterization

NLDM - Non-linear Delay Model

PA - Path Analyzer

PRP – Average Percentage of Resilient Paths

PVT - Process, Voltage, and Temperature

PWL - Piecewise Linear

QDI - Quasi-Delay-Insensitive

RC – Resistance and Capacitance

STA – Static Timing Analysis

TDTB – Transition Detector With Time Borrowing

TRW – Timing Resilience Window

# **CONTENTS**

| INTRODUCTION                                                             | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOTIVATION AND OBJECTIVES                                                | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CONTRIBUTIONS                                                            | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DOCUMENT STRUCTURE                                                       | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ASYNCHRONOUS CIRCUITS AND RESILIENT ARCHITECTURES                        | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ASYNCHRONOUS CIRCUITS                                                    | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RESILIENT ARCHITECTURES                                                  | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| STATE OF THE ART ON SYNCHRONOUS RESILIENT ARCHITECTURES                  | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RAZOR I                                                                  | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RAZOR II                                                                 | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RAZOR-LITE                                                               | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BUBBLE RAZOR                                                             | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TDTB AND DSTB                                                            | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DISCUSSION                                                               | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BLADE                                                                    | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DESIGN OF RESILIENT CIRCUITS                                             | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SELECTION OF A REDUCED CELL LIBRARY                                      | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| REDUCED CELL LIBRARY CRITERIA AND EVALUATION METRICS                     | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BENCHMARK CIRCUITS                                                       | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SELECTION OF STANDARD CELLS                                              | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| APPROACH 1: SELECTION BASED STATISTICAL ANALYSIS OF CELL USAGE           | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| APPROACH 2: SELECTION BASED ON THE NUMBER OF INPUTS                      | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LIBRARY OF 3-INPUT CELLS                                                 | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CELL LIBRARY CHARACTERIZATION                                            | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BACKGROUND                                                               | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ELECTRICAL CHARACTERIZATION OF STANDARD CELLS AND DELAY IN CIRCUIT PATHS | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TECHNOLOGY LIBRARIES                                                     | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ENCOUNTER LIBRARY CHARACTERIZER                                          | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MULTI-VOLTAGE CHARACTERIZATION FLOW                                      | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                          | MOTIVATION AND OBJECTIVES CONTRIBUTIONS DOCUMENT STRUCTURE  ASYNCHRONOUS CIRCUITS AND RESILIENT ARCHITECTURES ASYNCHRONOUS CIRCUITS RESILIENT ARCHITECTURES STATE OF THE ART ON SYNCHRONOUS RESILIENT ARCHITECTURES . RAZOR I RAZOR II RAZOR-LITE BUBBLE RAZOR TOTB AND DSTB DISCUSSION BLADE DESIGN OF RESILIENT CIRCUITS  SELECTION OF A REDUCED CELL LIBRARY REDUCED CELL LIBRARY CRITERIA AND EVALUATION METRICS BENCHMARK CIRCUITS SELECTION OF STANDARD CELLS APPROACH 1: SELECTION BASED STATISTICAL ANALYSIS OF CELL USAGE APPROACH 2: SELECTION BASED ON THE NUMBER OF INPUTS LIBRARY OF 3-INPUT CELLS  CELL LIBRARY CHARACTERIZATION BACKGROUND ELECTRICAL CHARACTERIZATION OF STANDARD CELLS AND DELAY IN CIRCUIT PATHS TECHNOLOGY LIBRARIES ENCOUNTER LIBRARY CHARACTERIZER |

| 4.2.1 | NOMINAL VOLTAGE ENVIRONMENT CREATION                                         | 67  |

|-------|------------------------------------------------------------------------------|-----|

| 4.2.2 | VOLTAGE-DEPENDENT PARAMETER EXTRACTION                                       | 70  |

| 4.2.3 | MULTI-VOLTAGE CHARACTERIZATION AND VALIDATION                                | 72  |

| 4.3   | CASE-STUDY: MULTI-VOLTAGE CHARACTERIZATION OF REDUCED CELL                   |     |

|       | LIBRARY                                                                      | 73  |

| 5     | TIMING ANALYSIS OF CIRCUITS UNDER VOLTAGE SCALING                            | 79  |

| 5.1   | RELATED WORK                                                                 | 81  |

| 5.2   | ANALYSIS ENVIRONMENT                                                         | 82  |

| 5.3   | BEHAVIOR OF LOGIC PATHS UNDER VOLTAGE SCALING                                | 84  |

| 5.4   | VOLTAGE SCALING EFFECTS ON RESILIENT ARCHITECTURES                           | 87  |

| 5.5   | EFFECTS OF VOLTAGE SCALING IN THE DESIGN OF RESILIENT CIRCUITS               | 92  |

| 6     | CONCLUSIONS                                                                  | 95  |

| 6.1   | FUTURE WORK                                                                  | 95  |

|       | REFERENCES                                                                   | 97  |

|       | <b>APPENDIX A</b> – Supplementary results for $\overline{PRP_{VS}}$ analysis | 101 |

#### 1. INTRODUCTION

The first wave of the mobile revolution led to the ubiquity of battery-powered portable devices. These devices, which are usually based on the synchronous circuit design paradigm, are required to deliver good autonomy while performing complex tasks that demand high performance computing. Wearable devices and Internet of Things (IoT) applications, which, according to [Zod15], are part of the next wave of the mobile revolution, have very different requirements. Unlike most mobile devices, which can be recharged on a daily basis, wearables and battery-powered IoT applications can have a very strict power budget, as these products could be subjected to energy-starved environments. Due to this characteristic, such applications are good candidates for ultra-low power sub-threshold operation [Vit15, CCGC13].

Albeit transistors become faster as technology nodes advance, allowing smaller gate delays and potentially leading to higher operating frequencies, manufacturing process variability also grows aggressively [JCDGH15]. In this way, delay uncertainties, which arise from such variations, begin to challenge synchronous designers. To cope with that, increasingly large delay margins need to be added to the period of clock signals to ensure timing constraints closure, limiting performance gains and constraining power efficiency. Low power requirements tend to further increase variations, which may lead to additional delay guardbands [JCDGH15]. Among the several techniques that have been explored in the last decades to address these problems, three are quite relevant and promising: voltage scaling, asynchronous circuits, and resilient architectures. The former is a classic technique, usually employed to reduce power consumption by diminishing the supply voltage of the circuit. It relies on the fact that power is directly proportional to the square of the voltage and, together with dynamic frequency scaling, is employed in many modern processors [KSSF10, ZGC+12, KKLR11]. Asynchronous circuits remove the need for a global clock signal, potentially reducing power consumption and electromagnetic interferences caused by periodic signal [BOF10]. Resilient architectures allow removing delay margins and tolerate timing errors to mitigate variability, which enables circuits to operate with relaxed timing constraints [EKD+03]. Due to the less strict timing margins, resilient circuits supporting voltage scaling could potentially provide higher performance at nominal voltage by allowing the circuit to operate close to average-case delay. These can also provide larger power savings when operating at supply levels lower than the minimum error-free voltage, which is possible due to the resilience to timing errors.

In the context of mobile devices, wearables, and IoT, resilient architectures supporting voltage scaling could bring benefits to each of these classes of application. The former class can leverage from the performance gains at nominal voltage. The remaining ones can benefit from operating at lower supply voltages – which can increase the energy efficiency

of the circuit. Yet, synchronous resilient architectures are prone for failures due to metastability [BCC+14] and can exhibit high penalties due to error recovery based on architectural replay [JCDGH15]. This issues can be overcome by asynchronous resilient architectures, such as Blade.

This work proposes as novelty to investigate how the reduction of supply voltage affects circuit path delays, providing insight on the effects of voltage scaling in resilient circuits. To enable this investigation, a method to extend the voltage corners supported by standard cell libraries was devised, along with a technique for establishing reduced cells libraries that present performance levels similar to the full libraries while ensuring proper operation at low supply voltages.

### 1.1 Motivation and Objectives

Blade [HMH+15, HHC+15] is a novel asynchronous resilient circuit architecture that seeks to overcome the problems with current synchronous resilient architectures, providing low error-recovery overhead and metastability-tolerant operation. Its development is a partnership between the University of Southern California (USC), in Los Angeles (USA), and the GAPH group at PUCRS. Part of the research work conducted by the Author during his MSc course targeted the development of Blade. Since Blade is a new approach for circuit design, there are many open problems and interesting research areas related to it. In this context, this work aims to understand how digital circuits behave under voltage scaling, providing insight on how reduced supply voltages affect resilient circuit design. Even though this study focuses on Blade, some analysis can be extended to synchronous resilient architectures.

Figure 1.1 – Plot depicting the logic path delays of the c17 ISCAS'85 benchmark [HYH99] as a function of the supply voltage. The maximum delay of the eight paths that compose the circuit are shown.

It is well known that the delays of logic paths in a digital circuit increase as the supply voltage scales down. For instance, consider Figure 1.1, which plots the logic path delays of a circuit as a function of the supply voltage. Each line on the plot depicts the maximum delay of one of the eight logic paths obtained in a post-synthesis netlist of the c17 ISCAS'85 benchmark [HYH99]. In this plot, one can measure the rate at which the circuit delay increases as the supply voltage reduces. In addition, an interesting behaviour of the critical path can be observed: at the threshold region (around 450-500mV), the critical path of the circuit changes. From 1V to 500mV, the critical path is that represented by the purple line. For voltages below 500mV, the path depicted in brown becomes the critical one. Another way to visualize this behaviour is through the path migration plot, illustrated in Figure 1.2. This plot depicts the logic path delays of the circuit ranked by their criticality at each supply voltage - higher criticality levels indicate paths with larger delays. The change of critical path can be clearly seen by looking at the behaviour of the path depicted in brown. Its delay gradually increases in relation to the other paths, causing it to become the critical path when the threshold is crossed (i.e. for supply voltages of 450mV and below). The migration plot of this circuit shows that the logical path criticality can change as supply voltage scales. One of the goals of this work is to evaluate how these path fluctuations affect the design of resilient circuits. The data depicted in Figures 1.1 and 1.2 was extracted using the analysis environment detailed in Section 5.2.

Figure 1.2 – Path migration plot illustrating the logic path fluctuation on the the c17 benchmark [HYH99]. For each supply voltage, the maximum delays of the eight paths that compose the circuit are ranked according their criticality.

To enable circuits to operate with relaxed timing constraints, resilient architectures implement specialized hardware to detect and correct timing violations in a transparent manner. To avoid prohibitively large area overheads, error detection logic is traditionally implemented only in critical and near-critical paths. In this context, the main objective of this work is to understand the impact of logic path fluctuations due to voltage scaling in resilient circuit design.

#### 1.2 Contributions

The contributions of this work can be summarized in three items: i) a method to select reduced standard cell libraries; ii) the multi-voltage characterization flow; iii) the timing analysis of digital circuits under voltage scaling. These contributions are briefly sketched in this Section.

#### Method to select reduced standard cell libraries

This first contribution guarantees that circuits synthesized with the reduced library achieve timing and area results comparable to the full library, while keeping circuit functionality at low/very low supply voltages.

#### Multi-voltage characterization flow

This flow is a method designed to extend the voltage corners supported by standard cell libraries. It provides a systematic way to characterize libraries to a wide range of target voltages, ensuring the proper scaling of voltage-dependent parameters.

#### Timing analysis of circuits under voltage scaling

The main contribution of this work is the study of logic path behavior under voltage scaling. This investigation helps understand how supply voltage reduction affects path delays, providing insight on how changes in logic path criticality impacts the design of resilient circuits.

#### 1.3 Document Structure

The remaining of the document is organized as follows. Chapter 2 provides relevant background information on asynchronous circuits and resilient architectures. The method used to select the reduced cell library that is used throughout this work is detailed in Chapter 3. Chapter 4 discusses standard cell characterization and describes the multi-voltage characterization flow. The main contribution of this work is explored in Chapter 5. Chapter 6 presents some final remarks and directions for future work.

# 2. ASYNCHRONOUS CIRCUITS AND RESILIENT ARCHITECTURES

This Chapter presents basic concepts on asynchronous circuits and resilient architectures necessary to the understanding of this work in Sections 2.1 and 2.2. Section 2.3 presents and discusses the state of the art in synchronous resilient architectures. Section 2.4 introduces Blade, a novel asynchronous resilient architecture that seeks to overcome the problems with current synchronous resilient architectures. Finally, Section 2.5 provides a discussion about the design of resilient circuits.

### 2.1 Asynchronous Circuits

Figure 2.1 - An abstract view of pipeline implementations of digital circuits: (a) a synchronous pipeline; (b) an asynchronous pipeline. Adapted from [NS11].

Events in sequential digital systems are traditionally synchronized by a global clock signal. In such implementations, as Figure 2.1(a) illustrates, the clock signal is designed to update all registers simultaneously – thus, creating a *synchronous* circuit. *Asynchronous* circuits, on the other hand, do not employ global synchronization. Instead, local handshakes between neighbour registers control the synchronization and sequencing of events [BOF10]. In an asynchronous pipeline like the one depicted in Figure 2.1(b), the operation of each register depends only on the previous and following registers – i.e. there is no control signal

commanding all registers. The discrete-time abstraction created by synchronous implementations helps simplifying the design, but removing it can grant several other benefits, like lower power consumption, higher operating speed, lower electromagnetic noise emission, and the elimination of clock distribution problems [Hau95].

Differently from synchronous circuits, asynchronous circuits can be designed using different data encoding schemes and handshake protocols [BOF10]. A choice of handshake protocol and data encoding scheme is called a design template or simply a template. Current practical asynchronous design templates can be classified in two main families: Quasi-delayinsensitive (QDI) and Bundled-data (BD) [BOF10]. The key characteristic of QDI designs is the use of multi-rail delay insensitive (DI) data encoding. An example is dual-rail, which uses two wires to represent one bit of data - and completion-sensing circuits to determine data validity [BOF10]. The example of Figure 2.2(a) uses the use of an n-of-m delay insensitive code, where each pattern with n bits at '1' in the m wires of the data channel represents a valid information. For example, if m=3 and n=2, the 2-of-3 resulting code can represent 3 different pieces of information (011, 101, 110) in a delay insensitive way. The passive block (on the right hand side) uses special circuitry to sense when the data is one of the valid 3-bit combination, thus inferring a request event from the active block. Even though QDI provides relaxed timing constraints, circuits from this class are usually power and area hungry. For this reason, this work restricts attention to BD circuits, which are implemented with singlerail encoding (i.e. the traditional Boolean encoding, where n bits can represent 2<sup>n</sup> different pieces of information). This provides lower overhead and is less constraining with regard to the use of conventional standard-cell libraries and EDA tools for synthesis purposes.

Figure 2.2 – Families of asynchronous circuits and handshake protocols: a) Quasi-delayinsensitive (QDI) circuit using an n-of-m DI code; b) Bundled-data (BD) circuit; c) 2-phase handshake protocol; d) 4-phase handshake protocol.

BD circuits often use an explicit pair of sideband control signals (request and acknowledge) to provide synchronization. Since single-rail data encoding is used, BD requires a number of timing assumptions to ensure proper circuit operation. These timing assumptions lead to constraints to guarantee that combinational circuits have enough time to compute, while respecting setup and hold times of registers. Ensuring constraints usually happens by adding delay lines in front of control signals to match the logic path delay. This has as goal to guarantee that handshake events only take place when data signals are stable at the input of the next stage's register(s). As an example, refer to Figure 2.2(b): the delay line inserted in the reg signal ensures that the passive block will only receive the request event after the signals at its data input become stable. BD designs exist using both 2- and 4phase handshake protocols, which are illustrated, respectively, in Figures 2.2(c) and 2.2(d). 4-phase protocols have a return to zero (RTZ) (or to one, RTO) phase (transitions 3 and 4 in Figure 2.2(d) for an RTZ protocol) that increases the number of events necessary to complete a handshake, potentially reducing the performance of the circuit. 2-phase protocols improve performance, by eliminating the return phase, at the expense of more complex control circuitry. BD templates can use different design styles for implementing their control blocks. 2-phase BD control circuits were pioneered by Ivan Sutherland, who introduced the concept of micropipelines [Sut89], implemented with special capture-pass latches capable of sensing transitions at its inputs. A more recent approach is Mousetrap [SN07], which implements 2-phase BD circuits using level-sensitive latches and XOR gates. Nowick and Singh propose a very good overview of these and other classical and modern asynchronous pipelines in [NS11].

#### 2.2 Resilient Architectures

As silicon technology advances into the deep submicron (DSM) range, manufacturing variability becomes an increasing concern to circuit designers. To ensure good yield on contemporary processes, circuit designers add delay margins to account for process, voltage, and temperature (PVT) variations. Figure 2.3 illustrates how these margins, along with clock-related and data-dependent margins can increase the minimum cycle time of clocked logic. As an alternative to cope with PVT variations on synchronous circuits, resilient design techniques help removing the increasingly large delay margins, allowing circuits to operate with relaxed timing constraints. These techniques allow timing violations to occur, and rely on dynamic error recovery mechanisms to correct errors derived from such violations. Resilient architectures are usually implemented with special error detecting registers, capable of flagging when timing violations occur, and architectural mechanisms for error recovery, such as pipeline stalls or architectural replay. A number of resilient architectures have been proposed to date [EKD+03, DTP+09, FFK+13, KKFK13, HMH+15].

Figure 2.3 – Timing margins in contemporary VLSI designs.

Razor [EKD+03], also called Razor I, is a first successful family of resilient architectures and serves as a good case to explore how such architectures work. Figure 2.4(a) depicts the Razor I basic implementation, which relies on a special register called Razor Flip-flop (FF). This FF replaces selected FFs on delay-critical paths from an original, non-resilient architecture. A Razor FF combines a regular FF with a shadow latch controlled by a delayed clock signal. The delayed clock clk\_del is designed to meet the latch setup time in worst-case situations, guaranteeing data validity at the latch input at any clk\_del rising edge, even if and when the main flip-flop timing is violated. Timing violations are detected by comparing the values stored in the main FF and in the shadow latch. When delay failures occur, the value stored in the latch is used to correct the violation.

Figure 2.4 – Overview of the Razor I Architecture: (a) pipeline with Razor latches and control lines; (b) operation of a Razor I circuit. Adapted from [EKD+03].

Figure 2.4(b) illustrates the operation of a rising edge sensitive Razor FF. In the first clock cycle, the timing requirements of the main FF are met, and correct values are stored in both the main FF and in the shadow latch. In this scenario, the error signal coming from the comparator remains low, and the circuit operates without interruptions. In cycle 2, the combinational path time exceeds the allotted time and an incorrect value is stored in the main FF. Once the correct value is sampled in the shadow latch, at the start of cycle 3, the error signal is asserted. This causes the value stored in the shadow latch to be used as the input to the main FF. At the beginning of cycle 4, the correct value is stored in the main FF. Once a timing violation occurs in some clock cycle, the data on the following pipeline stage must be flushed in the next clock cycle, to avoid the propagation of incorrect data – this

accounts for the one cycle recovery penalty. In addition, the previous pipeline stage must be stalled for one cycle while the data from the shadow latch is restored into the main FF. Razor I operation relies on the assumption that worst-case situations are data-dependent and rarely occur. By allowing the circuit to tolerate timing failures, it is possible to reduce the circuit design margins, improving the average-case performance.

The error rate of a resilient circuit is a key design parameter, as it can determine if the circuit will deliver the desired performance improvements or if the error recovery overheads will dominate. The optimum error-rate is application- and circuit-dependent and can be set at design time, by post-silicon tuning, or during operation, using Dynamic Voltage and Frequency Scaling (DVFS) techniques.

## 2.3 State of the Art on Synchronous Resilient Architectures

This Section presents an overview of the current literature on synchronous resilient circuits, covering Razor-based architectures and alternative approaches.

#### 2.3.1 Razor I

The Razor I architecture [EKD+03] was originally proposed as a technique to enable larger energy savings on circuits operating with dynamic voltage scaling (DVS). As mentioned in Section 2.2, the error rate is a key design parameter of a resilient circuit, specially considering the large error correction cost in a Razor I circuit, which can be about 18 times more expensive in terms of energy than regular operation [EKD+03], as in the case of a 64-bit Kogge-Stone adder. Based on experiments, a target error rate of 1.5% was selected for that circuit, allowing average energy savings of 41% with a maximum performance slowdown of 6% for the set of simulated benchmarks. A 64-bit Alpha processor employing the Razor I error detection and recovery mechanism was manufactured in 0.18 µm technology. The circuit was designed to operate at 200MHz, and the shadow latch clock was delayed by half clock cycle. Out of a total of 2408 flip-flops, 198 timing-critical flops were replaced with Razor FFs. The prototype presented an energy overhead of up to 3.1% due to the added logic when operating at nominal voltage.

#### 2.3.2 Razor II

Razor II [DTP+09] simplifies the FF design proposed on the original Razor by removing the error recovery mechanism. The motivation behind this approach is that the

error rate at the point of first failure is in the order of 1 error in 10 million cycles, which makes error-correction energy negligible. Therefore, Razor II FF performs only error detection and error recovery takes place through architectural replay. The new FF, depicted in Figure 2.5(a), uses a single latch combined with a transition detector, operating as a positive-edge-triggered FF. Figure 2.5(b) exemplifies the Razor II FF operation: *i)* when data stabilizes before the rising edge of the clock no error is flagged, as illustrated by the scenario on the left side of Figure 2.5(b); *ii)* if a transition occurs after the rising edge of the clock, while the latch is transparent, the FF detects the transition and asserts the error signal, as shown on the right side of Figure 2.5(b). When an error occurs, the whole pipeline is flushed and the failing instruction is re-executed. In case of successive failures, the clock frequency is reduced by half during 8 cycles. A 64-bit 7-stage Alpha processor featuring Razor II was manufactured in 0.13 µm technology. Energy savings of up to 37.4% were obtained when the processor was kept with an error rate of 0.04%, compared to the energy consumption when the supply voltage is set to ensure correct operation with a 10% margin.

Figure 2.5 – Razor II operation: a) Example of a Razor II pipeline section and details of the Razor II flip-flop; b) Waveform exemplifying the operation of a Razor II circuit. Extracted from [DTP+09].

#### 2.3.3 Razor-Lite

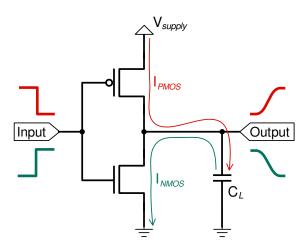

Razor-Lite [KKFK13] uses a side-channel transition detection approach, compatible with standard D FFs, as a way to reduce overheads due to error detection mechanisms. This approach allows the implementation of resilience on well-balanced pipelines, where a large number of FFs must be capable of detecting timing violations, with reasonable overhead. Figure 2.6(a) illustrates a conventional flip-flop design and the added logic (inside the red box) required by Razor-Lite. The added circuit connects to the virtual VDD (VVDD) and VSS (VVSS) rails of the FF, acting as a transition detector. Under normal operation (i.e. no error), as illustrated in the left box of Figure 2.6(b), the virtual rails voltage is kept stable after the rise transition of the clock and no error is flagged. When, after the rising edge of the clock, the input data 'D' transitions to '0', the following takes place, as depicted in the center box of Figure 2.6(b): i) before the data transition, 'VVDD' is charged to VDD, 'VVSS' is grounded,