#### PONTIFÍCIA UNIVERSIDADE CATÓLICA DO RIO GRANDE DO SUL FACULDADE DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

# ASYNCHRONOUS CIRCUITS: INNOVATIONS IN COMPONENTS, CELL LIBRARIES AND DESIGN TEMPLATES

#### **MATHEUS TREVISAN MOREIRA**

Dissertation submitted to the Pontifícia Universidade Católica do Rio Grande do Sul in partial fullfillment of the requirements for the degree of PhD in Computer Science.

Advisor: Prof. Dr. Ney L. V. Calazans

Co-Advisor: Prof. Dr. Peter A. Beerel (University of Southern California)

# REPLACE THIS PAGE WITH THE LIBRARY CATALOG PAGE

# REPLACE THIS PAGE WITH THE COMMITTEE FORMS

To Moreira.

- "- Would you tell me, please, which way I ought to go from here?

- That depends a good deal on where you want to get to.

- I don't much care where.

- Then it doesn't matter which way you go. "(Lewis Carroll, Alice in Wonderland)

#### **ACKNOWLEDGMENTS**

Gostaria de agradecer aos meus pais, Alda e Edi, e à minha irmã, Manu, pelo apoio, amor e carinho recebidos em toda minha trajetória até aqui. Obrigado, mãe, por sempre tentar entender o que eram essas tais de "ligações assíncronas". Amo vocês. À Liana, meu amor e minha companheira, obrigado por sempre estar ao meu lado. Foram muitas noites longas e finais de semana no laboratório dedicados ao desenvolvimento desse trabalho e tu sempre foste compreensiva e me apoiaste. Obrigado por ser essa pessoa que deixa meus dias mais alegres e por me ajudar a seguir crescendo e buscando meus objetivos, sempre de mãos dadas contigo. Te amo. Agradeço também aos meus amigos que sempre me ajudaram a lembrar que existe vida fora do laboratório. Obrigado por todos os momentos divertidos fazendo barulho com nossas bandas e assando uma carne.

Agradeço do fundo do meu coração ao Ney, que sempre confiou no meu trabalho e que, ao longo desses quase 8 anos de orientação, tornou-se, mais que um orientador, um mentor e um amigo. Obrigado por todas oportunidades e pelo teu tempo em todas as reuniões e discussões. Obrigado também pelos passeios por Los Angeles e Santa Monica e por me receber na tua casa junto à tua família. À Karin e às gurias, muito obrigado pelo carinho, pelas discussões filosóficas e pelas risadas. Agradeço também ao Moraes, que me acompanha desde a época do curso de engenharia e sempre esteve disponível para minhas conversas de "1 minutinho". Muito obrigado por todas as discussões técnicas, pelas oportunidades no GAPH e por sempre motivar meu amor pela microeletrônica.

Ao Marcon, meu padrinho de formatura e mentor, muito obrigado por todas conversas e risadas. Te agradeço pela sinceridade e por me ajudar a buscar meu caminho ao longo do meu desenvolvimento acadêmico, profissional e pessoal. Ah! Obrigado por me ensinar a diferença entre o certo e o justo. Agradeço também ao Fabiano por todas discussões extremamente produtivas. Obrigado por abrir meus olhos para outros lados da pesquisa e por todo apoio e motivação. Obrigado ao Julian por guiar meus primeiros passos na pesquisa e na microeletrônica. Tu foste uma pessoa fundamental na minha vida profissional e és um querido amigo. Te agradeço por todas discussões técnicas, pela orientação e pelas cervejas que bebemos juntos. Ao Edson, cevejeiro de mão cheia, muito obrigado por todas conversas sobre os caminhos da vida e pelas risadas. Obrigado também pelas oportunidades e por tua amizade.

Aos meus amigos do GAPH e do GSE, muito obrigado pelo tempo que passamos juntos e pelos bons momentos. Obrigado em especial ao Sérgio, que tornou-se um grande

amigo, pelos cafés no bar para esquecer um pouco as questões de trabalho e pelas discussões sobre arquitetura e organização de computadores. Te agradeço por sempre tirares todas minhas dúvidas sobre o projeto de sistemas embarcados e por acreditares em mim para formarmos uma equipe de projeto. O chip funcionou! Agradeço também ao Amory, por todas as conversas, técnicas e não técnicas, e pelas cervejas no Cuca Haus. Obrigado pelas oportunidades de colaboração, aprendi muito trabalhando contigo. Ao Moratelli, que me introduziu ao hobby de projetar drones, obrigado pelos momentos divertidos colocando os brinquedos no ar. Obrigado também por todas as substituições na PUCRS. Outro amigo especial é o Felipe, que sempre esteve ao meu lado nos bons e maus momentos. Nossa amizade começou na graduação e seguiu durante nossos cursos de mestrado e doutorado. Muito obrigado por tudo, alemão. Obrigado ao Wachter, ao Madala, ao Castilhos e ao Ruaro pelas partidas de tênis e pelas risadas. Obrigado também aos meus amigos que passaram pelo GAPH e pelo GSE durante esses anos, em especial ao Jerônimo, ao Vini, ao Gnomo, ao Raupp e ao Yan.

Agradeço também ao grupo de async do GAPH por todas discussões produtivas que tivemos e por todos que apoiaram meu trabalho ou desenvolveram pesquisa em conjunto. Aos Hecks pelos trabalhos que desenvolvemos juntos e pelos bons momentos que vivemos dentro e fora do laboratório. Valeu Guilherme pelos churrascos em Los Angeles. Valeu Leandro por todos momentos de descontração e pelo trabalho com o chip, sem tua placa não conseguiríamos validar o projeto. Ao Bruno, valeu pelo apoio ao desenvolvimento do meu trabalho de TCC e de mestrado e pelo bom humor diário. Ao Gibiluka e ao Guazzelli, obrigado por todas as discussões que tivemos e pelo apoio que vocês deram ao desenvolvimento do meu trabalho. Ao Michel e ao Baiano, valeu por todo o apoio com o fluxo e pelo projeto de todos os layouts que vocês fizeram. Ao Walter, ao Jurinha e ao Bortolon, obrigado pelos cafés e pelas risadas. Obrigado ao Kuentzer por sempre me explicar os conceitos de teste e pelas partidas de tênis. Agradeço também aos alunos de Engenharia de Computação que me auxiliaram no desenvolvimento dos trabalhos práticos: Gelmar, Porto, Giovane e Trojan. Agradeço, também, a todos os meus alunos na FACIN. Mesmo sem saber, vocês foram fonte de inspiração em diversos momentos.

Agradeço à FACIN e à PUCRS por todas as oportunidades e pelo apoio que recebi. Sou muito grato pela confiança depositada em mim e, em particular, pela oportunidade de trabalhar com o que eu amo. Agradeço também o apoio financeiro que me foi dado para participar de conferências. Obrigado em especial ao Dotti e ao Bernardo. Agradeço também ao apoio da CAPES, CNPq, FAPERGS e HP, que financiaram parcialmente minha trajetória acadêmica. Em especial, agradeço pelo financiamento do meu estágio sanduíche, que me trouxe um grande desenvolvimento profissional e pessoal. Agradeço também à UNISC e o pessoal de lá, em especial ao Leonel e ao Fred. Leonel, muito obrigado por sempre acreditar em mim e por todo apoio.

Agradeço ao pessoal da UFRGS que trabalhou comigo durante esse curso de doutorado. Obrigado ao Reis e ao Adriel pelo suporte com o ASTRAN. Nossa parceria foi – e está sendo – extremamente produtiva. Ao Ribas e ao André, e seus alunos Mayler e Augusto, meu muito obrigado pelo apoio com o trabalho em síntese NCL. Obrigado por todas as discussões técnicas, em especial ao Ribas. Agradeço também ao pessoal da UFPEL pela recente parceria em trabalhos de projeto de layout. Em especial, obrigado Leomar, Felipe e Smaniotto pelas oportunidades de trabalharmos juntos.

I can't find the words to say how grateful I am to Peter, who became my co-advisor in this work. Thanks for all the technical discussions we had and thanks for the guidance in my research with asynchronous circuits. More importantly, thank you for receiving me in your house and treating me like family. Your support was crucial in my stay in the United States. Thanks for always being so supportive, for all the mentorship and for all the doors you opened in my life. I also thank Janet and the girls for all the fun times we had in Encino. Thanks also go to my friends at USC who received me with open arms. Special thanks to Fei and Dylan, who became good friends. Thank you for all the good times in LA! I also thank my colleagues and friends in the async lab, Ajay, Yang and Ramy, for the technical discussions and fun times.

Finally, thank's to IEEE and its societies, specially Computer Society and Circuits and Systems Society, for the awards and the student grants that helped me attending conferences.

# CIRCUITOS ASSÍNCRONOS: INOVAÇÕES EM COMPONENTES, BIBLIOTECAS DE CÉLULAS E TEMPLATES DE PROJETO

#### **RESUMO**

O paradigma síncrono foi, por décadas, a principal escolha da indústria para o projeto de circuitos integrados. Infelizmente, com o desenvolvimento da indústria de semicondutores, restrições de projeto relativas à potência de um circuito e incertezas de atrasos aumentaram, dificultando o projeto síncrono. Alguns dos motivos para isso são o aumento na variabilidade dos processos de fabricação de dispositivo, as perdas de desempenho relativas em fios e as incertezas temporais causadas por variabilidades nas condições operacionais de dispositivos. Dessa forma, o paradigma assíncrono surge como uma alternativa, devido à sua robustez contra variações temporais e suporte ao projeto de circuitos de alto desepenho e baixo consumo. Entretanto, grande parte da indústria de ferramentas de automação de projeto eletrônico foi desenvolvida visando o projeto de circuitos síncronos e atualmente o suporte a circuitos assíncronos é consideravelmente limitado. Esta Tese propõe novas técnicas de projeto para otimizar circuitos assíncronos, desde o nível de células ao nível de sistema. Começamos analisando e otimizando componentes básicos para o projeto desses circuitos e depois apresentamos novas soluções para implementá-los no nível de transistores. As otimizações propostas permitem uma melhor exploração dos parâmetros desses circuitos, incluindo potência, atraso e área. Em um segundo momento, exploramos o uso desses componentes como células para a geração de uma biblioteca de suporte ao projeto semi-dedicado de circuitos assíncronos. Nesse contexto, propomos um fluxo completamente automatizado para projetar tais bibliotecas. O fluxo compreende ferramentas de dimensionamento de transistores e caracterização elétrica, desenvolvidas nesta Tese, e uma ferramenta de projeto de leiaute, desenvolvida por um grupo de pesquisa parceiro. Esse trabalho também apresenta uma biblioteca aberta, com centenas de componentes validados extensivamente através de simulações pós-leiaute. Além disso, usando essa biblioteca desenvolvemos novos *templates* para o projeto de circuitos assíncronos no nível de sistema, propondo um fluxo automático para síntese e mapeamento tecnológico. Comparado a uma solução assíncrona no estado da arte, nosso mais novo *template* apresenta uma eficiência energética quase duas vezes maior. As contribuições desta Tese permitiram a construção de uma infraestrutura para o projeto de circuitos assíncronos, abrindo caminho para a exploração do uso de templates assíncronos para solucionar problemas modernos e futuros no projeto de circuitos integrados.

**Palavras-Chave:** Projeto de components assíncronos, projeto de bibliotecas de células, templates para o projeto de circuitos assíncronos, quasi-delay-insisitive, semi-custom.

# ASYNCHRONOUS CIRCUITS: INNOVATIONS IN COMPONENTS, CELL LIBRARIES AND DESIGN TEMPLATES

#### **ABSTRACT**

For decades now, the synchronous paradigm has been the major choice of the industry for building integrated circuits. Unfortunately, with the development of semiconductor industry, power budgets got tighter and delay uncertainties increased, making synchronous design a complex task. Some of the reasons behind that are the increase in process variability, the losses in wire performance and the uncertainties in the operating condition of devices. These and other factors significantly impact transistor electrical characteristics, making it more complicated to meet timing closure in synchronous systems and compromising power efficiency. The asynchronous paradigm emerges as an efficient alternative to current design approaches, given its inherent high robustness against delay variations and suitability to low-power and high-performance design. However, while a major segment of the design automation industry was developed to support synchronous design, currently, design automation for asynchronous circuits is limited, to say the least. Furthermore, basic components for semi-custom design approaches, typically available in standard cell libraries were optimized to target synchronous implementations and those necessary to support asynchronous design were also left behind. This Thesis proposes new techniques to optimize asynchronous design, from cell to system level. We start by analyzing and optimizing basic components for asynchronous design and then propose new manners of implementing them at the transistor level. The proposed optimizations and novel components allow better exploring power, delay and area trade-offs, providing a guideline for asynchronous designers. We then explore how to design these components as cells for building a library to support semi-custom design. To that extent, we propose a completely automated flow for designing such libraries. This flow comprises transistors sizing and electrical characterization tools, developed in this Thesis, and a layout generation tool, developed by a fellow research group. We also provide a

freely available library, designed with the flow, with hundreds of components that were extensively validated with post-layout simulations. Using this library we devised new templates for designing asynchronous circuits at the system level, exploring an automated synthesis solution and expanding design space exploration. Compared to a similar state-of-the-art solution, our latest template provides almost twice better energy efficiency and comprises an original automated method for technology mapping and synthesis optimizations. The contributions of this Thesis allowed the construction of an infrastructure for building asynchronous designs, paving the way to explore their usage to solve contemporary and future challenges in integrated circuit design.

**Keywords:** Asynchronous components design, cell library design, asynchronous circuits design templates, quasi-delay-insensitive, semi-custom.

### **LIST OF FIGURES**

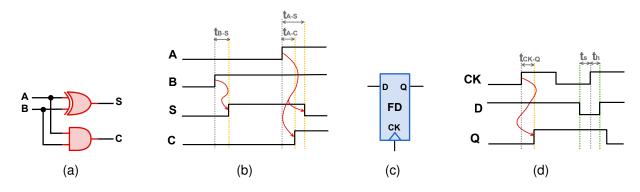

| Figure   | <ul> <li>1.1 - Combinational and sequential circuits: (a) Schematic of a combinational half adder circuit; (b) example waveform for circuit (a) operation;</li> <li>(c) Basic symbol of a flip-flop; (d) example waveform showing the flip-flop</li> </ul>                                                             |    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          |                                                                                                                                                                                                                                                                                                                        | 30 |

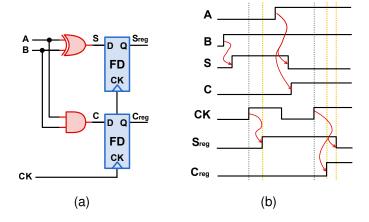

| Figure   | 1.2 – Example sequential logic block: (a) circuit schematic and (b) waveform depicting its behavior                                                                                                                                                                                                                    | 31 |

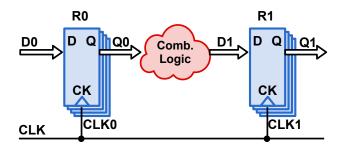

| Figure   | 1.3 - Example of a typical segment of a synchronous datapath                                                                                                                                                                                                                                                           | 33 |

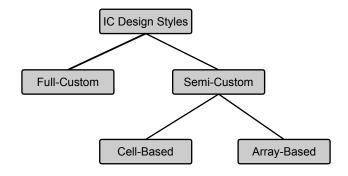

| Figure   | 2.1 – A taxonomy for IC design styles, adapted from [RCN03]                                                                                                                                                                                                                                                            | 41 |

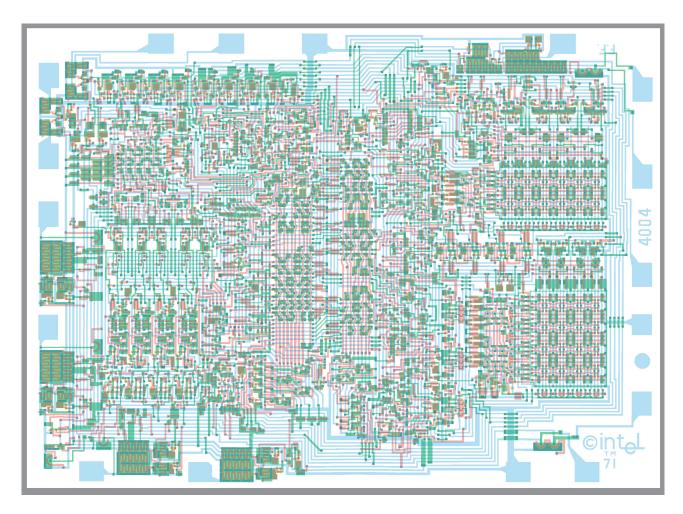

| Figure   | 2.2 - Layout of the Intel 4004 microprocessor [Int]                                                                                                                                                                                                                                                                    | 42 |

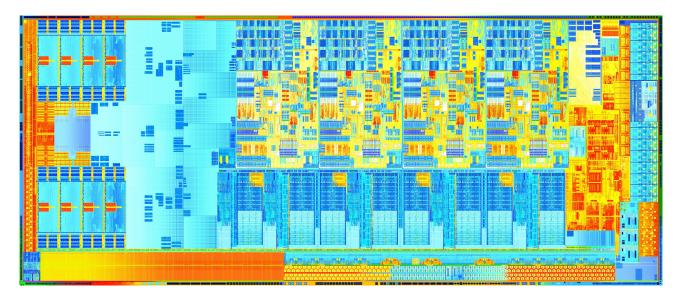

| Figure   | 2.3 - Layout of the Intel Ivy Bridge 3C [Int]                                                                                                                                                                                                                                                                          | 43 |

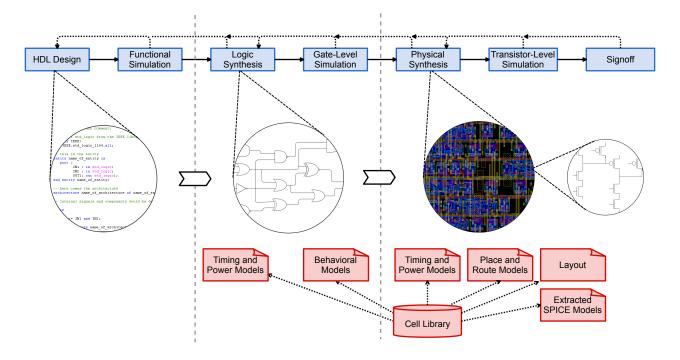

| Figure   | 2.4 - Basic cell-based IC design flow                                                                                                                                                                                                                                                                                  | 45 |

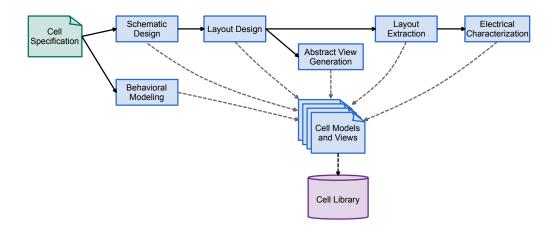

| Figure   | 2.5 – Basic design flow for the design of a cell                                                                                                                                                                                                                                                                       | 52 |

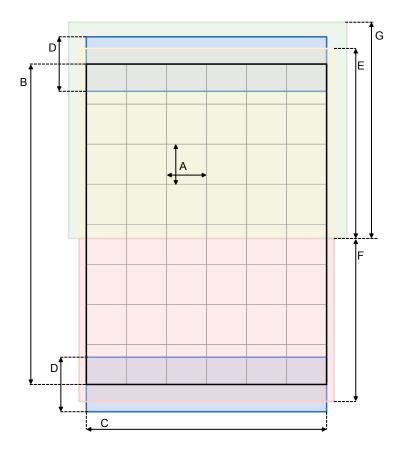

| Figure   | 2.6 – Typical architectural rules for a cell from a standard-cell library, adapted from [Mor10]. "A" is the cell pitch (or routing grid pitch), "B" is the cell height, "C" is the cell width (which can vary), "D" is the power rails width and "E", "F" and "G" are the height of implant layers [RCN03, SS02, SS04] | 53 |

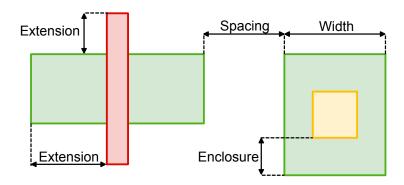

| Figure   | 2.7 – The basic set of DRC rule classes [RCN03, SS02, SS04]                                                                                                                                                                                                                                                            | 54 |

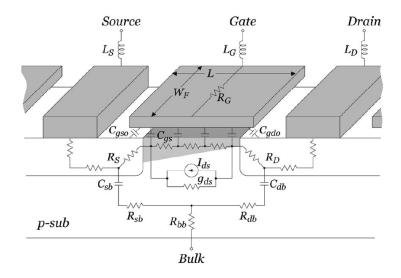

| _        | 2.8 – Physical model of a planar bulk NMOS transistor, extracted from                                                                                                                                                                                                                                                  | 0. |

| i igai o | [DENB05]                                                                                                                                                                                                                                                                                                               | 55 |

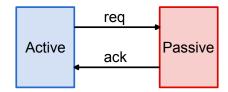

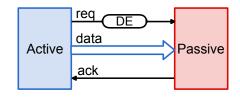

| Figure   | 2.9 – Example of pure control communication through handshaking                                                                                                                                                                                                                                                        | 57 |

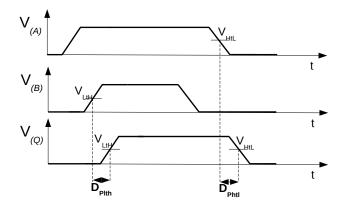

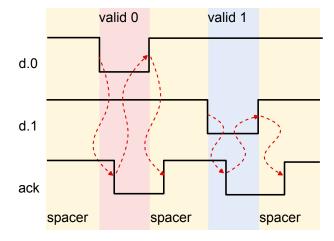

| Figure   | 2.10 – Operation of handshake protocols: (a) 4-phase and (b) 2-phase                                                                                                                                                                                                                                                   | 57 |

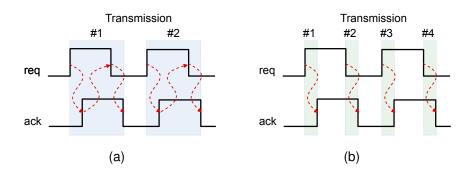

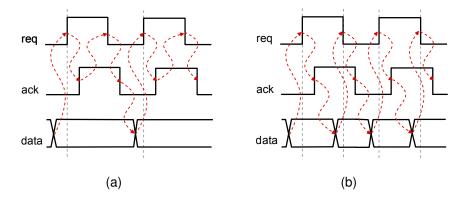

| Figure   | 2.11 – Example of a BD channel                                                                                                                                                                                                                                                                                         | 58 |

| Figure   | 2.12 – Example of (a) 4-phase and (b) 2-phase bundled-data communication.                                                                                                                                                                                                                                              | 58 |

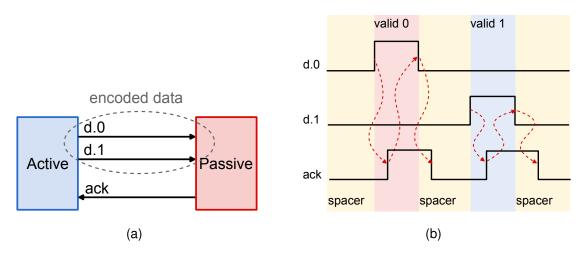

| Figure   | 2.13 – Example of 4-phase 1-of-2 RTZ DI channel for 1 bit: (a) block diagram of two communicating elements and (b) example waveform for the                                                                                                                                                                            |    |

|          |                                                                                                                                                                                                                                                                                                                        | 61 |

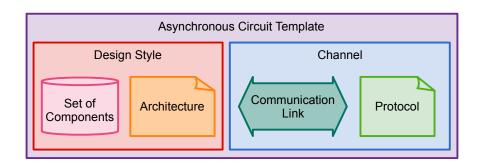

|          | 2.14 – Asynchronous circuits template definition                                                                                                                                                                                                                                                                       | 62 |

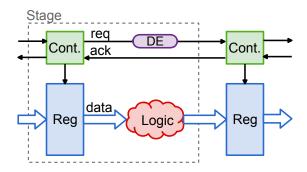

| _        | 2.15 – Generic example of circuit architecture for BD templates                                                                                                                                                                                                                                                        | 63 |

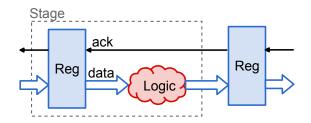

| _        | 2.16 – Generic example of circuit architecture for QDI templates                                                                                                                                                                                                                                                       | 64 |

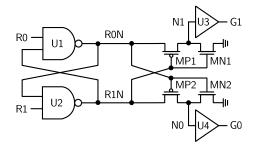

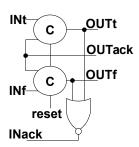

| Figure   | 3.1 – General scheme for a simple MUTEX. It is composed by two cross-coupled NANDs and a metastability filter (MF), [ZHM+15]                                                                                                                                                                                           | 67 |

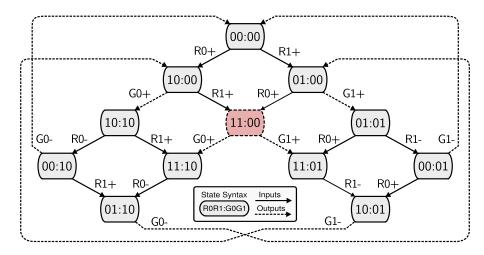

| Figure   | 3.2 - State diagram of a MUTEX, using the state order R0R1:G0G1. Solid lines correspond to primary input transitions, while dotted lines stand for                                                                                                                                                                     |    |

|          | primary output transitions [ZHM+15]                                                                                                                                                                                                                                                                                    | 68 |

| Figure 3.3 - Basic 2-input C-element state diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

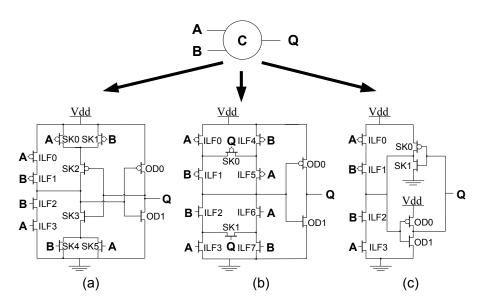

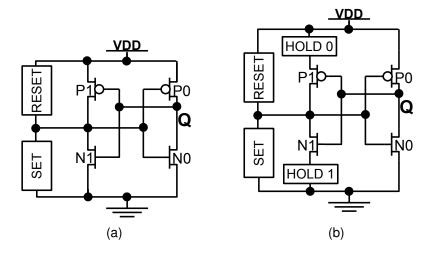

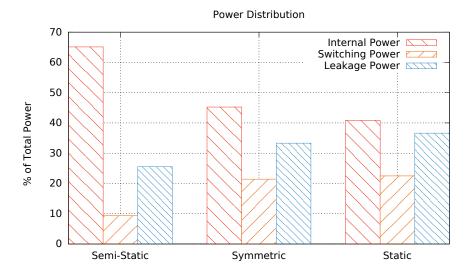

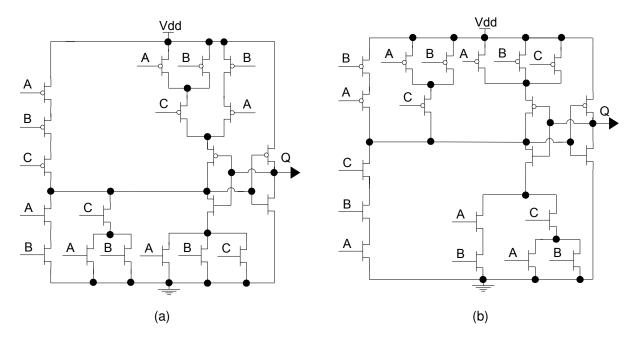

| Figure 3.4 – Three classic implementations of the C-element: (a) static (Sutherland), (b) symmetric (van Berkel), (c) semi-static (Martin). Adapted from [MOMC12].                                                                                                                                                                                                                                                                                                                                                                       | 70       |

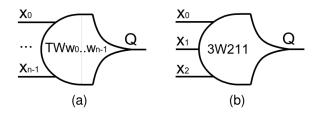

| Figure 3.5 – Symbology for NCL gates: (a) generic NCL symbol; (b) symbol of an example NCL gate with 3 inputs, threshold T=3, and weights w0=2, w1=1 and w2=1. Note that the implicit ordering of inputs in the symbol is from top to bottom, associated with the list of weights from left to right                                                                                                                                                                                                                                     | 72       |

| Figure 3.6 – NCL topologies: (a) semi-static and (b) static. Adapted from [MAGC14].                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

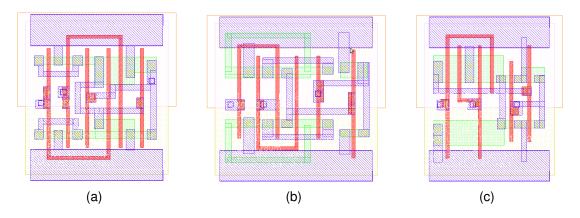

| Figure 3.7 – Example physical layout at the cell level of the designed C-elements:                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

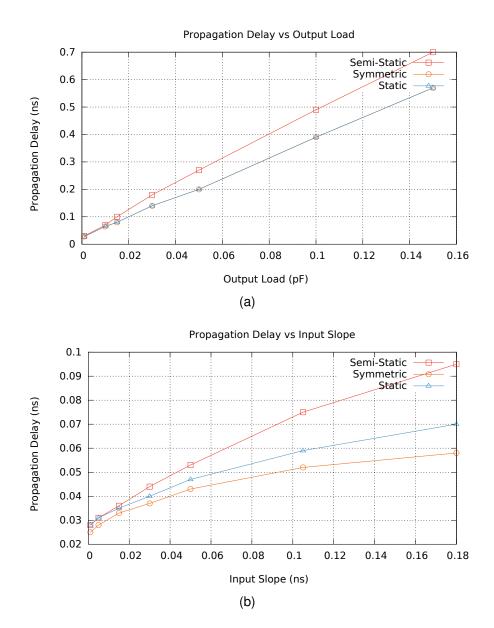

| <ul> <li>(a) static, (b) symmetric, (c) semi-static. Adapted from [MOMC12].</li> <li>Figure 3.8 — Propagation delay of the designed C-elements after electrical extraction, as a function of the (a) output load capacitance and (b) input slope. In (a), results were obtained by fixing the input slope in 1.2 ps and varying the output load from 0.001 pF to 0.15 pF. In (b), results were obtained by fixing the output load in 1 fF and varying the input slope load from 0.0012 ns to 0.180 ns. Adapted from [MOMC12].</li> </ul> | 75<br>77 |

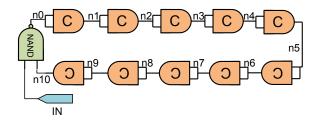

| Figure 3.9 – Oscillator ring employed for an initial comparison of the impact of each C-element implementation in an asynchronous circuit. Adapted from [MOMC12]                                                                                                                                                                                                                                                                                                                                                                         | 78       |

| Figure 3.10 – C-elements power consumption for each asynchronous RSA crypto-<br>graphic core implementation. Adapted from [MOMC12]                                                                                                                                                                                                                                                                                                                                                                                                       | 81       |

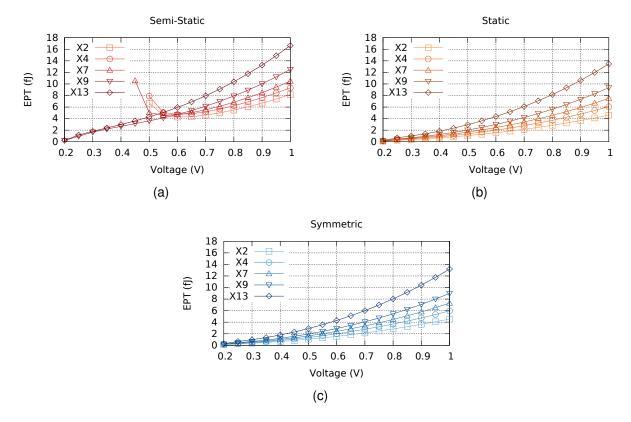

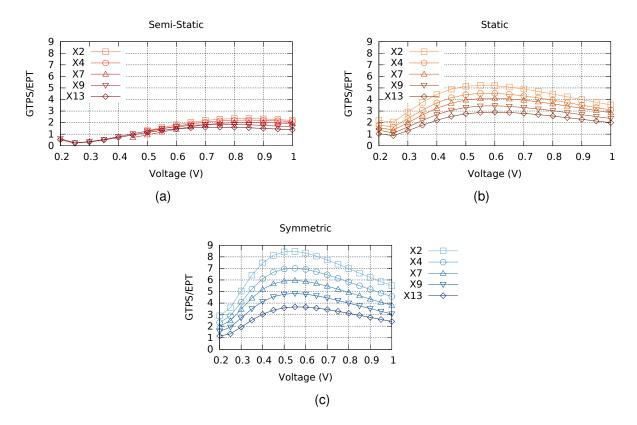

| Figure 3.11 – Average EPT for varying voltage supplies for each drive of the three C-elements: (a) semi-static, (b) static and (c) symmetric. Adapted from [MC13]                                                                                                                                                                                                                                                                                                                                                                        | 84       |

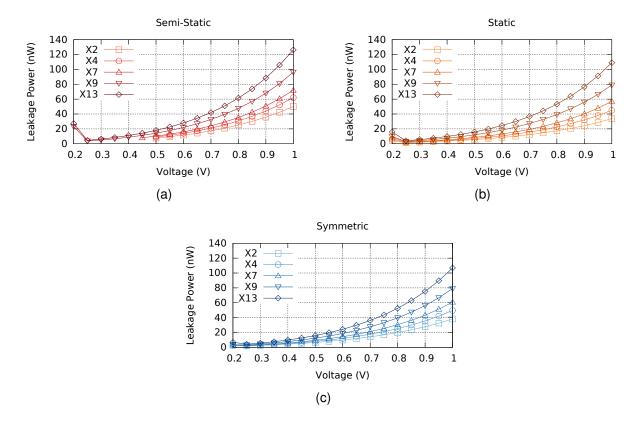

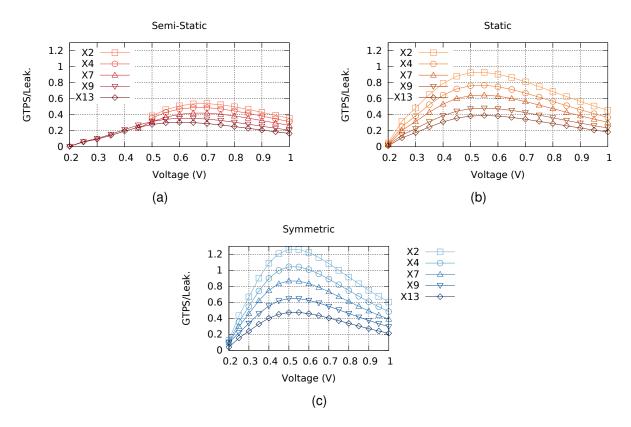

| Figure 3.12 – Average leakage power for varying voltage supplies for each drive of the three C-elements: (a) semi-static, (b) static and (c) symmetric. Adapted from [MC13]                                                                                                                                                                                                                                                                                                                                                              | 85       |

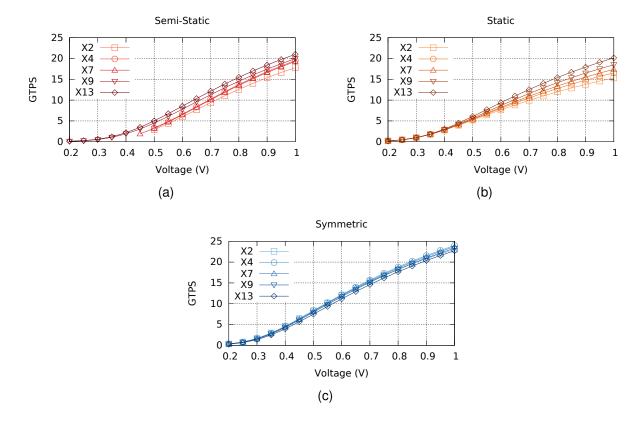

| Figure 3.13 – Average GTPS for varying voltage supplies for each drive of the three C-elements: (a) semi-static, (b) static and (c) symmetric. Adapted from [MC13]                                                                                                                                                                                                                                                                                                                                                                       | 86       |

| Figure 3.14 – Speed-energy efficiency for varying voltage supplies for each drive of the three C-elements: (a) semi-static, (b) static and (c) symmetric. Adapted from [MC13]                                                                                                                                                                                                                                                                                                                                                            | 87       |

| Figure 3.15 – Speed-leakage efficiency for varying voltage supplies for each drive of the three C-elements: (a) semi-static, (b) static and (c) symmetric. Adapted                                                                                                                                                                                                                                                                                                                                                                       | 00       |

| from [MC13]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 88<br>88 |

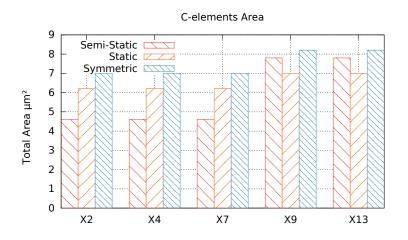

| Figure 3.16 – C-elements area for each drive. Adapted from [MC13]                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00       |

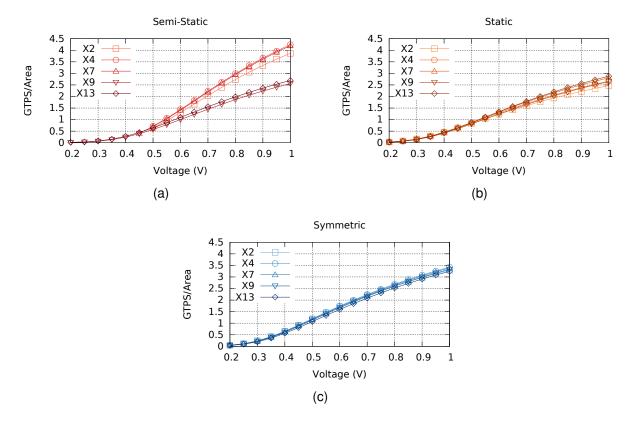

| Figure | 3.17 – Speed-area efficiency for varying voltage supplies for each drive of the three C-elements: (a) semi-static, (b) static and (c) symmetric. Adapted from [MC13]                                                                                                                                                                                                  | 89  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

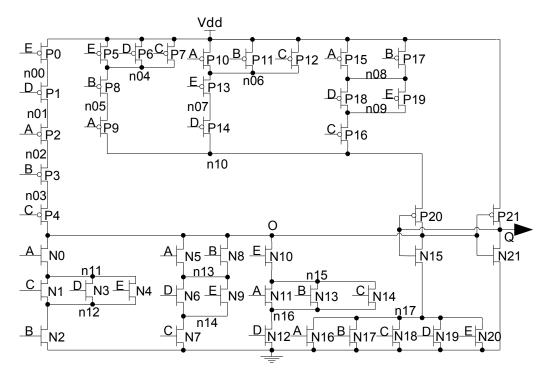

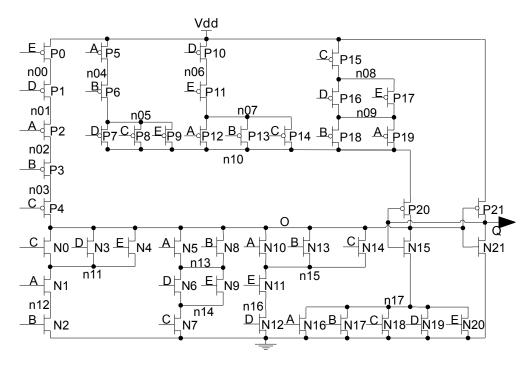

| Figure | 3.18 – A0 CMOS schematic for the 3-of-5 example NCL gate. Adapted from                                                                                                                                                                                                                                                                                                | 91  |

| Figure | 3.19 – A1 CMOS schematic for the 3-of-5 example NCL gate. Adapted from [MOMC13]                                                                                                                                                                                                                                                                                       | 93  |

| Figure | 3.20 - A2 CMOS schematic for the 3-of-5 example NCL gate. Adapted from [MOMC13]                                                                                                                                                                                                                                                                                       | 94  |

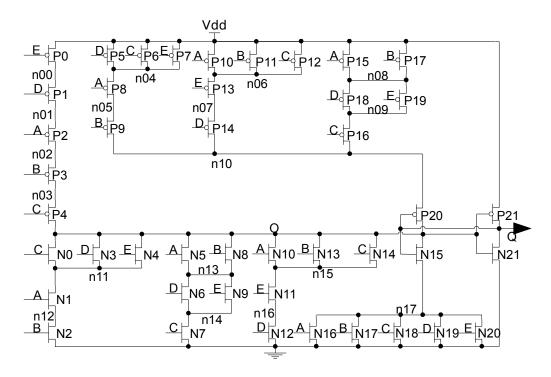

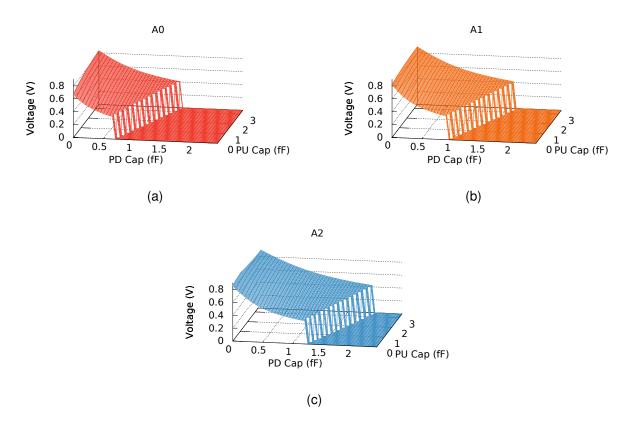

| Figure | 3.21 – Maximum negative peak values (in Volts) of glitches caused in node <i>O</i> due to charge sharing effects for (a) A0 , (b) A1 and (c) A2. Adapted from                                                                                                                                                                                                         | 95  |

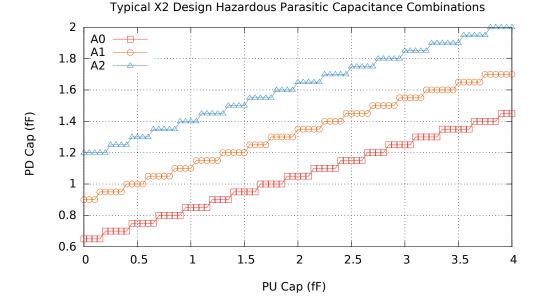

| Figure | 3.22 - Critical PU and PD Cap for the X2 drive cells for a typical process                                                                                                                                                                                                                                                                                            | 96  |

| Figure | 3.23 - Critical PU and PD Cap for the X18 drive cells for a typical process                                                                                                                                                                                                                                                                                           | 97  |

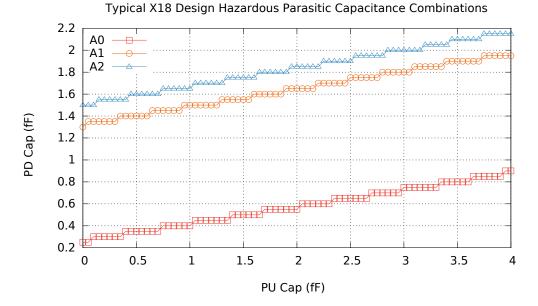

| Figure | 3.24 – Critical PU and PD Cap for the X18 drive for a slow PMOS and fast NMOS process and typical operating conditions. Adapted from [MOMC13]                                                                                                                                                                                                                         | 98  |

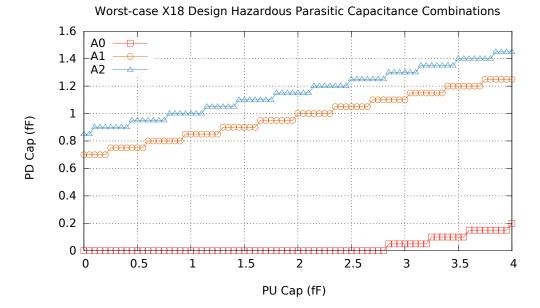

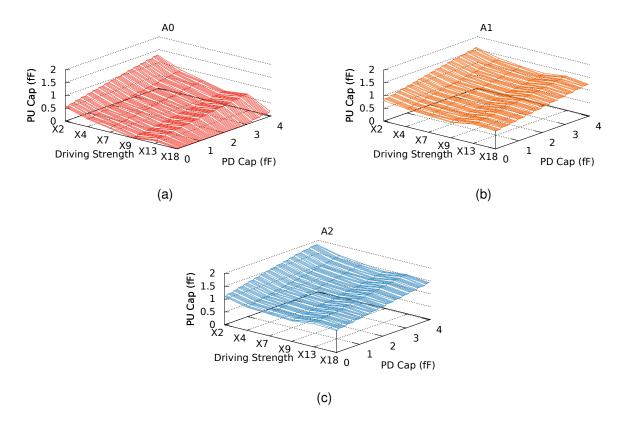

| Figure | 3.25 - Robustness of arrangements (a) A0, (b) A1 and (c) A2. Adapted from [MOMC13]                                                                                                                                                                                                                                                                                    | 99  |

| Figure | 3.26 - Proposed topology for designing NCL gates. Adapted from [MAGC14].1                                                                                                                                                                                                                                                                                             | 100 |

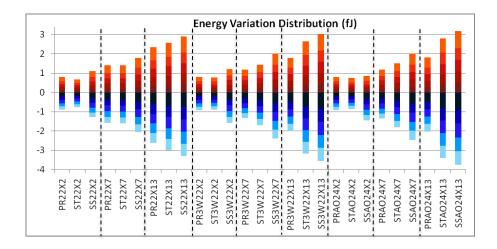

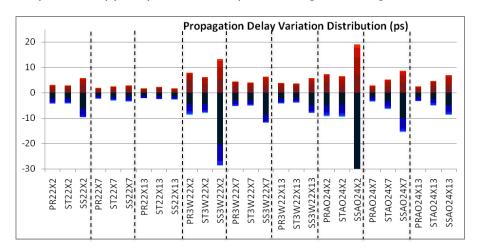

| Figure | 3.27 – Energy variation distribution varying operating voltage and temperature. Data were divided into 10 sets (5 positive and 5 negative). Each color represents a quintile of positive sets (in red) and negative sets (in blue), where darker colors represent lower quintiles and brighter colors represent upper quintiles. Adapted from [MAGC14]                | 104 |

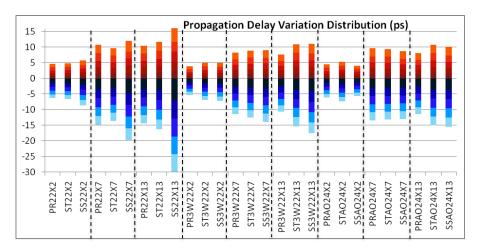

| Figure | 3.28 – Propagation delay variation distribution for varying operating voltage and temperature. Data were divided into 10 sets (5 positive and 5 negative). Each color represents a quintile of positive sets (in red) and negative sets (in blue), where darker colors represent lower quintiles and brighter colors represent upper quintiles. Adapted from [MAGC14] | 104 |

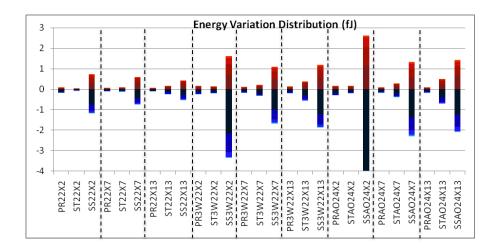

| Figure | 3.29 – Energy variation distribution observed from Monte Carlo analysis.  Data were divided into 10 sets (5 positive and 5 negative). Each color represents a quintile of positive sets (in red) and negative sets (in blue), where darker colors represent lower quintiles and brighter colors represent upper quintiles. Adapted from [MAGC14].                     | 105 |

| Figure | 3.30 – Propagation delay variation distribution observed from Monte Carlo analysis. Data were divided into 10 sets (5 positive and 5 negative). Each |     |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|        | color represents a quintile of positive sets (in red) and negative sets (in                                                                          |     |

|        | blue), where darker colors represent lower quintiles and brighter colors rep-                                                                        |     |

|        | resent upper quintiles. Adapted from [MAGC14]                                                                                                        | 105 |

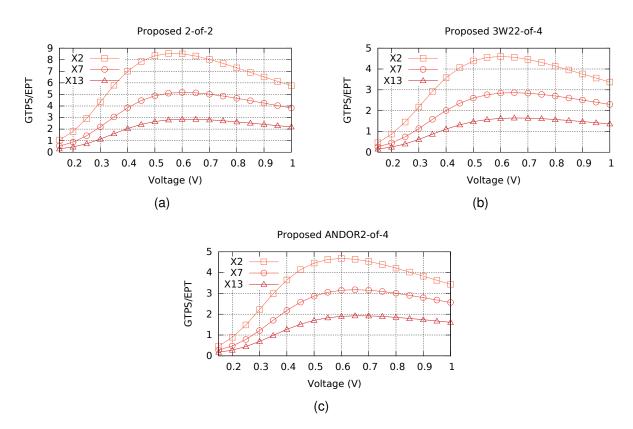

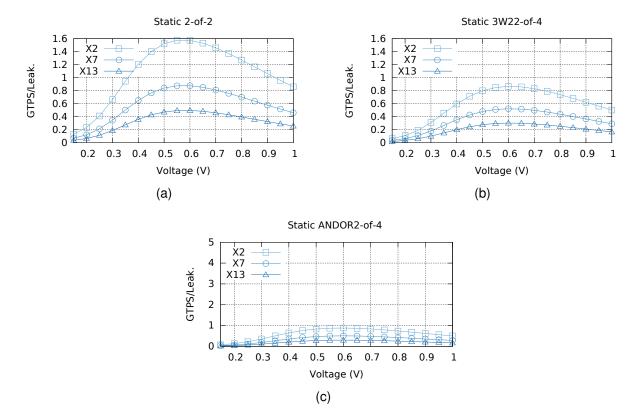

| Figure | 3.31 – Speed-energy efficiency for 2-of-2, 3W22-of-4 and ANDOR2-of-4                                                                                 | .00 |

| riguic | gates using the proposed topology. Adapted from [MAGC14]                                                                                             | 107 |

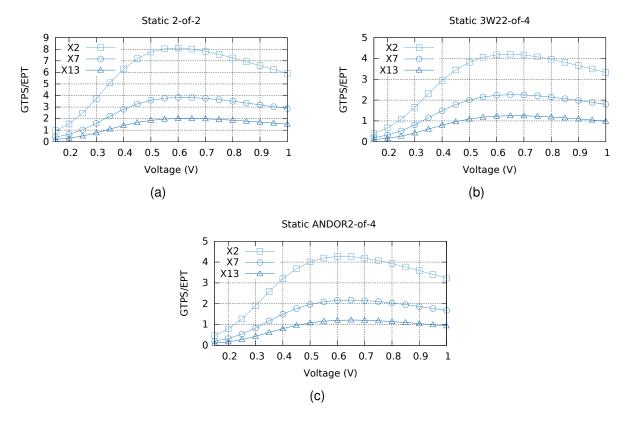

| Figure | 3.32 - Speed-energy efficiency for 2-of-2, 3W22-of-4 and ANDOR2-of-4                                                                                 |     |

| 9      | gates using the static topology. Adapted from [MAGC14]                                                                                               | 108 |

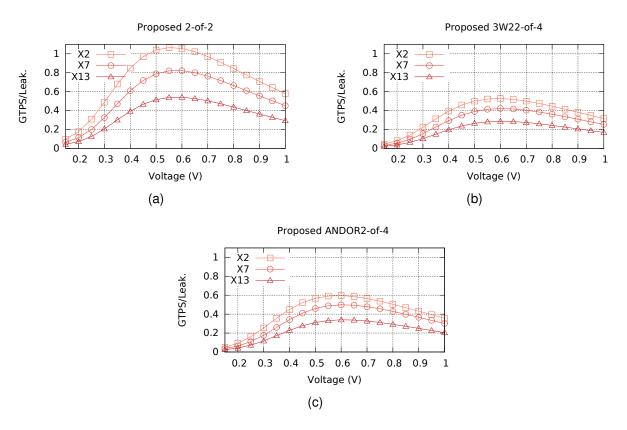

| Figure | 3.33 - Speed-leakage efficiency for 2-of-2, 3W22-of-4 and ANDOR2-of-4                                                                                |     |

| Ü      | gates using the proposed topology. Adapted from [MAGC14]                                                                                             | 108 |

| Figure | 3.34 - Speed-leakage efficiency for 2-of-2, 3W22-of-4 and ANDOR2-of-4                                                                                |     |

| _      | gates using the static topology. Adapted from [MAGC14]                                                                                               | 109 |

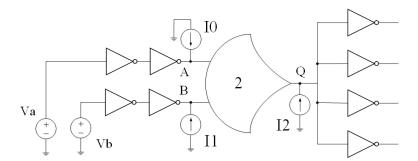

| Figure | 3.35 - Example of simulation environment for evaluating SEEs in a 2-of-2                                                                             |     |

|        | NCL gate. Adapted from [MAGC14]                                                                                                                      | 109 |

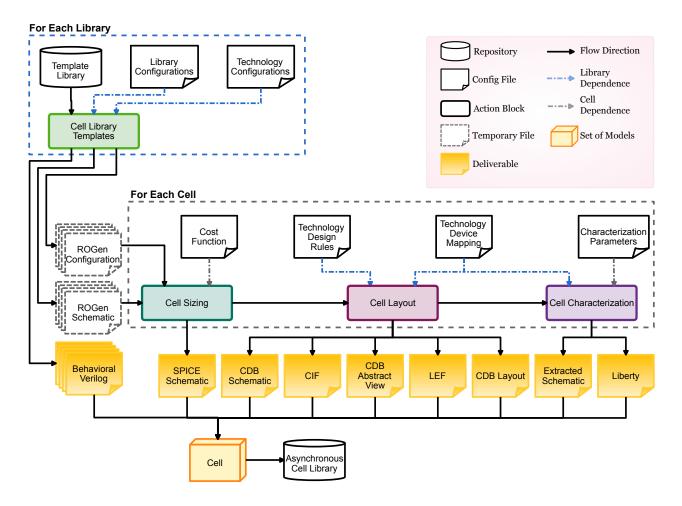

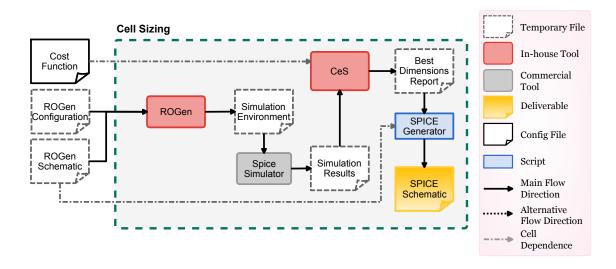

| Figure | 4.1 - Overview of the ASCEnD-A flow                                                                                                                  | 120 |

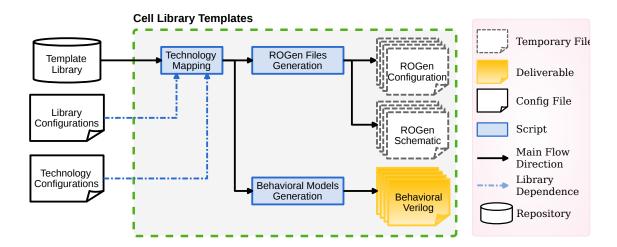

| Figure | 4.2 - Details of the Cell Library Templates action block, responsible for the                                                                        |     |

|        | process of library template generation in the ASCEnD-A flow                                                                                          | 122 |

| Figure | 4.3 - Details of the Cell Sizing action block of the ASCEnD-A flow                                                                                   | 124 |

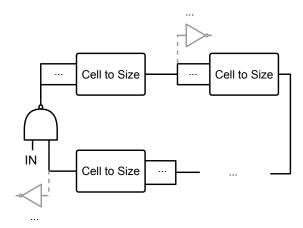

| Figure | 4.4 - Controlled ring oscillator produced by ROGen to perform transistor                                                                             |     |

|        | sizing simulations                                                                                                                                   | 124 |

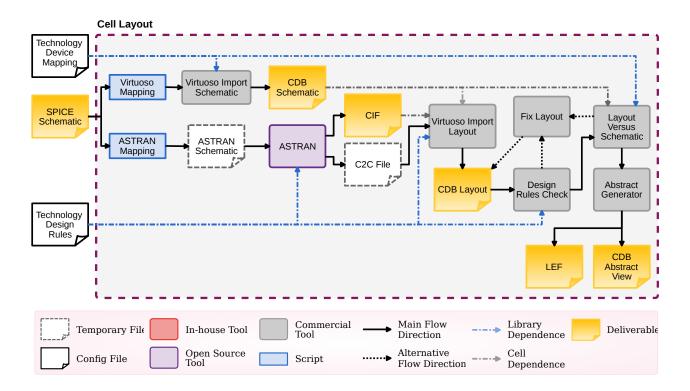

| Figure | 4.5 - Details of the Cell Layout action block, used for layout generation in                                                                         |     |

|        | the ASCEnD-A flow                                                                                                                                    | 128 |

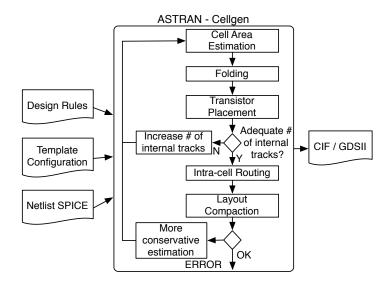

| Figure | 4.6 - The cell generation flow employed by ASTRAN [ZRM+14b]                                                                                          | 128 |

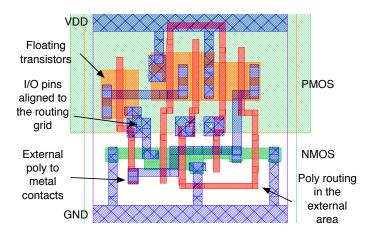

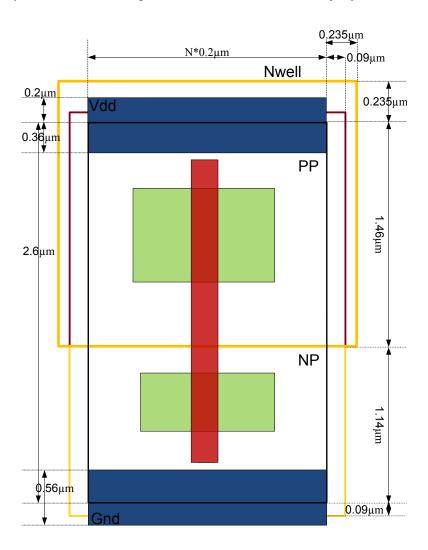

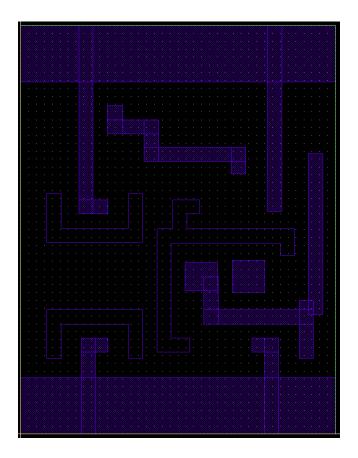

| Figure | 4.7 - ASTRAN layout style [MAZ+14b]                                                                                                                  | 129 |

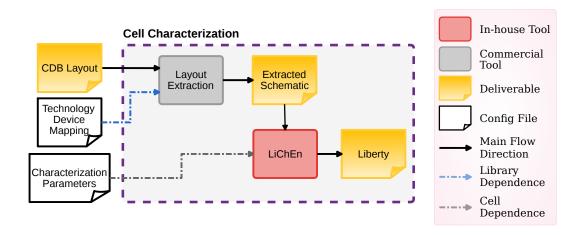

| Figure | 4.8 - Details of the Cell Characterization action block, required for the                                                                            |     |

|        | characterization tasks in the ASCEnD-A flow                                                                                                          | 130 |

| Figure | 4.9 - Example of interaction during a tentative characterization of a spe-                                                                           |     |

|        | cific C-element using the Cadence ELC tool [MOCO13]                                                                                                  |     |

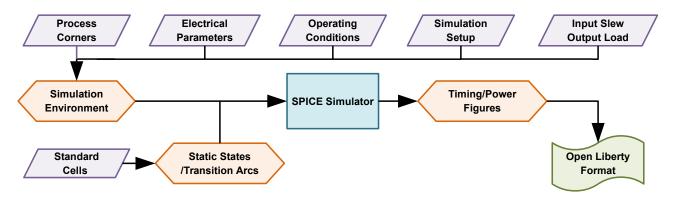

| Figure | 4.10 – The LiChEn electrical characterization flow [MOCO13]                                                                                          | 132 |

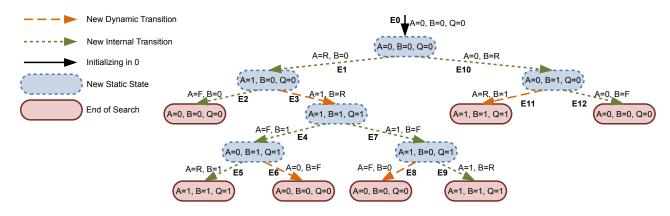

| Figure | 4.11 - Computation of transition arcs and static states of a two input C-                                                                            |     |

|        | element. "R" stands for low-to-high transitions (rise) and "F" for high-to-low                                                                       |     |

|        | transitions (fall). Graph edges are labeled numerically as En, according to                                                                          | 104 |

| Cie    | the order in which they occur during the transition arcs search [MOCO13]                                                                             |     |

|        | 4.12 – Example of propagation delays for a 2-input C-element [MOCO13]                                                                                |     |

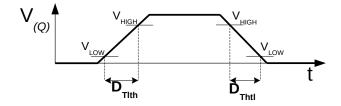

| ⊢ıgure | 4.13 – Transition delays example for an output pin Q [MOCO13]                                                                                        | 13/ |

| Figure | 4.14 – Standard layout architecture. The red polygon is polysilicon and the green rectangles are diffusion. NP and Nwell are the negative doping layers and PP is the positive doping layer. Adapted from [Mor10]                                                                | 122 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

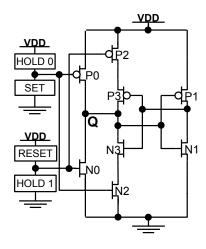

| Figure | 5.1 – Schematic of a 1-of-2 4-phase QDI 1-bit WCHB                                                                                                                                                                                                                               |     |

| _      | •                                                                                                                                                                                                                                                                                | 140 |

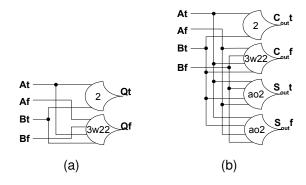

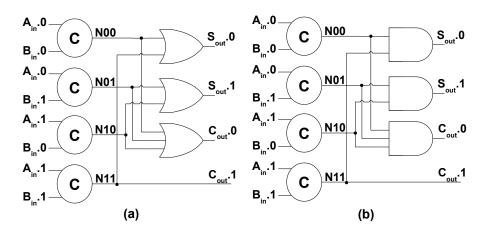

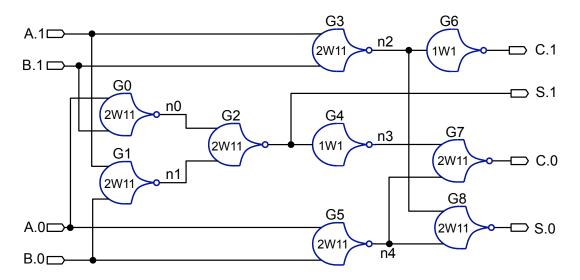

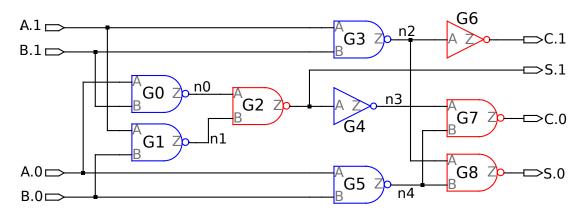

| rigure | 5.2 – Example 1-of-2 DIMS-based blocks: (a) a one-bit half adder; and (b) a one-bit full adder                                                                                                                                                                                   | 144 |

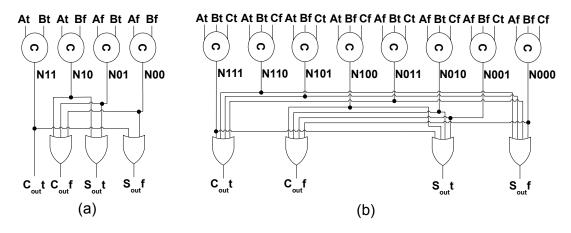

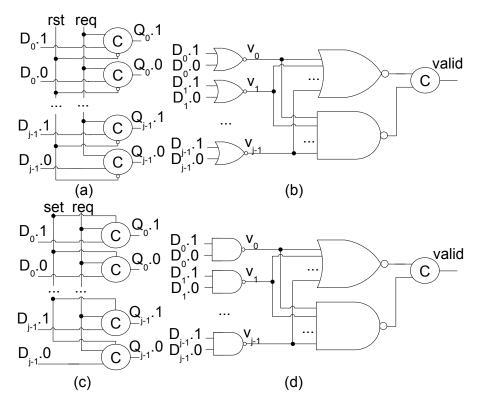

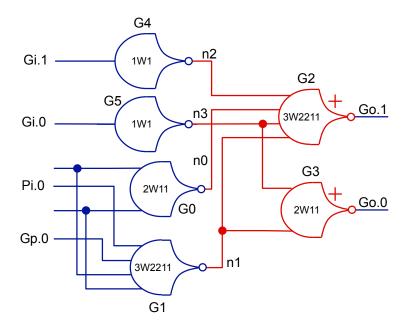

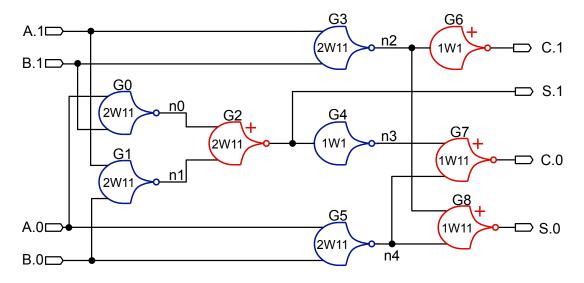

| Figure | 5.3 - Examples of 1-of-2 4-phase QDI circuits built with NCL gates: (a) 2-input AND gate; (b) half adder combinational block                                                                                                                                                     | 145 |

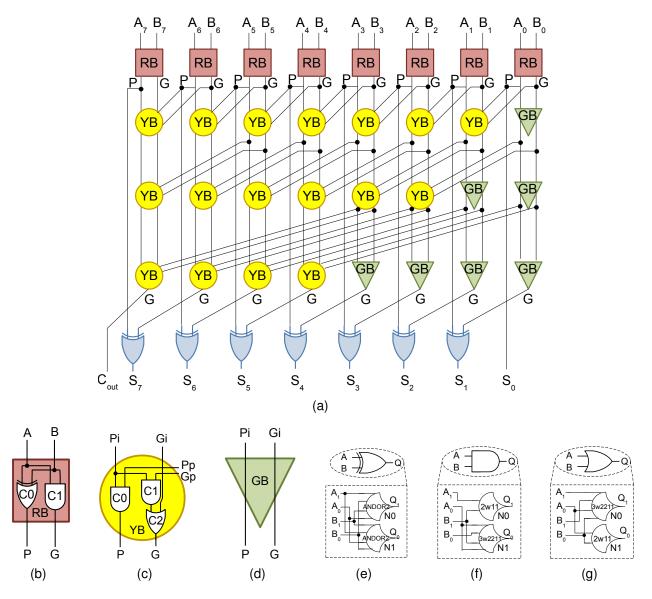

| Figure | 5.4 – Details of the Kogge-Stone adder design: (a) block diagram (b, c, d) red (RB), yellow (YB) and green (GB) boxes internal structure; (e, f, g) NCL implementation of 2-input XOR, AND and OR gates. Adapted from [MTMC14].                                                  | 147 |

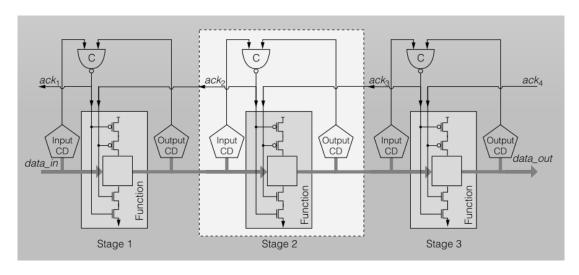

| Figure | 5.5 – Architecture of the PCHB template, adapted from [NS11]. CDs are completion detection blocks.                                                                                                                                                                               |     |

| Figure | 5.6 – Example of a waveform for the transmission of two 1-bit values in a 4-phase 1-of-2 RTZ DI channel                                                                                                                                                                          |     |

| Figure | 5.7 – WCHB latch and validity detector implementations: (a) RTZ buffer using resettable, active-low C-elements (lower input); (b) RTZ validity detector; (c) RTO latch using settable, active-high C-elements (upper input); and (d) RTO validity detector. Adapted from [MPC14] | 154 |

| Figure | 5.8 - DIMS/DIMxS implementation of (a) RTZ and (b) RTO half-adders. Adapted from [MPC14]                                                                                                                                                                                         |     |

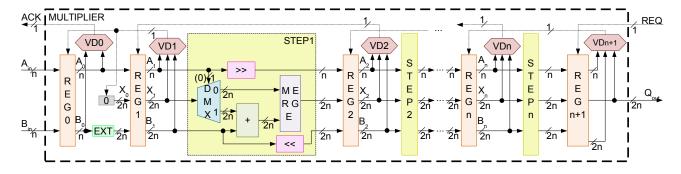

| Figure | 5.9 – Block diagram of the case study pipelined multiplier. Dotted lines are single wire control signals and full lines are 1-of-2 encoded data channels. Adapted from [MPC14]                                                                                                   | 158 |

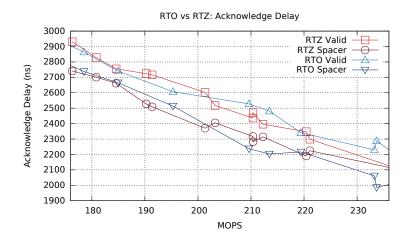

| Figure | 5.10 – Acknowledge delay of valid data and spacer for RTO and RTZ. Adapted from [MPC14]                                                                                                                                                                                          |     |

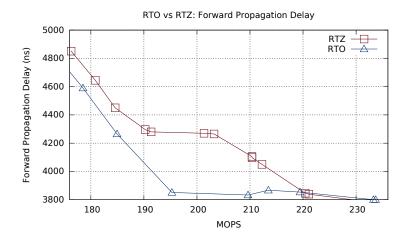

| Figure | 5.11 — Forward propagation delay results for the simulated designs. Adapted from [MPC14]                                                                                                                                                                                         | 160 |

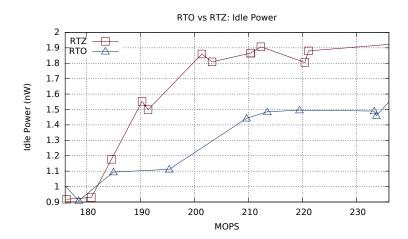

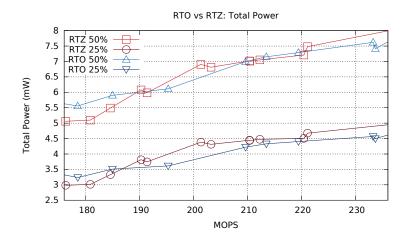

| Figure | 5.12 – Total power of the designs while at reset/set and idle states. Adapted from [MPC14]                                                                                                                                                                                       | 160 |

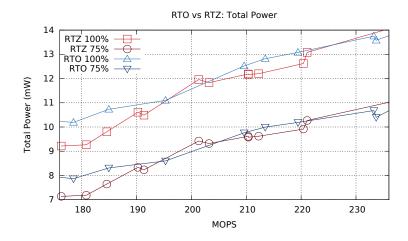

| Figure | 5.13 – Total power of the RTO and RTZ designs when computing 100% and 75% of the time. Adapted from [MPC14]                                                                                                                                                                      | 161 |

| Figure | 5.14 – Total power of the RTO and RTZ designs when computing 50% and 25% of the time. Adapted from [MPC14]                                                                                                                                                                       | 161 |

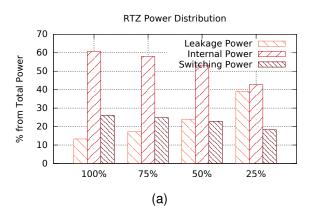

| Figure | 5.15 – Average power distribution of designs: (a) RTZ and (b) RTO. Adapted from [MPC14]                                                                                                                                                                                          | 162 |

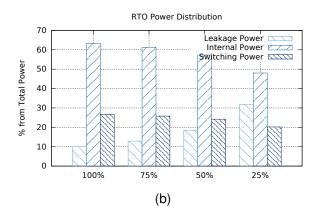

| Figure | 5.16 – Power distribution in the multiplier components for a scenario where the circuit is computing 100% of the time. VD stands for validity detector. Adapted from [MPC14]                                                                                                                                                                 | 163 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

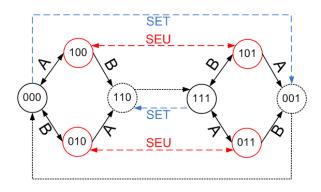

| Figure | 5.17 – State transition graph (ABQ) of a C-element considering SET and SEU effects [PCV12]. Full-line nodes are static states. Dotted-line nodes are transition (unstable) states. Dashed lines are transitions that generate SETs or SEUs in the output. Dotted lines are transitions from unstable to stable states. Adapted from [MGHC14] |     |

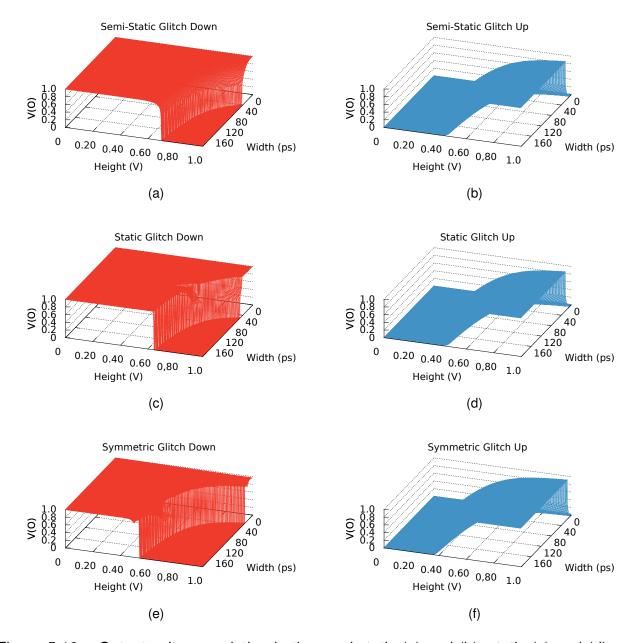

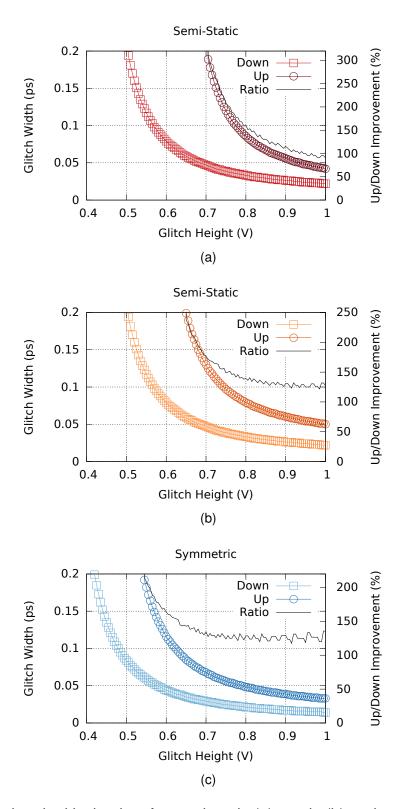

| Figure | 5.18 – Output voltage variation in the semi-static (a) and (b), static (c) and (d) and symmetric (e) and (f) topologies. Glitch Up stands for 010 and 100 scenarios and Glitch Down stands for 011 and 101 scenarios, where the worst case result was collected. Adapted from [MPC14]                                                        | 167 |

| Figure | 5.19 – Isolated critical points for semi-static (a), static (b) and symmetric (c) topologies. Adapted from [MPC14]                                                                                                                                                                                                                           | 169 |

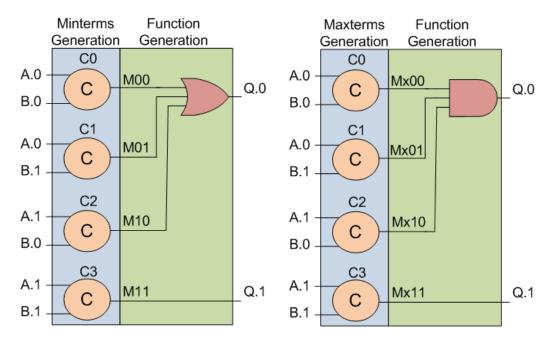

| Figure | 5.20 – Schematics for 2-input, 1-of-2 AND in DIMS and DIMxS. Adapted from [MGHC14]                                                                                                                                                                                                                                                           | 170 |

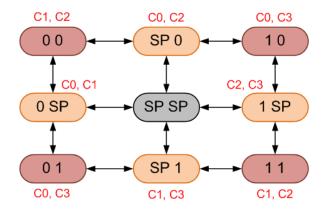

| Figure | 5.21 – Transition diagram for 2-input DIMS and DIMxS AND blocks. Inputs are assumed to use the 1-of-2 code. SP stands for spacer. Adapted from [MGHC14]                                                                                                                                                                                      | 171 |

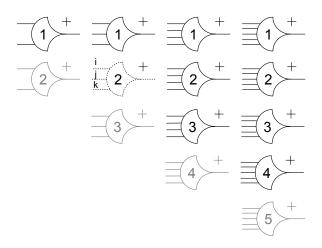

| Figure | 5.22 – A basic set of 14 NCL+ gates. Adapted from [MOPC13b]                                                                                                                                                                                                                                                                                  |     |

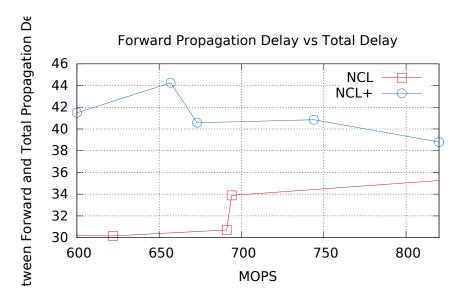

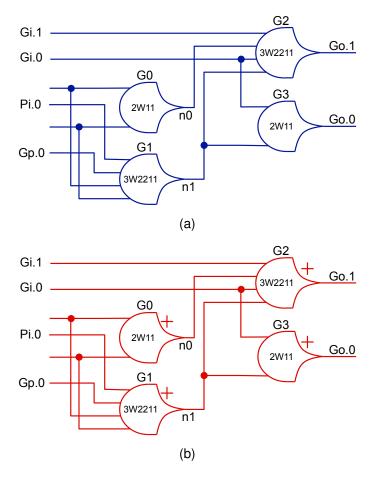

| Figure | 5.23 – Example transistor topologies for NCL and NCL+ gates (2-of-3 gates): (a) topology for the 3-input T=2 NCL gate; (b) an NCL+ gate with the same number of inputs and threshold. Adapted from [MOPC13b]                                                                                                                                 | 173 |

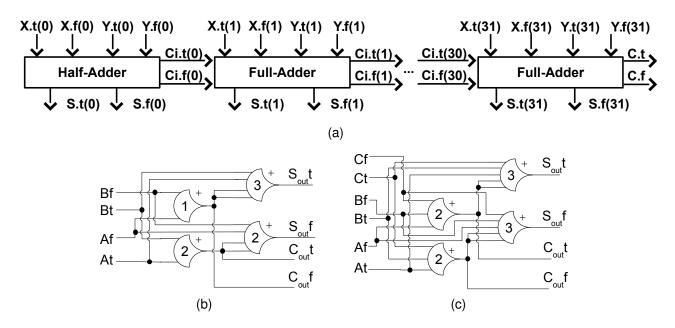

| Figure | 5.24 – A 32-bit ripple carry adder: (a) the block diagram; gate level schematics of the NCL+ (b) half adder and (c) full adder. Adapted from [MOPC13b].                                                                                                                                                                                      | 174 |

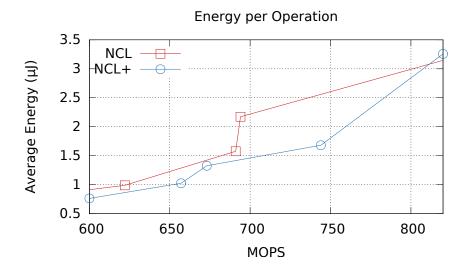

| Figure | 5.25 – Energy per operation for the NCL and NCL+ adders. Adapted from [MOPC13b]                                                                                                                                                                                                                                                              | 176 |

| Figure | 5.26 – Idle power for the NCL and NCL+ adders. Adapted from [MOPC13b].                                                                                                                                                                                                                                                                       | 176 |

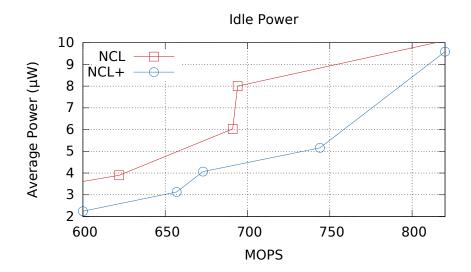

| Figure | 5.27 – Percentage of the total delay represented by forward propagation delay for the NCL and NCL+ adders. Adapted from [MOPC13b]                                                                                                                                                                                                            | 177 |

| Figure | 5.28 – NCI and NCL+ example implementations of the generate path of block YB from the Kogge0Stone adder of Figure 5.4: (a) NCL implementation; (b) NCL+ implementation. Adapted from [MTMC14]                                                                                                                                                | 178 |

| Figure | 5.29 – Example of an SDDS-NCL implementation of the generate path for the YB yellow box of a Kogge-Stone adder. Adapted from [MTMC14]                                                                                                                                                                                                        | 180 |

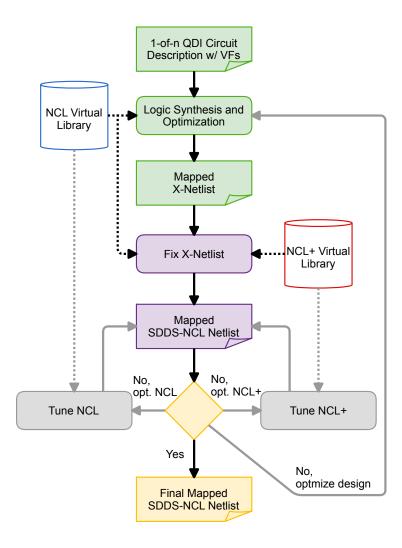

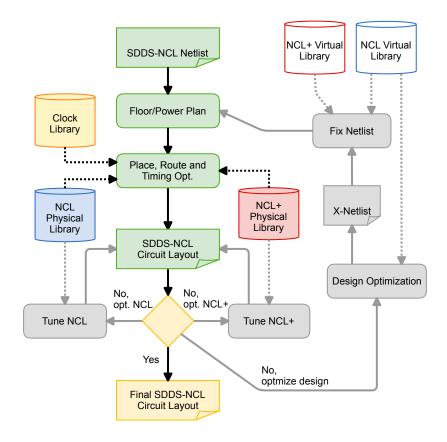

| Figure | 5.30 – Design flow for technology mapping and logic optimization of 1-of-n QDI circuits using SDDS-NCL                                                                                                                                                                                                                                       | 182 |

| Figure | 5.31 – Example Verilog description of a dual-rail half-adder using only VFs.     | 183 |

|--------|----------------------------------------------------------------------------------|-----|

| Figure | 5.32 - X-Netlist resultant from the synthesis of the circuit described in Fig-   |     |

|        | ure 5.31                                                                         | 184 |

| Figure | 5.33 - VF representation of an X-Netlist resultant of the synthesis of the       |     |

|        | circuit described in Figure 5.31                                                 | 184 |

| Figure | 5.34 - Algorithm for fixing an X-Netlist                                         | 185 |

| Figure | 5.35 - Mapped SDDS-NCL Netlist equivalent to Figure 5.33                         | 186 |

| Figure | 5.36 - Design flow for physical synthesis of 1-of-n QDI circuits using SDDS-     |     |

|        | NCL                                                                              | 188 |

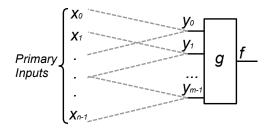

| Figure | 5.37 – Example combinational logic circuit that implements $f(x_0, x_1,, x_n) =$ |     |

|        | $g(y_0, y_1,, y_m)$                                                              | 192 |

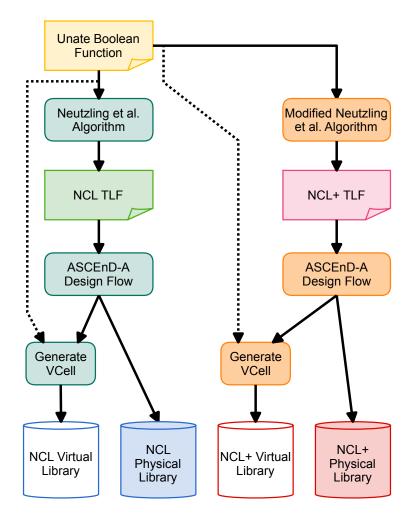

| -igure | 5.38 – Design flow for generating virtual libraries                              | 194 |

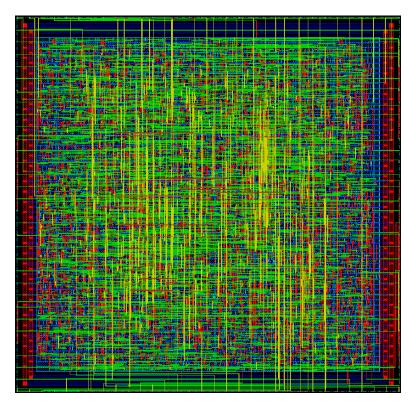

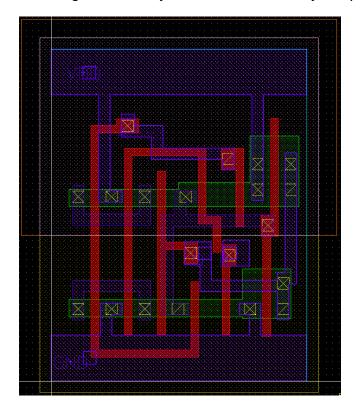

| Figure | 5.39 - Layout of a case study 16-bit multiplier designed using the proposed      |     |

|        | SDDS-NCL flow                                                                    | 204 |

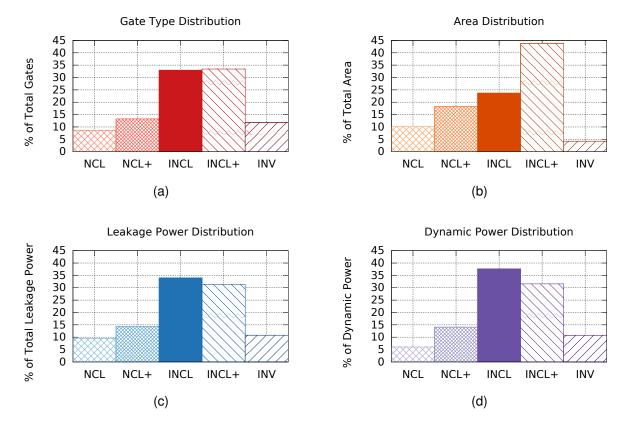

| Figure | 5.40 - Distribution of (a) gate count, (b) area, (c) leakage power, and (d)      |     |

|        | dynamic power among different gate types in the fast SDDS-NCL version            |     |

|        | of the synthesized 16-bit multiplier. Gate types considered here are NCL,        |     |

|        | NCL+, INCL, INCL+ and INV (inverters)                                            | 206 |

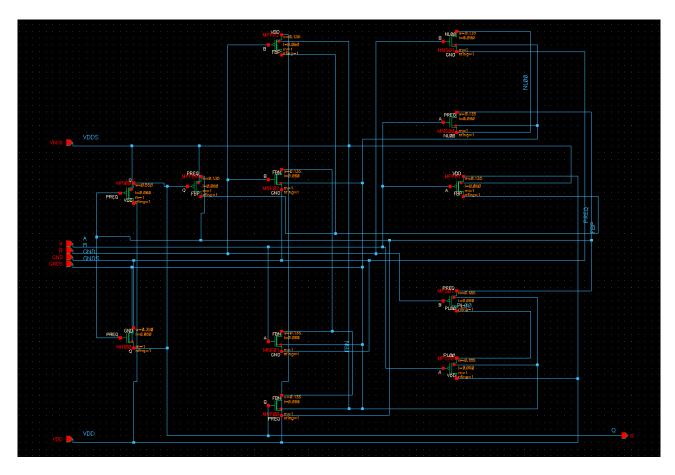

| igure  | A.1 - Schematic of the case study 2-input C-element imported to CDB              | 247 |

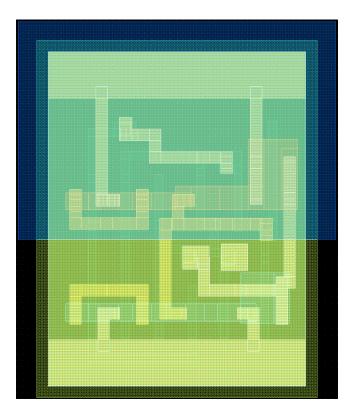

| ⁻igure | A.2 $-$ CIF of the generated layout for the case study 2-input C-element         | 249 |

| igure  | A.3 - Imported layout of the generated layout for the case study 2-input         |     |

|        | C-element                                                                        | 249 |

| -igure | A.4 - Generated abstract view for the case study 2-input C-element               | 250 |

| Figure | A.5 - Extraction report for the case study 2-input C-element                     | 252 |

## **LIST OF TABLES**

| Table 2.1 — 4-phase 1-of-2 RTZ encoding for one data bit                                                                                                                        | 61   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 3.1 - Basic 2-input C-element truth table                                                                                                                                 | 69   |

| Table 3.2 — Truth table of an example NCL gate with 3 inputs with threshold 3 and weights 2, 1 and 1. Note that <i>i</i> denotes the current instant of time                    | 72   |

| Table 3.3 – Area, parasitic capacitance, input capacitance and average dynamic                                                                                                  |      |

| and leakage power of the C-element implementations. Adapted from [MOMC12]                                                                                                       | . 76 |

| Table 3.4 — Performance figures of the oscillator rings. Adapted from [MOMC12] 7                                                                                                | 78   |

| Table 3.5 — Area and power results for the three asynchronous RSA cryptographic core implementations after place and route. Adapted from [MOMC12] 8                             | 30   |

| Table 3.6 – Minimum voltage for maintaining correct functionality of the semi-static C-element for different driving strengths at varying temperatures .  Adapted from [MC13]   | 32   |

| Table 3.7 – Minimum voltage for maintaining correct functionality of the static C-element for different driving strengths at varying temperatures . Adapted from [MC13]         | 32   |

| Table 3.8 — Minimum voltage for maintaining correct functionality of the symmetric  C-element for different driving strengths at varying temperatures . Adapted from [MC13]     | 32   |

| Table 3.9 — Input sequence for observing charge sharing effects in a 3-of-5 gate.  Adapted from [MOMC13]                                                                        | 92   |

| Table 3.10 – Area, input and parasitic capacitances, speed-energy and speed-leakage tradeoffs for the 2-of-2 case study gates. Adapted from [MAGC14]. 10                        | 01   |

| Table 3.11 – Area, input and parasitic capacitances, speed-energy and speed-leakage tradeoffs for the 3W22-of-4 case study gates. Adapted from [MAGC14].                        | 101  |

| Table 3.12 – Area, input and parasitic capacitances, speed-energy and speed-leakage tradeoffs for the AO2-of-4 case study gates. Adapted from [MAGC14].10                       | 01   |

| Table 3.13 – Observed minimum operating voltage for different versions of the 2-of-2 case study. Darker case values are worse than light case values. Adapted from [MAGC14]     | 06   |

| Table 3.14 – Observed minimum operating voltage for different versions of the 3W22-of-4 case study. Darker case values are worse than light case values.  Adapted from [MAGC14] | 06   |

| Table 3.15 – Observed minimum operating voltage for different versions of the AO2-of-4 case study. Darker case values are worse than light case values. Adapted from [MAGC14] | 107 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.16 – Input (I.) and output (O.) critical charge for the 2-of-2 case study gates.  Adapted from [MAGC14]                                                               |     |

| Table 3.17 – Input (I.) and output (O.) critical charge for the 3W22-of-4 case study                                                                                          |     |

| gates. Adapted from [MAGC14]                                                                                                                                                  | 110 |

| Table 3.18 – Input (I.) and output (O.) critical charge for the AO2-of4 case study gates. Adapted from [MAGC14].                                                              | 110 |

| Table 4.1 – Resulting SSs, DTAs and ITAs after the complete search for the logic function of a 2-input C-element. Logical values assume the order A, B, Q                     | 104 |

| for inputs/outputs [MOCO13]                                                                                                                                                   | 134 |

| Table 5.1 – Static power consumption in C-elements when inputs are at the same                                                                                                | 151 |

| logical level. Adapted from [MGC12b]                                                                                                                                          |     |

| Table 5.2 — 4-phase 1-of-2 RTO encoding for one data bit                                                                                                                      |     |

| Table 5.3 — Truth table for an RTZ 1-of-2 half-adder. Adapted from [MPC14]                                                                                                    |     |

| Table 5.4 — Truth table for an RTO 1-of-2 half-adder. Adapted from [MPC14]                                                                                                    | 15/ |

| Table 5.5 — States of the C-elements for a 2-input DIMS AND. Inputs are assumed to be dual-rail and SP stands for spacer. Adapted from [MGHC14]                               | 171 |

| Table 5.6 – States of the C-elements for a 2-input DIMxS AND. Inputs are assumed to be dual-rail and SP stands for spacer. Adapted from [MGHC14]                              | 172 |

| Table 5.7 — Simulation results for NCL adder. Adapted from [MOPC13b]                                                                                                          | 175 |

| Table 5.8 - Simulation results for NCL+ adder. Adapted from [MOPC13b]                                                                                                         | 175 |

| Table 5.9 - Input weights and threshold relationship to Q=A(B+C) [MNM+14]                                                                                                     | 195 |

| Table 5.10 - Greater and smaller sets of inequalities from Table 5.9                                                                                                          | 196 |

| Table 5.11 – Generated inequalities from Table 5.10 [MNM+14]                                                                                                                  | 196 |

| Table 5.12 – Equivalent NCL and NCL+ gates for VF Q=A(B+C). Adapted from [MNM+14].                                                                                            | 197 |

| Table 5.13 – NCL+ greater and smaller sets of inequalities from Table 5.9 [MNM+14].                                                                                           |     |

| Table 5.14 - Equivalent NCL and NCL+ gates for a NAND VF. Adapted from [MNM+14                                                                                                |     |

| Table 5.15 – Positive unate VFs and respective NCL/NCL+ gates                                                                                                                 | _   |

| Table 5.16 – Negative unate VFs and respective INCL/INCL+ gates                                                                                                               |     |

| Table 5.17 – Case studies synthesis, simulation and power analysis results. Adapted                                                                                           |     |

| from [MNM+14]                                                                                                                                                                 | 202 |

| Table 5.18 - Gates count comparison for ISCAS85 benchmarks considering the                                                                                                    |     |

| proposed SDDS-NCL template and design flow and traditional NCL design.                                                                                                        | 203 |

| Table 5.19 - Results for the 16-bit multiplier case study synthesized using an NCL |     |

|------------------------------------------------------------------------------------|-----|

| template-based approach and the proposed design flow                               | 205 |

#### LIST OF ACRONYMS

AFSM – Asynchronous Finite State Machine

ASCEND - Asynchronous Standard Cells Enabling n Designs

ASCEND-A - ASCEND ASTRAN

BABANOC - Balsa-Based Network-on-Chip

BD - Bundled-data

BVF - Boolean Virtual Function

CDB - Cadence Data Base

CALTECH – California Institute of Technology

CES – Cell Specifier

CHP - Communicating Hardware Processes

CIF - Caltech Intermediate Form

CMOS - Complementary Metal-Oxide-Semiconductor

CSP – Communicating Sequential Processes

DE - Delay Element

DFT – Design for Testability

DI – Delay-Insensitive

DIMS – Delay-Insensitive Minterm Synthesis

DIMXS – Delay-Insensitive Maxterm Synthesis

DPC - Dual Polarity Circuit

DRC – Design Rule Check

DTA - Dynamic Transition Arc

DUV – Design Under Verification

EDA – Electronic Design Automation

EPT – Energy per Transition

FDSOI – Fully Depleted Silicon on Insulator

FET – Field Effect Transistor

FO4 - Fanout-of-4

FPGA – Field Programmable Gate Array

GALS - Globally Asynchronous Locally Synchronous

GAPH - Grupo de Apoio ao Projeto de Hardware

GDSII – Graphic Database System II

GTPS - Giga Transitions per Second

HA - Half Adder

HDL – Hardware Description Language

IC – Integrated Circuit

IEEE - Institute of Electrical and Electronics Engineers

INCL - Inverted Null Convention Logic

INCL+ - Inverted Null Convention Logic Plus

IP - Intellectual Property

ITA - Internal Transition Arc

ITRS - International Technology Roadmap for Semiconductors

LEC – Logic Equivalence Checking

LEF - Library Exchange Format

LICHEN - Library Characterization Environment

LKP – Leakage Power

LVS - Layout Versus Schematic

MF – Metastability Filter

MOPS - Millions of Operations per Second

MOS – Metal–Oxide–Semiconductor

MUTEX - Mutual Exclusion Element

MPSOC – Multi-Processor System-on-Chip

NCL – Null Convention Logic

NCL+ – Null Convention Logic Plus

NOC – Network-on-Chip

NRE – Non-Recurring Engineering

NUG - Negative Unate Gate

PCHB - Precharged Half Buffer

PDK - Process Design Kit

PR - Production Rule

PUG - Positive Unate Gate

PVT – Process Voltage and Temperature

QDI - Quasi-delay-insensitive

ROGEN – Ring Oscillator Generator

RPDFT – Robustly Path Delay Fault Testable

RSA - Rivest-Shamir-Adleman

RTL – Register Transfer Level

RTO - Return-to-One

RTZ - Return-to-Zero

SDC – Synopsys Design Constraints

SDDS - Spatially Distributed Dual Spacer

SDF – Standard Delay Format

SEE – Single Event Effect

SET - Single Event Transient

SEU - Single Event Upset

SOC - System-on-Chip

SOI - Silicon on Insulator

SS - Static State

STA – Static Timing Analysis

STFB - Single-Track Full Buffer

TLF – Threshold Logic Function

UDP - User Defined Primitive

USC - University of Southern California

VD – Validity Detector

VF - Virtual Function

VHDL - Very High Speed Integrated Circuits Hardware Description Language

VL – Virtual Library

VLSI – Very Large Scale Integration

WCHB - Weak-Conditioned Half Buffer

## **CONTENTS**

| 1     | INTRODUCTION                                       | 29  |

|-------|----------------------------------------------------|-----|

| 1.1   | PRELIMINARIES                                      | 29  |

| 1.2   | MOTIVATION                                         | 33  |

| 1.3   | PROBLEM DESCRIPTION                                | 36  |

| 1.4   | GOALS                                              | 37  |

| 1.5   | ORIGINALITY OF THIS THESIS                         | 37  |

| 1.6   | DOCUMENT STRUCTURE                                 | 39  |

| 2     | CELL-BASED AND ASYNCHRONOUS CIRCUITS DESIGN        | 40  |

| 2.1   | CELL-BASED DESIGN                                  | 40  |

| 2.1.1 | IC DESIGN STYLES                                   | 40  |

| 2.1.2 | CELL-BASED DESIGN FLOW                             | 43  |

| 2.1.3 | CELL LIBRARY DESIGN                                | 51  |

| 2.2   | ASYNCHRONOUS DESIGN                                | 56  |

| 2.2.1 | CHANNELS AND HANDSHAKE PROTOCOLS                   | 56  |

| 2.2.2 | BUNDLED-DATA CHANNELS                              | 58  |

| 2.2.3 | DELAY-INSENSITIVE CHANNELS                         | 59  |

| 2.2.4 | ASYNCHRONOUS CIRCUITS TEMPLATES                    | 61  |

| 3     | INNOVATIONS IN ASYNCHRONOUS COMPONENTS DESIGN      | 66  |

| 3.1   | STATE-OF-THE-ART IN ASYNCHRONOUS COMPONENTS DESIGN | 66  |

| 3.1.1 | THE MUTUAL EXCLUSION ELEMENT                       | 66  |

| 3.1.2 | THE C-ELEMENT                                      | 68  |

| 3.1.3 | NCL GATES                                          | 71  |

| 3.1.4 | DISCUSSION                                         | 74  |

| 3.2   | C-ELEMENTS DESIGN                                  | 75  |

| 3.2.1 | AREA, POWER AND DELAY TRADE OFFS                   | 75  |

| 3.2.2 | LOW VOLTAGE OPERATION                              | 81  |

| 3.3   | NCL GATES DESIGN                                   | 89  |

| 3.3.1 | CHARGE SHARING AWARE DESIGN                        | 90  |

| 3.3.2 | NEW TOPOLOGY                                       | 98  |

| 3.4   | DISCUSSION                                         | 111 |

| 4     | INNOVATIONS IN ASYNCHRONOUS CELL LIBRARIES DESIGN            | 114 |

|-------|--------------------------------------------------------------|-----|

| 4.1   | STATE-OF-THE-ART IN CELL LIBRARIES FOR ASYNCHRONOUS DESIGN . | 114 |

| 4.1.1 | TIMA ASYNCHRONOUS LIBRARY                                    | 114 |

| 4.1.2 | UNIVERSITY OF UTAH ASYNCHRONOUS CELL LIBRARY                 | 115 |

| 4.1.3 | USC ASYNCHRONOUS CELL LIBRARIES                              | 116 |

| 4.1.4 | CELLTK                                                       | 117 |

| 4.1.5 | CHARACTERIZATION FLOW BY PRAKASH                             | 118 |

| 4.1.6 | DISCUSSION                                                   | 118 |

| 4.2   | THE ASCEND-A FLOW                                            | 119 |

| 4.2.1 | CELL LIBRARY TEMPLATES                                       | 121 |

| 4.2.2 | CELL SIZING                                                  | 123 |

| 4.2.3 | CELL LAYOUT                                                  | 127 |

| 4.2.4 | CELL CHARACTERIZATION                                        | 130 |

| 4.3   | THE ASCEND-ST65 V2 LIBRARY                                   | 137 |

| 4.3.1 | LIBRARY ARCHITECTURE                                         | 137 |

| 4.3.2 | LIBRARY COMPOSITION                                          | 139 |

| 4.3.3 | LIBRARY DISTRIBUTION AND ORGANIZATION                        | 139 |

| 4.4   | DISCUSSION                                                   | 140 |

| 5     | INNOVATIONS IN ASYNCHRONOUS DESIGN TEMPLATES                 | 142 |

| 5.1   | STATE-OF-THE-ART IN QDI TEMPLATES FOR ASYNCHRONOUS DESIGN .  | 142 |

| 5.1.1 | THE DUAL-RAIL RTZ WCHB/DIMS TEMPLATE                         | 142 |

| 5.1.2 | THE NCL TEMPLATE                                             | 145 |

| 5.1.3 | THE PCHB TEMPLATE                                            | 146 |

| 5.1.4 | DISCUSSION                                                   | 149 |

| 5.2   | RETURN-TO-ONE QDI CHANNELS                                   | 151 |

| 5.3   | THE DUAL-RAIL RTO WCHB/DIMXS TEMPLATE                        | 152 |

| 5.3.1 | PROPOSED ARCHITECTURE                                        | 153 |

| 5.3.2 | POWER AND PERFORMANCE TRADE OFFS                             | 157 |

| 5.3.3 | TEMPLATE ROBUSTNESS                                          | 164 |

| 5.4   | THE NCL+ TEMPLATE                                            | 171 |

| 5.4.1 | PROPOSED DESIGN STYLE                                        | 172 |

| 5.4.2 | EXPERIMENTS                                                  | 173 |

| 5.5   | THE SDDS-NCL TEMPLATE                                        | 177 |

| 5.5.1 | PROPOSED ARCHITECTURE                                        | 177 |

| 5.5.2 | PROPOSED DESIGN FLOW                                                         | 180 |

|-------|------------------------------------------------------------------------------|-----|

| 5.5.3 | ANALYSIS OF THE ALGORITHM FOR FIXING <i>X-NETLISTS</i>                       | 189 |

| 5.5.4 | VIRTUAL LIBRARIES DESIGN                                                     | 193 |

| 5.5.5 | EXPERIMENTS                                                                  | 199 |

| 5.6   | DISCUSSION                                                                   | 206 |

| 6     | CONCLUSIONS                                                                  | 210 |

| 6.1   | CONTRIBUTIONS OF THIS WORK                                                   | 210 |

| 6.1.1 | THESIS CONTRIBUTIONS                                                         | 210 |

| 6.1.2 | OTHER CONTRIBUTIONS                                                          | 212 |

| 6.2   | DISCUSSION AND FUTURE WORK                                                   | 214 |

|       | REFERENCES                                                                   | 218 |

|       | APPENDIX A – Example of Usage of the ASCEnD-A Flow                           | 235 |

| A.1   | TEMPLATES GENERATION                                                         | 235 |

| A.2   | CELL SIZING                                                                  | 240 |

| A.3   | CELL LAYOUT                                                                  | 246 |

| A.4   | CELL CHARACTERIZATION                                                        | 252 |

|       | APPENDIX B – List of Cells Currently Available in the ASCEnD-ST65 v2 Library | 264 |

|       |                                                                              |     |

#### 1. INTRODUCTION

Asynchronous circuits have been the research subject of several research groups since the late 1950s, when they were first proposed. However, these circuits never made it to consumer products in a large scale because semiconductors market evolved to well accommodate synchronous design, but not asynchronous. The reason for that is the reduced complexity that the former allowed in early technology nodes. As technologies evolved and transistors shrunk, though, problems that could be easily waived in synchronous design complicated and new design challenges started to emerge. In this new scenario, interest on asynchronous circuits design regained relevance both in academia and industry. The problem is that, because the market evolved to support the synchronous paradigm, design methodologies, tools and intellectual property (IP) blocks also evolved in a specialized way to optimize synchronous design. Hence, a gap currently exists between the levels of automation for asynchronous circuits and for synchronous ones. The work conducted in the context of this Thesis provides a step towards higher levels of design automation and better design space exploration for asynchronous circuits. This chapter explores the motivation, goals and contributions of this Thesis.

#### 1.1 Preliminaries

Digital circuits are widely spread in our society since their take off in the early 1970s. after the invention of the metal-oxide-semiconductor (MOS) transistor [RCN03]. Evolving from mainframe and minicomputers to smartphones, tablets, wearable devices and medical applications, digital circuit-based appliances are a part of our daily lives. Initially, digital integrated circuits (ICs) were all full-custom, i.e. truly handcrafted, where every transistor was manually placed, routed and optimized [RCN03]. However, as silicon technologies evolved, integration capabilities rocketed from thousands to millions, and then to billions, of transistors in a single chip, as predicted by Gordon Moore in the 1960s [Moo65, Moo03]. This was the welcoming the era of very large scale integration (VLSI) design. With this evolution, full-custom approaches proved to be unsustainable and digital designers had to adhere to strategies that were more amenable to automation. As a result, hardware description languages (HDLs) [Vah10] and semi-custom design approaches like the standard-cell methodology were born and quickly spread among VLSI designers [WH10, RCN03, Mic94]. Using HDLs, designers could specify the behavior of a digital circuit in a precise and formal manner using a textual description consisting of expressions, statements and control structures [Vah10]. Moreover, HDLs enabled a technology independent specification flow that allowed reusing code and performing verification steps in the early stages of the design process. The standard-cell methodology provided complementary benefits, as the process